多媒体处理,特别是视频和音频编解码以及数码照相机已经成为手机的常见功能。然而,正当手机对功能需求日益增长的时候,手机生产厂商和OEM设备制造商却面临着不断减少器件数量和降低物料(BOM)成本同时满足严格低功耗要求的压力。他们必须解决这些问题,同时支持在多种网络上运行的各种通信标准。

传统手机芯片组是以DBB(数字基带)芯片为中心,通常包含微控制器(MCU)和数字信号处理器(DSP)。在多媒体功能应用在手机之前,MCU的基本作用是完成以下两个主要功能:一个是运行通信协议物理层的控制码(也称为第1层);另一个是控制通信协议栈的上层软件(第2或第3层),包括表示层或人机界面(MMI)。DSP的基本作用是完成物理层大量的数学计算功能,包括信道均衡、信道编解码以及电话语音编解码。

随着多媒体功能的日益增加,增加手机功能的方法之一是提高DBB中的集成度。新一代基带处理器是一种高度复杂的系统芯片(SoC),它不仅支持几种通信标准,而且提供多媒体功能以及用于多媒体显示器、图像传感器和音频设备相关的接口。 完全可编程的软件定义无线电(SDR)对手机设计工程师来说非常有吸引力。SDR的最终目标是使无线手机能够支持多种手持设备功能(例如,电话、个人数字助理、智能手机和许多其他设备),并且实时改变个性化无线电通信,同时确保服务质量(QoS)。有人认为大范围推广软件无线电所面临的所有因素对于手机都很关键:多功能(相同设备上增加其他服务)、全球移动性、小封装和低功耗、容易生产以及容易升级。

新一代手机对SDR的需求更加明显,要求支持三套不同的标准:无线标准、多媒体标准和连接标准。例如,GSM和GPRS通信模块必须与FDD WCDMA调制解调模块共存在一部多模手机上,手机还也必须能够实现MPEG4视频编解码和MP3编解码,还要支持IEEE 802.11无线局域网和蓝牙标准。AD6900 DBB是一种支持未来SDR多标准和多媒体手机终端的平台,可满足新一代手机对各种功能的要求。

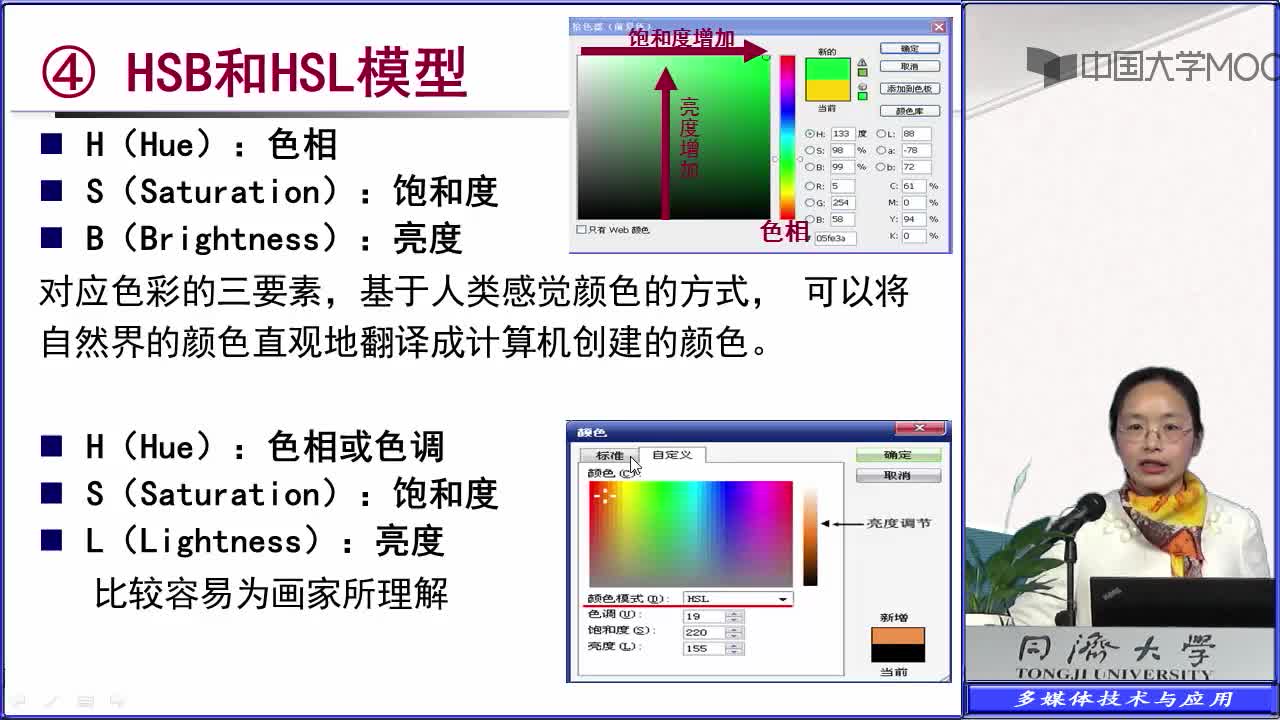

AD6900系统结构

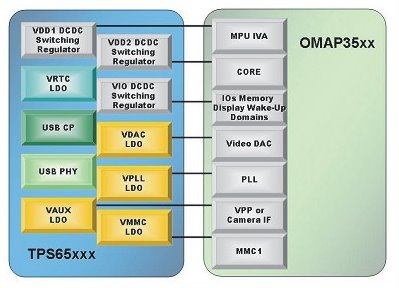

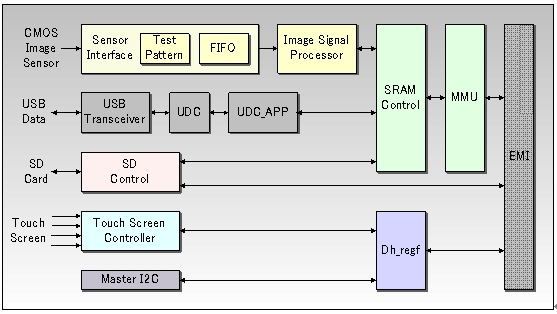

AD6900是低功耗无线数字基带芯片,高级电源管理系统满足了GSM、GPRS和EDGE终端的严格要求,还支持对计算量要求很大的多媒体功能。AD6900集成了Blackfin DSP处理器、ARM926EJ-S处理器、片内大容量RAM,以及外设扩展接口。AD6900包含支持专用数码相机、USB OTG、多媒体卡(MMC)、SD卡、IrDA红外端口、拇指轮、彩色显示器以及串行接口设备(例如蓝牙、WiLAN和A-GPS模块)的集成接口,结构框图如图1所示。

图1 AD6900结构框图

图1中的右上方是Blackfin处理器子系统,它由Blackfin处理器内核、L1代码存储器和数据存储器(可配置为高速缓存或SRAM)、统一的L2存储器、DSPDMA作为Blackfin DMA控制器,以及用于采集和处理GSM数据的DSP外设。Blackfin处理器子系统与系统总线接口单元(SBIU)交叉开关相连接。 图1右下方是ARM926-S微控制器子系统,它由ARM微控制器内核、高速缓存和紧密耦合内存(TCM)组成。系统中第三片片内内存称为系统RAM(L3存储器),Blackfin处理器和ARM微控制器都可访问它。连接外部设备的通用外设部分称为外设总线(PBUS),它主要用于控制大多数外部设备,vwin 基带(ABB)处理器和RF收发系统。

多媒体连接功能,即用于显示器和捕获设备的接口,由专用APBUS子系统支持。它由并行外围接口(PPI)控制器(支持10bit数码相机传感器或视频输入接口(包括ITU-656和ITU-601数字视频))和专用外部总线接口(支持并行液晶显示器,称为EBUS2)组成,消除了主要外部存储器接口中的噪声和负载。多媒体接口设备的数据搬移由称作APPDMA的多通道DMA控制器支持,它支持包括YUV4:2:2、YUV4:2:0和RGB565等其他格式的视频格式。

AD6900是基于分级存储器系统。从Blackfin处理器角度来看,L1缓存器提供有限容量的快速零等待存储能力。由于Blackfin处理器的时钟频率很高,所以L1存储器也十分昂贵,采用小容量的快速存储器才是经济上切实可行的方案。较低级别的存储器可提供较大的储存容量,但需要更长的访问时间。对ARM处理器来说也是一样,在处理器中具有容量相当小的快速L1高速缓存存储器。

存储器系统由以下几部分组成。

L1 DSP存储器:DSP内核工作在260MHz频率时的高速缓存和SRAM,包括80KB指令存储器和32KB数据存储器。

L1 ARM存储器:ARM内核工作在260MHz频率时的高速缓存和SRAM,包括20KB指令存储器和16KB数据存储器。

L2 存储器:以一半的DSP内核频率(130MHz)工作的64KB流水线SRAM,主要用来存储DSP数据和指令。

L3存储器:以几分之一DSP内核频率工作的256KB存储器,也称作系统RAM。

L4存储器:大容量片外存储器,包括SRAM、PSRAM(蜂窝RAM)、SDRAM、NOR以及NAND闪存。

AD6900的视频编解码 AD6900系统的对称性允许DSP和ARM内核都能够访问外围设备和存储器,在实现视频、音频和语音编解码时具有很大的灵活性。手机制造商可能只选择其中一个内核来实现编解码,这取决于系统的不同要求,例如指令执行性能、代码可用性和负载平衡。通常,由于DSP优化了数据路径并且具有数字计算能力,所以用DSP实现视频和音频编解码比用ARM内核实现具有更好的性能。在某些情况下,系统设计工程师可能希望使用ARM内核完成这项工作,这时代码在ARM内核中运行,或是在要求平衡DSP和ARM工作负载的计算中使用ARM内核。为了将多媒体系统和通信模块集成在同一DBB中,多媒体系统必须具有另一个功能,即从L1指令和数据高速缓存中执行程序。视频和音频编解码占用尽可能少的DMA和系统资源是非常重要的,这样可以避免引起对通信模块的意外影响。与以前基于DMA的旧方法相比,现代DBB中的软件对高速缓存使用进行了扩展。

衡量视频编解码的复杂性 在无线DBB上支持视频编解码,会大大增加处理模块的计算量。调制解调、语音和视频模块都是基于数据流的算法,也就是说它们处理输入数据流并且产生输出数据流。然而,通常视频编解码所处理的数据量(相对数据的计算量)要比语音编解码或典型调制解调模块的数据量大许多倍。以典型的电话语音编码器为例,其处理160个16bit的采样帧,产生80~130个输出bit。通常,优化的AMR编码器处理一帧的时间是250 000个处理器时钟周期(用Blackfin处理器来度量)。因此,每个输入语音采样大约需要1500个DSP处理器时钟周期,或者每个输入数据字节需要750个时钟周期。用类似的方法,EDGE均衡器的主要组件可输入122个16bit的采样帧,通常用大约100 000个DSP时钟周期完成数据处理,或者每个输入字节400个时钟周期。相反,以QCIF分辨率尺寸的视频解码器为例,其每帧具有25 344个像素,通常每帧执行1 000 000个DSP时钟周期。这相当于每个输出字节需要26个时钟周期(假设采用YUV4:2:0视频格式,每像素1.5字节编码),这种视频解码器要求输入的数据是EDGE数据均衡器的15倍多,并且几乎是比语音编解码器多6倍的数据。这意味着实现视频编解码器的主要难题与系统中需要输入的大量数据的数量有关。每个数据的计算量比手机中任何其他算法低很多。为了支持这种大量数据移动的要求,AD6900具有专用子系统APBUS,以及用于PSRAM和SDRAM的快速外部存储器接口。视频编解码器不仅需要非常宽的数据带宽,而且还需要大容量的存储器来存储大量的图像数据结构,这称为帧缓存。在AD6900中,帧缓存可配置在外部的PSRAM或SDRAM存储器中。

系统划分 AD6900具有处理完成QVGA图像格式视频解码和编码能力。由于视频编解码需要相当大容量的存储空间,所以将所有的存储对象放在最佳的物理存储器中对于编解码器的性能是非常重要的,因为必须使数据流量要求与系统接口和总线之间的可用带宽保持平衡。在很大程度上,视频编解码器的时钟性能是由传输像素数据接口的速度决定的。如图1所示,可用的物理存储器是L1(DSP和ARM)、L2(DSP)、L3(系统RAM)和L4(片外存储器,包括SRAM、PSRAM、SFDRAM和只读存储器)存储器。AD6900最重要的系统接口是外部总线接口,也称为EBUS。这是一个支持所有外部存储器设备的接口。液晶显示器是由称为EBUS2的单独外部接口支持,摄像头是由专用的PPI接口支持,这两个接口都属于APPBUS。

视频编解码器需要的存储器可以划分为以下几个分区:帧缓存器区、堆区、程序区、常量区和堆栈区。到目前为之,帧缓存器是最大的内存对象区,它能存储编码器和解码器所需要的帧。视频编解码器基于以下两个原则:帧内冗余和帧间冗余。帧间冗余仅使用帧N的不同部分像素来压缩帧N。帧间冗余使用每帧内的像素而不是帧N中的部分像素来压缩帧N,由于这个原因,视频编解码器需要过去(在某些情况下需要未来)帧的拷贝。MPEG4-SP简单类解码器在1/4VGA(QVGA)分辨率时需要两个帧缓存器,每个帧缓存器容量为110KB,总共为220KB。堆区包含多种类型的临时存储器,容量为80KB,程序区大约是150KB,常量区是另外30KB,堆栈区大小是2KB。

为了对视频编解码器内存储对象的布置作出最佳选择,也必须量化每个对象所需的数据带宽。表1给出了每个对象所需要的数据流量。例如,在解码器中帧缓存要求图像数据的每个像素具有4.36字节,这转换到QVGA分辨率的30 fps情况下大约是10MB/s,这大约是完整解码器所要求的总带宽的一半。堆区要求大约是6.7MB/s,或者是总带宽的32%。

表1 MPEG4的内存对象和相对带宽

帧缓存器所需要的给定带宽及其大小都放在在AD6900的外部存储器中(第四级),即PSRAM或SDRAM。SDRAM接口(图1中的SDC)能够达到130MB/s的最大吞吐量。在这种情况下帧缓存所需要的带宽10MB/s正好在可接受的限制范围内。可能的存储器映射如表1所示,包括帧缓存器、所有片外存储器的程序区和常量区以及系统RAM(第三级)中的堆区。

AD6900的视频编解码器支持MPEG4 simple profile Levels 0-3包括I-VOP和P-VOP帧格式、AC/DC系数预测、4-Motion向量、无限制向量移动以及短标头模式。(MPEG4用语,VOP或称为视频对象平面是表示某一时刻采样一帧图像数据的单位。)为了最大程度提供集成灵活性和与其他DBB相连的代码接口,AD6900的大多数代码基(大约90%的代码基)仍然使用C高级语言编写,仅有很小部分(大约10%)的接口采用Blackfin专用汇编语言编写。

另外也对MPEG4视频编解码器进行了优化,以便匹配现有总线和外部接口资源,并且也为了它们能产生尽可能少的数据流量。通过精心的管理数据移动,可使外部存储器所需的带宽减少30%。

多媒系统统除了支持编解码所需要的存储对象外,还需具有额外的帧缓存来支持输出和输入显示设备(例如液晶显示器和图像传感器模块)。然而,在APPBUS系统中也支持输入和输出设备本身,每种设备都有一个专用的外部接口。在最终的分析中,还必须考虑EBUS中这些存储器的大小和带宽分配。

可变的处理时间以及输出和输入缓存 与视频编解码相关的一个特殊问题是编码或解码一帧所要求的处理时间并不是常量。也就是说,它是与场景内容(特别是场景的运动量)、比特率和特定编码流结构或图像组(GOP)大小有关的一种复杂函数。 图2所示为例,示出了使用Blackfin DSP解码MPEG4流时,解码每帧所需要的时钟周期数。本测试的输入流采用CIF格式编码,比特率为350b/s,帧率为10fps,GOP大小为10。参数GOP表示两个I-VOP之间的P-VOP数量,因此在本例中每隔9个P-VOP就有一个I-VOP。图2中的每个点表示解码某帧所需的时钟周期数。实线表示20个采样值的移动平均数。从这幅图中可以很清楚地看出,I-VOP比P-VOP需要大很多的处理能力,每十个帧点的趋势明显地表明大约有700万~900万个时钟周期。P-VOP的处理时间最少为100万个时钟周期,最多高达1000万个处理时钟周期。

图2 MPEG4解码对时间的波动

每帧的时钟周期平均数与场景中的运动量成比例。场景的初始部分(1~420帧)有相当低的运动,而中间部分(421~630帧)有高的运动量。在场景的最后一部分(1260到最终的帧)中,场景中有非常大的运动量。这也表明P-VOP所需要的处理时间与场景的运动量有关,而I-VOP所要求的处理时间与此关联较小。 从这幅图中可以看出,当设计播放器时,必须考虑可变的解码时间。如果仅假设解码器要求最差情况下的执行时间,这时大约是每帧1000万个时钟周期,则由于大多数帧不需要那么多的时钟周期,过于保守的设计浪费了大量的DSP资源。 相反,现在是在解码器的输出端使用缓存来存储几个帧以为显示做准备。这种输出缓存系统能够平滑解码器执行时间的波动,所以允许设计师工程师按照平均执行时间来设计解码器。

MPEG4的品质因数 用来加速视频编解码器的许多优化方案可能会对编码器的数字性能引起负面影响。也就是说,使用太过分的措施减少编码器时钟周期数可能会引起由于峰值信噪比(PSNR)的减小而导致的编码性能变差。下降的PSNR将减小编码器压缩视频内容的能力,从而造成规定质量条件下输出的比特率比预期的高。例如,使用运动估计的方法可以非常简单或非常复杂,取决于所搜索的相邻宏块的数量。如果试图减少计算量而搜索太少的宏块数,则对于给定的压缩比,PSNA值会变低。

图3示出四种不同MPEG4编码器相应的速率失真曲线,它们都工作在Simple Profile @ Level 2简单类二级条件下。速率失真曲线是用来描述在给定某压缩比(或比特率)条件下产生的噪声(失真)进入视频流的程度。随着比特率下降,噪声增加(PSNR降低)。被测编码器是Blackfin AD6900编码器、ISO/IEC的anci C参考编码器、微软的参考编码器和xvid编码器。所使用的采样是称作“Akiyo”的测试顺序。性能较好的编码器可能对任何给定的比特速率都有较高的PSNR值。这幅图表明了Blackfin编码器和其他的编码器具有相同或者更好的性能。

图3 Blackfin DSP MPEG4-SP编码器的PSNR性能

AD6900的音频编解码 早期的多媒体手机几乎完全依靠于多种电话语音编解码来支持音频。例如AMR的标准编解码器用来辅助记录和播放QCIF格式甚至更低的低分辨率运动剪辑。而且,AMR也是MMS标准的主要部分,它可提供多媒体信息通信功能。然而,目前全功能多媒体手机需要支持多种音频编解码标准,例如MP3、AAC、AAC-LC、HE-AAC(也称为aac Plus)、RealAudio、WMA以及WB-AMR。 在AD6900中,MCU和DSP都能够运行音频编解码,并且和视频编解码一样,用哪一个处理器完成音频编解码取决于负载平衡、编解码可用性以及其他考虑因素。一般地,用DSP实现音频编解码要比MCU执行速度快并且功耗低。 以HE-AAC为例。Blackfin处理器实现高质量(HQ)类需要40MIPS的速率,实现低功耗(LP)类需要25MIPS,两种情况都采用立体声。ARM9E实现LP类需要33MIPS的速率,或者大约30%以上的处理器资源。AAC-LC是一个以13.8MIPS速率运行并且需要非常低DSP负荷的音频编解码的例子。

Blackfin处理器为实现语音编解码已做了高度优化。特别是NB-AMR语音编解码器,代码区大小为50KB,数据区大小为30KB,编码速率要求8~16MIPS的,解码速率为2MIPS。WB-AMR编解码器,代码区大小为50KB,数据区大小为25KB,编码速率要求20~30MIPS的速率,解码速率为6~8MIPS。 将音频编解码器集成到数字基带中所面临的难题远不如上面所述的视频编解码器复杂。一般地,音频编解码器可能具有非常高的数据计算速率,因此不需要配置大量的外部总线接口和存储器。音频编解码器所使用的数据对象也比较小。例如,HE-AAC的数据存储器(音频编码标准中存储器要求最大的一种)要求是70KB,而QVGA视频编解码器要求超过250KB。在AD6900中,通常将大多数音频编解码器的数据对象放置在外部存储器上(例如,SDRAM或PSRAM),这样就不会产生宽带宽问题。

结束语 本文讨论了系统设计工程师在使用无线数字基带处理器AD6900实现软件多媒体标准时所遇到的几个难题及其解决方案。在给定的大动态无线环境中,无线手机不仅必须支持多种空中接口,而且也必须支持多种复杂的视频和音频标准,这种情况下,移动终端利用软件可编程能力以保持高度灵活性是很关键的。

德赢Vwin官网

App

德赢Vwin官网

App

评论