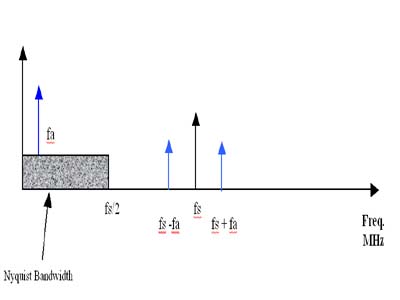

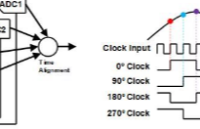

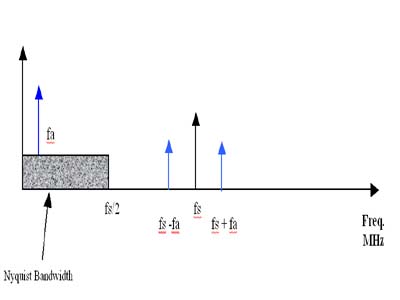

交织结构的优势可惠及多个细分市场。交织型

ADC最大好处是增加了带宽,因为

ADC的奈奎斯特带宽更宽了。同样,我们举两个100 MSPS

ADC交织以

实现200 MSPS

采样速率的例子。

2020-06-09 09:54:49

6440

6440

ADC使用若干个

ADC_CLK 周期对输入电压

采样,

采样周期数目可以通过

ADC_SMPR1 和

ADC_SMPR2 寄存器中的SMP[2:0]位而更改。

2012-03-22 10:45:30

5849

5849

在之前接触的设计中如果涉及要

实现

ADC

采样的话,往往会从精度和速率来考虑对性能的影响,一般来说精度是固定的或有一个最大精度设置,但是

采样速率的话,过快会造成

采样不准确,往往会对整个设计的性能造成限制

2017-09-22 11:24:34

9499

9499

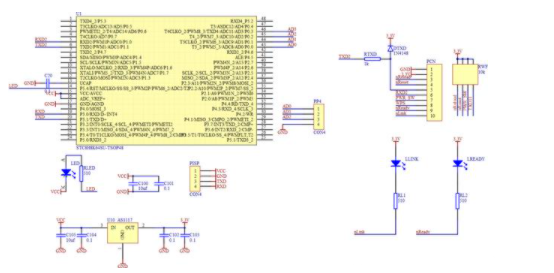

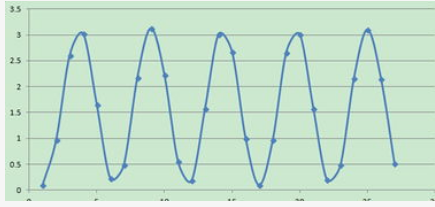

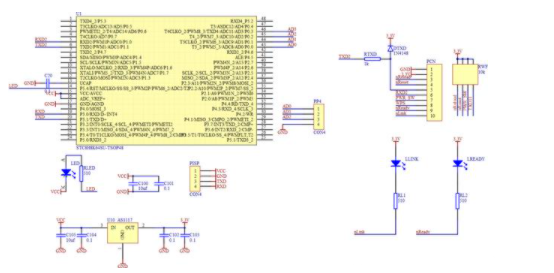

设计基于STC8G8K64U单片机的

高速

ADC

采样板,可以为普通的电路实验提供快速波形

采样的模块。

2021-04-28 11:12:00

7669

7669

如今大多数

ADC芯片里都集成了

采样保持功能,以便更好地处理交流信号,这种类型的

ADC我们叫做

采样

ADC,可是早些时候的

ADC并非

采样类型,而只是一个简单的编码器。 非

采样

ADC的一个缺点是,如果在

2021-04-28 11:02:50

24116

24116

ADC扫描

采样若干通道,数据保存在指定缓冲区,连续

采样若干次之后触发中断,然后读取

采样数据处理。

2022-09-09 12:54:11

1747

1747

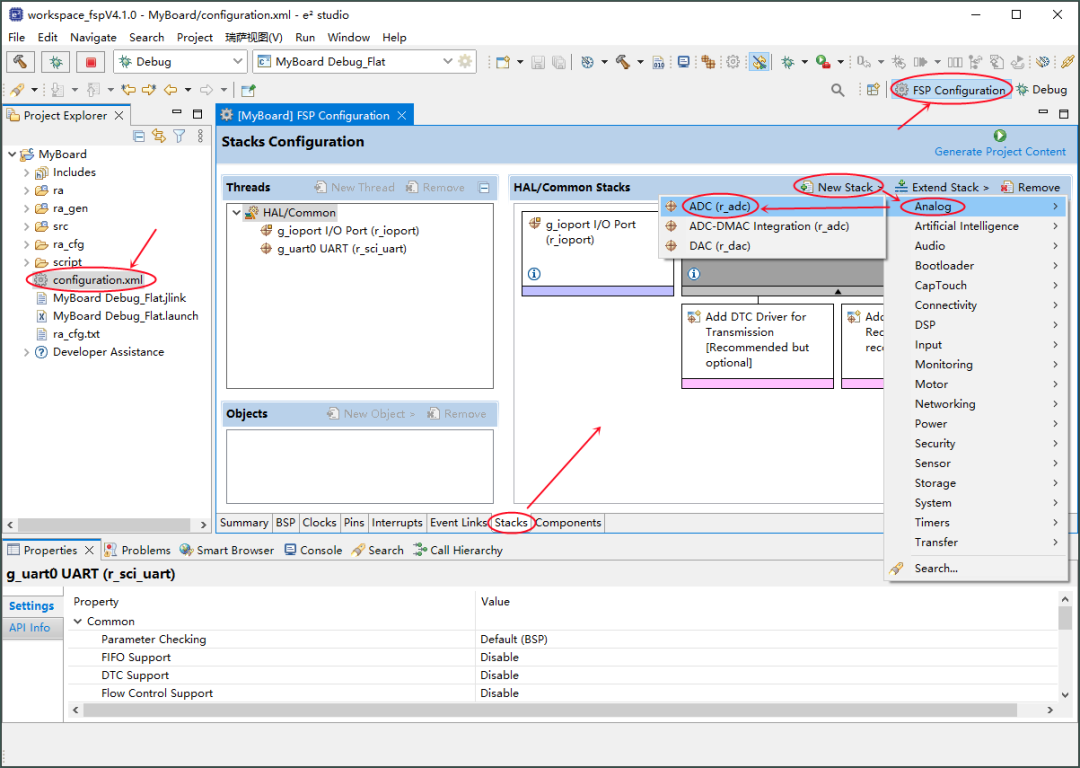

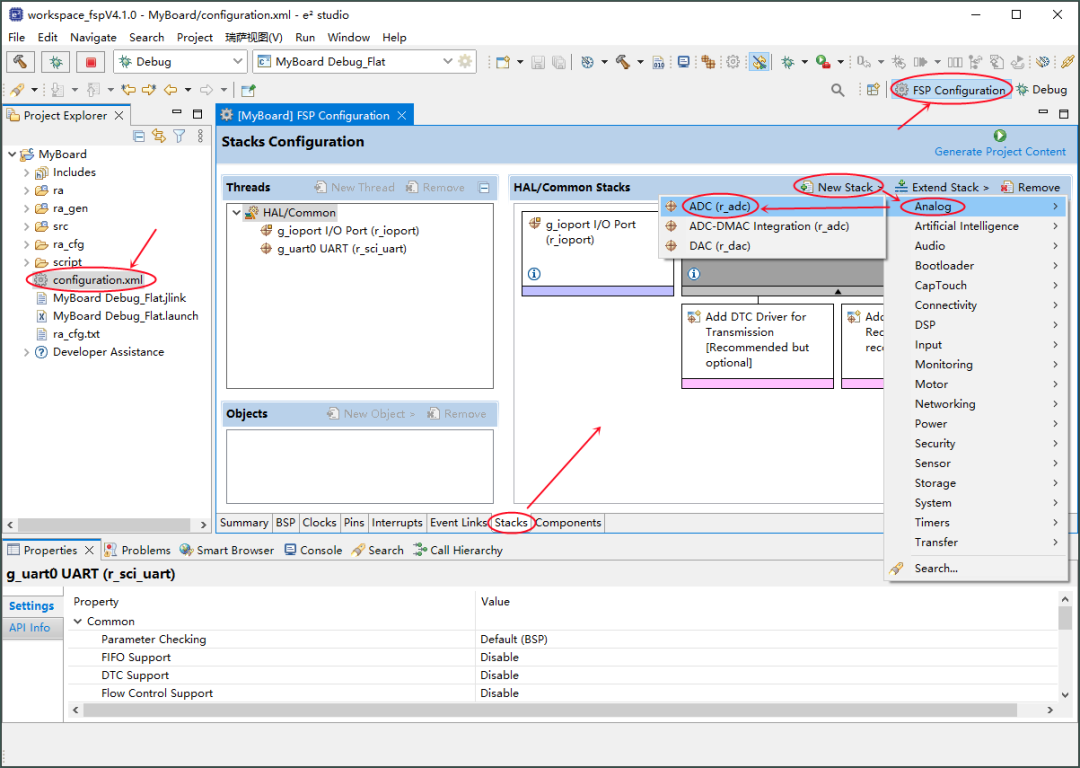

在RA6M4处理器的

ADC里,有两路

ADC可以分别

采样当前的CPU内部温度和参考电压值。

2022-12-19 09:23:20

1498

1498

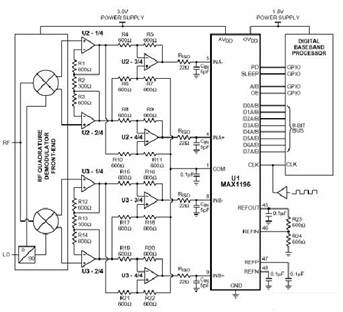

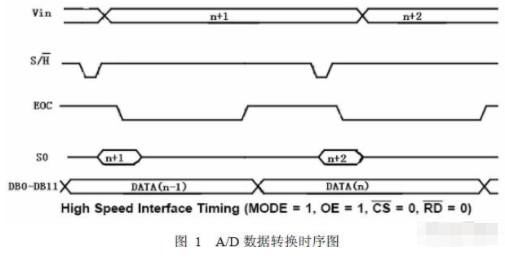

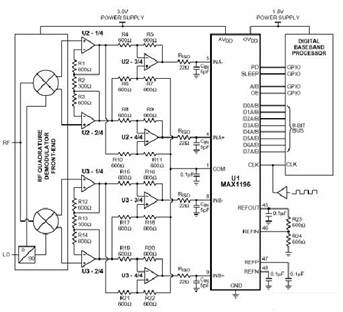

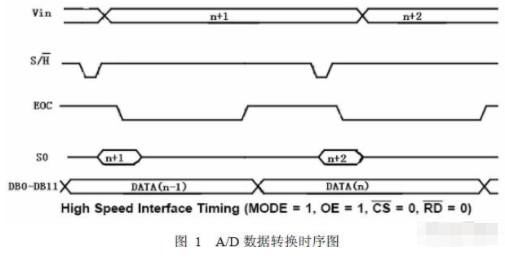

本文详细介绍了通常应用于IF和基带的

高速模数转换器(

ADC)的正确布板、元件

选择及元件布局。文中以高分辨率、

高速数据转换器MAX12555系列为例,介绍了优化电路设计、正确

高速布板、旁路和去耦技巧、热管理、元件

选择及布局。

2023-02-23 14:53:19

757

757

2808中epwm启动

adc

采样,现在希望在一次epwm中断中(

采样读值在epwm中断中,不对

adc设置中断函数),要求对某一通道连续

采样四次,而不是用四个通道,请问有没有可能

实现?

2020-05-12 09:33:34

作为一个偏向工控的芯片,

ADC

采样是一个十分重要的外设。STM32集成三个12位精度18通道的内部

ADC,最

高速度1微秒,结合DMA可以解放CPU进行更好的处理。

ADC接口上的其它逻辑功能包括:

2019-07-18 08:25:29

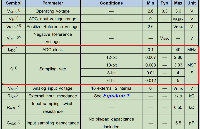

在雷达、导航等军事领域中,由于信号带宽宽(有时可能高于10MHz),要求

ADC的

采样率高于30MSPS,分辨率大于10位。目前

高速高分辨率

ADC器件在

采样率高于10MSPS时,量化位数可达14位,但

2021-04-14 06:16:30

ADC_RegularChannelConfig(

ADC1,

ADC_Channel_10, 1,

ADC_SampleTime_55Cycles5); //设置指定

ADC的规则组通道,设置它们的转化顺序和

采样时间

ADC

2020-08-28 08:00:16

采用的

高速AD:PXIe-5114 PXI示波器,

高速DA:PXIe-5413 PXI波形发生器,跪求

实现

高速DA

采样和AD的例程。

2018-08-21 16:19:19

大家好,我的问题与样品率有关。

选择任意波形

采样率的

ADC

采样率的标准是什么?在我的例子中,我的WaveDAC(50 KSPS)直接连接到

ADC(17位;5kSPS和实际转换率=4935个SPS

2018-12-28 15:26:46

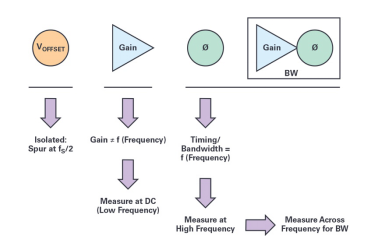

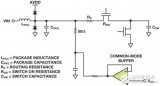

采用

高速模数转换器(

ADC)的系统设计非常困难,对于输入有两类

ADC架构可供

选择:缓冲型和无缓冲型。 缓冲和无缓冲架构的特征 高线性度缓冲器,但需要更高的功率; 更易设计输入网络与高阻抗缓冲器接口

2023-12-18 07:42:00

采用

高速模数转换器(

ADC)的系统设计非常困难,对于输入有两类

ADC架构可供

选择:缓冲型和无缓冲型。缓冲和无缓冲架构的特征缓冲架构的基本特征*高线性度缓冲器,但需要更高的功率;*更易设计输入网络与高

2018-10-18 11:23:57

正确

选择输入网络元件对于

高速

ADC的驱动和输入网络的平衡至关重要(参考应用笔记:“正确

选择输入网络,优化

高速

ADC的动态性能和增益平坦度”)。 在较高IF应用中,端接电阻的位置非常重要。交流耦合

2021-10-23 11:10:35

。近年来,NS、Atmel等公司都开发出了

高速

ADC,比如

ADC08D1000、AT84AS003TP等,它们都是经

采样后分多路降速进行传输。目前,多路并行数据传输存储成为

高速信号采集系统的主流趋势。

2019-07-05 08:11:34

外部

高速

ADC,PWM输出做时钟驱动,GPIO端口做数据接口,DMA读取到内部RAM,可以做到30M的

采样速度吗,新唐M4的IO口的读取速度有那么高吗

2023-06-26 06:26:11

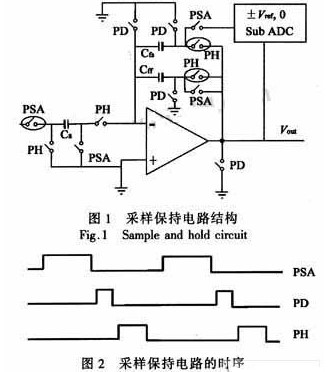

的应用中是一个关键部分。由于其他结构诸如两步快闪结构或内插式结构都很难在高输入频率下提供低谐波失真,因此流水线结构在

高速低功耗的

ADC应用中也成为一个比较常用的结构。 作为流水线

ADC前端的

采样保持

2018-10-08 15:47:53

高速、超宽带信号采集技术在雷达、天文和气象等领域应用广泛。高

采样率需要

高速的模/数转换器(

ADC)。目前市场上单片

高速

ADC的价格昂贵,分辨率较低,且采用单片超

高速

ADC

实现的数据采集对FPGA的性能和PCB布局布线技术提出了严峻的挑战。

2019-11-08 06:34:52

关于AD选型过程中,看到ADI出了一些针对直接射频

采样的

高速宽带

ADC和DAC,比如AD9625和AD9144,最大

采样率可以支持2.5GSPS和2.8GSPS. 我一直有个观点,就是SDR的一个

2018-10-10 14:28:33

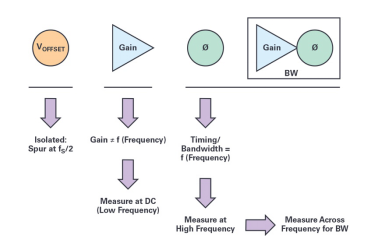

Nyquist 和 Shannon信息定理是什么?使用国家半导体

ADC演示

高速

ADC应用

欠

采样的作用与好处是什么?

2021-05-28 06:53:56

描述TIDA-01016 是一款适合高动态范围

高速

ADC的时钟解决方案。射频输入信号由

高速

ADC直接采用射频取样法捕获。

ADC32RF80 是一款双通道 14 位 3GSPS 射频取样

2018-09-30 09:26:09

关于

高速

ADC的

选择与应用你想要的都在这里

2021-05-25 06:57:38

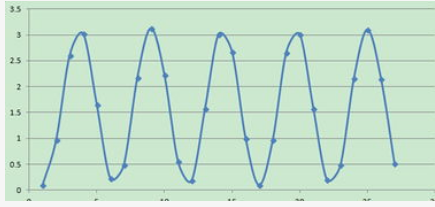

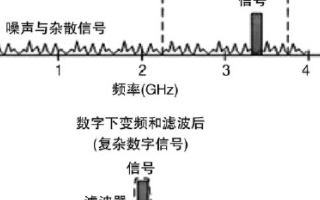

摘 要: 针对当前高

采样率

ADC成本高昂、

采样精度较低的问题,提出了基于

欠

采样的信号频率估计方法,通过组合使用低速

ADC,可以达到

高速

ADC的

采样效果。通过建立仿真对所提出的方法进行验证,结果显示

2018-07-31 10:24:36

介绍了一种基于现场可编程门阵列(FPGA)和第二代双倍数据率同步动态随机存取记忆体(DDR2)的

高速模数转换(

ADC)

采样数据缓冲器设计方法,论述了在Xilinx V5 FPGA中如何

实现

高速同步

2010-04-26 16:12:39

如何

合理的

选择PLC?如何利用三菱PLC

实现对印刷机的精确控制?

2021-11-03 07:02:27

高频应用如何才能取得最好性能所需的变频器特性?如何

选择适合高频应用的

高速

ADC?

2021-04-13 06:45:25

如何在Mbed OS操作系统下

实现

ADC

高速数据

采样?

2021-12-17 06:38:46

如何用STM32内置的

高速

ADC去

实现一个数字

采样示波器呢?其

实现方式是什么?

2021-11-08 06:52:55

需要一个

高速的

ADC在某个定点进行

采样,对

采样的电压值进行量化,但是找了一圈好像

高速的

ADC都是时钟直接控制的,只能在时钟的沿进行

采样。因为需要对外部事件产生的时间点对电压值进行量化操作,所以需要实时。按道理来说应该是有的啊我感觉

2022-03-14 21:14:01

ADI的

高速模数转换器(

高速

ADC)提供市场上最佳的性能和最高的

ADC

采样速度。该系列产品包括高中频

ADC(10MSPS -125MSPS)、集成接收机的低中频

ADC(125MSPS

2017-04-12 17:24:29

定时器触发

ADC

采样如何去

实现呢?如何使用

ADC的定时器去触发

ADC单次转换的功能呢?

2021-11-23 06:23:29

(使用放大器)也可以是无源(使用变压器或巴伦),具体取决于系统要求。无论哪种情况,都必须谨慎

选择元器件,以便

实现在目标频段的最优

ADC性能。射频

采样

ADC采用深亚微米CMOS工艺技术制造,并且半导体器件的物理

2018-11-01 11:25:01

怎么

实现

高速

采样保持电路的设计?

2021-10-11 07:42:17

谷歌搜索术语“模数转换器

选择”会产生了数以千计的搜索结果,证明这一任务对参与设计传感解决方案的许多人而言仍然具有挑战性。毕竟,从8位微控制器(MCU)中集成的简单10位

ADC到可以GHz速率解析

2019-03-18 06:45:12

需要

选择一款带宽在2MHz以上、

采样率在20MSPS、位数最好是16位的

高速

ADC,对于有正有负的正弦脉冲信号应

选择怎样的

ADC进行

采样?

2023-12-21 07:40:09

小弟最近项目中要对200KHz的超声波信号进行

采样,

采样时长越100us,无奈MCU自带的

ADC

采样率最高才200ksps,所以希望用MCU外带一块

高速

ADC来

实现。因为后续处理要求精度比较高,所以

2018-09-27 11:45:20

您好:我在选型

高速

ADC时,发现datasheet上标注了

采样率范围,给出最小值典型值和最大值。比如AD9208,输入时钟最高6GHz,

采样率三值分别为2500,3000,3100MSPS。请问

2018-07-30 08:53:53

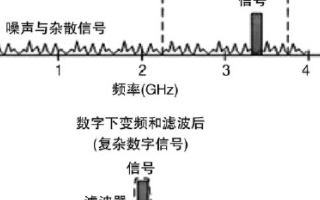

搬移到基带不会被Fs/2内的信号干扰,因此,Pipeline型的

ADC也常常被称为

欠

采样

ADC。(原文 德州仪器高性能单片机和模拟器件在高校中的应用和选型指南 p13),请问这里所说的把中频处的信号搬移到基带进行处理,是怎么

实现的?不理解?请教

2019-02-26 08:59:33

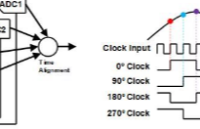

想请问大家: 我拟采用500Msps以上

采样率,JESD204B接口的

ADC芯片构建2通道以上的一个多通道

高速数据采集系统。为使讨论问题具体,简单,明确。现假设有一系统是4个

采样率500Msps

2018-07-24 10:45:54

需要

选择一款带宽在2MHz以上、

采样率在20MSPS、位数最好是16位的

高速

ADC,对于有正有负的正弦脉冲信号应

选择怎样的

ADC进行

采样?附件print_26.bmp2.3 MB

2018-10-26 09:33:24

问个类似的问题,如果我系统

采样频率是62MHz,对于同一款

ADC,比如AD9258,有AD9258-65,也有AD9268-80。我是否也要

选择-65的?

2019-03-11 09:48:26

ADI的

高速模数转换器(

高速

ADC)提供市场上最佳的性能和最高的

ADC

采样速度。该系列产品包括高中频

ADC(10MSPS -125MSPS)、集成接收机的低中频

ADC(125MSPS

2018-08-17 06:55:58

Luminary的

ADC过

采样应用笔记 本文主要介绍一种Luminary单片机高精度低成本AD转换的

实现方法,解决在某些要求高精度

ADC领域的Luminary应用问题。

2010-04-03 14:38:21

31

31

,信号带宽同等重要。我们发现,高于 Shannon 速率的

采样还有其它的好处,如处理增益可以极大地改善动态范围。系统设计师掌握了这一知识,就能在通用且价格

合理的标准

ADC中,正确地

选择

ADC

采样频率和精度。

2006-03-11 12:54:23

1448

1448

在

高速数据采集中,

高速

ADC的选用和数据的存储是两个关键问题。本文介绍一种精度为12位、

采样速率达25Msps的

高速模数转换器AD9225,并给出其与8位RAM628512存储器的接口电路。由于存储

2009-06-16 07:51:33

4226

4226

高性能、多通道、同时

采样

ADC在数据采集系统(DAS)中的设计摘要:本文将帮助设计人员

实现高性能、多通道、同时

采样的数据采集系统(DAS)。介绍了元器件的

合理

选择及其PCB布线

2009-06-23 21:12:55

4022

4022

高速

ADC,什么是

高速

ADC背景知识: 随着计算机技术、通信技术和微电子技术的

高速发展,大大促进了

ADC技术的发展,

ADC作为模拟量与数据量接

2010-03-24 13:28:01

9741

9741

设置

高速

ADC的共模输入电压范围(中文) 对于包含基带

采样、

高速

ADC的通信接收机,输入共模电压范围(VCM)非常重要。特别是对于单电源供

2010-03-30 17:59:39

3883

3883

本文介绍对于了解

高速

ADC电源设计至关重要的各种测试测量方法。为了确定转换器对供电轨噪声影响的敏感度,以及确定供电轨必须处于何种噪声水平才能使

ADC

实现预期性能,有两种测

2011-06-28 09:51:15

1027

1027

本文应用ADS 软件设计了一个4GSps 4bit GaAs 基超

高速

ADC,该

ADC芯片采用折叠内插结构

实现。文中详细描述了

采样保持电路(T/H)与折叠内插电路设计与仿真,芯片最终采用GaAs HBT 工艺

实现

2011-07-05 15:45:24

48

48

C8051F020

实现C8051F020

实现

ADC

采样芯片外的模拟电压

ADC

采样芯片外的模拟电压通过LCD显示,并通过串口发送到PC机

2015-11-12 14:23:11

29

29

基于FPGA的

高速多通道AD

采样系统的设计与

实现_徐加彦

2017-01-18 20:23:58

12

12

现代

高速

采样

ADC设计为低失真和宽失真信号处理系统中的动态范围。

实现规定的性能电平取决于

ADC自身外部的许多因素,包括适当的设计任何必要的支持电路。模拟输入驱动电路为尤其重要,因为在以下情况下,它会降低固有的

ADC动态性能:设计不当。

2022-08-01 14:18:13

0

0

了解

高速

ADC时钟抖动的影响将

高速信号数字化到高分辨率要求仔细

选择一个时钟,不会妥协模数转换器的

采样性能(

ADC)。 在这篇文章中,我们希望给读者一个更好的了解时钟抖动及其影响

高速模数转换器的性能

2017-05-15 15:20:59

13

13

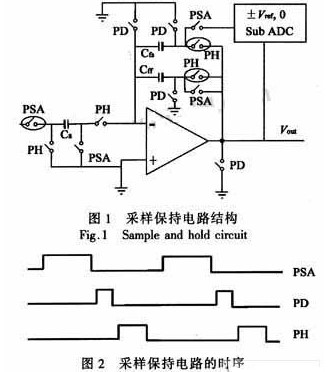

的应用中是一个关键部分。由于其他结构诸如两步快闪结构或内插式结构都很难在高输入频率下提供低谐波失真,因此流水线结构在

高速低功耗的

ADC应用中也成为一个比较常用的结构。 作为流水线

ADC前端的

采样保持电路是整个系统的关键模块电路

2017-11-16 15:23:31

1

1

是无源(使用变压器或巴伦),具体取决于系统要求。无论哪种情况,都必须谨慎

选择元器件,以便

实现在目标频段的最优

ADC性能。 简介 射频

采样

ADC采用深亚微米CMOS工艺技术制造,并且半导体器件的物理特性表明较小的晶体管尺寸支持的最大电压也较低

2017-11-22 17:46:05

1009

1009

本文主要讨论

采样时钟抖动对

ADC信噪比性能的影响以及低抖动

采样时钟电路的设计。

ADC是现代数字解调器和软件无线电接收机中连接模拟信号处理部分和数字信号处理部分的桥梁,其性能在很大程度上决定

2017-11-27 14:59:20

17

17

的应用中是一个关键部分。由于其他结构诸如两步快闪结构或内插式结构都很难在高输入频率下提供低谐波失真,因此流水线结构在

高速低功耗的

ADC应用中也成为一个比较常用的结构。 作为流水线

ADC前端的

采样保持电路是整个系统的关键模块电路

2017-12-07 10:45:23

5

5

1;

ADC在最

高速

采样的时候需要1.5+12.5个

ADC周期,在14M的

ADC时钟下达到 1Msps的速度,因为我主频是72M所以4分频后稍微高了点,18MHZ的

ADC时钟,

采样速度应该高于1M了。

ADC

采样2路同时

采样方式,用TIM2 CC2来生成时钟信号触发

ADC来

实现指定频率的

采样。

2018-05-18 01:44:00

24018

24018

任何高性能

ADC,尤其是射频

采样

ADC,输入或前端的设计对于

实现所需的系统级性能而言很关键。很多情况下,射频

采样

ADC可以对几百MHz的信号带宽进行数字量化。前端可以是有源(使用放大器)也可以

2018-06-04 10:50:00

1894

1894

数据采集系统的总体架构如图1所示,其中PCI核、DMA控制器与A/D控制器均在FPGA内部

实现。为

实现多路并行

采样,可选用多片A/D器件并行处理的方式,在FPGA的

高速状态机控制下,完成模拟信号经过

2018-08-28 10:16:07

12734

12734

的模块,

采样保持电路的性能直接决定了整个

ADC的性能,在以上系统中对功耗的要求十分严格。本设计在

实现

高速高精度

采样保持功能的同时,还

实现了MDAC功能,这样既能降低

ADC功耗又能减少芯片面积。

2019-06-13 08:19:00

4768

4768

在应用C8051F020的片内

高速

ADC进行时间序列

采样时,编写代码使

ADC工作于最

高速度是一个难题。本文从

ADC的C语言中断模式的驱动代码设计开始,分析对应的汇编语言中消耗CPU的主要步骤,研究

2019-09-12 08:00:00

6

6

1/14HZ = 71.4ms,一个周期

采样6000个点,则每两个点之间的

采样间隔为:71.4ms/6000 = 71.4 / 6 us;

选择

ADC的

采样周期为71.5,则

ADC时钟频率为:71.4 /(6 * 71.5)≈ 6MHZ。

2019-10-14 16:22:06

19056

19056

过去5年间,速度在1GSPS以上的

高速

ADC技术的

采样率和性能不断提升,全新器件能够

实现RF频谱的直接

采样。这些全新的模数转换器 (

ADC) 能够在保持出色噪声和线性的同时,在3GHz或更高的频率

2020-02-07 10:55:31

2001

2001

任何高性能

ADC,尤其是射频

采样

ADC,输入或前端的设计对于

实现所需的系统级性能而言很关键。很多情况下,射频

采样

ADC可以对几百MHz的信号带宽进行数字量化。前端可以是有源(使用放大器)也可以

2020-09-29 10:44:00

0

0

本文应用的测控系统中,按照测控需求,每个信号周期内通常

采样96 个点,

采样值累 加次数为4096 次,若

采样频率

选择为1 MHZ,则平均每个

采样占用时间为0.393216 秒,为 了满足测控实时性的要求。因此本系统设计中,

ADC的

采样频率

选择为1MHZ。

2020-12-25 10:31:43

8612

8612

AN-1388: 使用AD7779 24位同步

采样Σ-型

ADC

实现电能质量测量的相干

采样

2021-03-20 14:37:48

14

14

AD9260:2.5 MHz输出字率下16位分辨率的

高速过

采样CMOS

ADC数据表

2021-04-17 17:07:26

14

14

AD7864:4通道、同步

采样、

高速、12位

ADC数据表

2021-04-27 14:03:50

4

4

软件无线电直接射频

采样的

高速

ADC系统研究(开关电源技术与设计 潘永雄pdf)-该文档为软件无线电直接射频

采样的

高速

ADC系统研究总结文档,是一份很不错的参考资料,具有较高参考价值,感兴趣的可以下载看看………………

2021-09-16 13:35:42

19

19

STM32

ADC过

采样技术

2021-12-08 16:21:06

41

41

project

选择芯片(此处我选的是STM32F051R8

选择结束后如下配置一下芯片的相关配置我是ST-LINK下载所以

选择SW模式.

ADC是4通道

采样1-4.打开串口一.只要左边的选项选好,右边的芯片的引脚就自动配置好.RCC我在左侧的表格里没勾选,因为我用的是内部时钟啊,不用

2021-12-24 19:29:29

15

15

现代接收器系统对更高容量和更多数据吞吐量的需求不断增加。我们必须拥有高

采样率数据转换器和高动态范围系统。一些模数转换器(

ADC)架构确实

实现了非常高的

采样率,但没有最佳的信噪比(SNR)。其他器件可

实现非常好的SNR,但其

采样率有限。没有一个内核

ADC器件同时满足高

采样速率和动态范围的要求。

2023-04-15 09:49:09

1242

1242

本文将帮助设计人员

实现高性能、多通道、同时

采样的数据采集系统(DAS)。介绍了元器件的

合理

选择及其PCB布线,以优化系统性能。Maxim的MAX1308、MAX1320和MAX11046是极具特色的同时

采样

ADC。本文给出的测试数据说明了遵循设计要点能够为系统带来的各项益处。

2023-06-16 14:39:24

833

833

adc

采样率和带宽的关系

ADC(Analog-to-Digital Converter),即模拟转数字转换器,是将模拟信号转换成数字信号的重要器件。其中,

采样率和带宽是

ADC性能参数之一,也是

2023-09-12 10:51:12

6012

6012

运用DMA功能

实现高级定时器和

ADC的同步触发

采样在做BLDC电机控制时,需要

ADC的

采样时刻和定时器产生的PWM波形相配合,才能获取准确的

采样值,本文介绍了CW32F030系列芯片通过运用DMA功能

实现高级定时器和

ADC的同步触发

采样的功能。

2022-06-06 13:35:55

31

31

大家在使用

ADC

采样的时候是否计算过

ADC的

采样率,这个问题非常关键!

2024-01-23 09:29:47

560

560

德赢Vwin官网 App

德赢Vwin官网 App

评论