的输出,并且如果正弦波不够完美的话,在振荡器内部稍微改造下来改变它的性能。当合成器执行反馈时,它们有时称为锁相环或PLL。www实际生活中的介成器作常复杂,也很昂贵。它们可以完成许多功能而不仅仅是反馈

2017-12-06 14:06:07

补偿,需要更大的功耗。 小数分频锁相环相比整数分频,价格较高。 Q:小数分频的锁相环杂散的分布规律是什么?A:小数分频的锁相环由于应用在工作的鉴相频率较高,所以其参考杂散也会分布到偏离载波很远的位置上

2019-01-16 12:27:07

,二者表现出差不多的杂散性能。一个通用的规则是,在200kHz的信道间隔以下,小数分频的杂散性能优于整数分频。小数分频的锁相环需要良好的频率规划,以避开大的杂散出现。所以使用起来,难度较大。整数

2017-04-27 15:58:16

频率合成器的主要性能指标锁相环频率合成器原理锁相环频率合成器捕捉过程的分析与仿真

2021-04-22 06:27:35

;><strong>锁相环频率合成器的方案研究</strong><br/><

2010-03-16 10:59:24

做了一批锁相环频率合成器10套,有2套在做完环境试验和老化后出现跳频工作一段时间后失锁问题,主要现象是:开机工作正常,跳频工作几分钟后,失锁,跳频速率每分钟1000跳,失锁后无法再锁定回去,一直失锁

2018-09-30 11:52:13

ADI是高性能模拟器件供应商,在锁相环领域已有十多的的设计经验。到目前为止,ADI的ADF系列锁相环产品所能综合的频率可达8GHz,几乎能够涵盖目前所有无线通信系统的频段。ADF系列PLL频率合成器

2018-10-31 15:08:45

ADI是高性能模拟器件供应商,在锁相环领域已有十多的的设计经验。到目前为止,ADI的ADF系列锁相环产品所能综合的频率可达8GHz,几乎能够涵盖目前所有无线通信系统的频段。ADF系列PLL频率合成器

2018-11-06 09:03:16

的频带,但是时钟频率较高的DDS价格昂贵。采用锁相环合成,杂散性能与相位噪声性能较好,可实现的工作频带宽,但频率切换速度较慢,跳频时间较长。由于系统并没有对频率切换速度提出过高要求,因此从价格方面考虑

2019-06-21 06:32:34

DC1959A-A,演示板,采用LTC6948-1超低噪声和杂散整数N频率合成器,集成VCO。 DC1959A提供50欧姆SMA连接器,用于参考频率输入fREF(REF + IN)和差分RF输出(RF +和RF-)

2019-07-18 08:08:07

DC1959A-C,演示板,采用LTC6948-3超低噪声和杂散整数N频率合成器,集成VCO。 DC1959A提供50欧姆SMA连接器,用于参考频率输入fREF(REF + IN)和差分RF输出(RF +和RF-)

2019-07-18 08:43:41

EVAL-ADF4351EB1Z,该板设计用于允许用户评估ADF4351频率合成器的性能,以实现锁相环(PLL)。它显示了该板,其中包含ADF4351集成合成器和VCO,用于输出信号的SMA连接器

2019-03-01 08:03:03

Delta Sigma LMX2502和LMX2512的N射频锁相环包括压控调制器振荡器(VCO)、环路滤波器和分数N射频一致地如果合成器系统,这些模块构成一个闭环射频合成器系统。LMX2502支持韩国

2020-09-25 17:41:56

`MTI品牌频率合成器产品介绍MTI锁相环询价热线MTI锁相环现货MTI锁相环代理王先生*** 深圳市首质诚科技有限公司,MTI-Milliren Technologies Inc将其石英振荡器性能

2019-06-23 17:07:53

锁相环具有较好的低通特性,从而可以消除小数分频杂散。 图7为新的频率合成器的原理框图。图中每个累加器的输出和下一个累加器的输入相接,累加器的溢出可以控制分频比。为了减小剩余相位抖动,需合理控制分频比

2012-08-02 11:08:55

介绍了锁相环路的基本原理,分析了集成锁相环芯片ADF4106的工作特性,给出了集成锁相环芯片ADF4106的一个应用实例,为高频频率合成器的设计提供了很好的思路。 关键词:ADF4106,锁相环,频率合成器,环路滤波器

2019-07-04 07:01:10

FPGA技术、锁相环技术、频率合成技术,设计出了一个整数/半整数频率合成器,能够方便地应用于锁相环教学中,有一定的实用价值。

2019-06-25 06:36:13

问:什么是PLL频率合成器?

2019-09-17 19:00:51

尤其在无线通信应用中,常常需要以非常短的时间切换 PLL (锁相环) 合成器的输出频率。在这类情况下,人们经常希望在相对较大的频率跳变之后,以不到 20µs 时间实现稳定的输出频率。以下我们将介绍

2019-07-25 06:16:50

(DS)、锁相环频率合成技术(PLL)、直接数字频率合成技术(DDS)、混合频率合成技术四种实现方式,其中锁相环频率合成器是射频电路中最常使用的一种结构,相比于其他几种结构,PLL结构能够在有限的功耗限制

2018-09-06 14:32:13

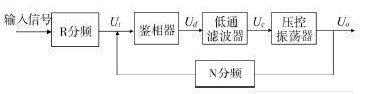

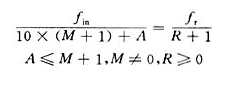

的频率切换。 频率合成技术是利用参考频率源来产生具有一系列离散的、高准确度、高稳定度频率信号的一项技术。锁相式频率合成器是利用锁相环(PLL)将压控振荡器(VCO)的频率锁定在某一个频率点上,由压控振荡器

2019-06-25 05:00:05

直接数字频率合成(DDS)在过去十年受到了频率合成器设计工程师极大的欢迎,它被认为是一种具有低相位噪声和优良杂散性能的灵活的频率源,基于DDS的频率合成器在许多应用中能比基于锁相环(PLL)频率

2019-07-08 07:26:17

基于单片机和锁相环MC14046频率合成器的设计,要求是产生频率在1MHZ左右,求大家指点。

2012-04-11 14:01:59

本文设计了一种多环锁相频率合成器。多环锁相环路有直接数字频率合成(DDS)环路和锁相频率合成环路(PLL)组成。充分利用两个不同环路的优点,既保证了高的输出频率,又得到了较高的频率分辨率。【关键词

2010-05-13 09:09:53

。本文结合FPGA技术、锁相环技术、频率合成技术,设计出了一个整数/半整数频率合成器,能够方便地应用于锁相环教学中,有一定的实用价值。那么有谁知道具体该如何利用FPGA设计PLL频率合成器吗?

2019-07-30 07:55:22

PLL应用中颇具价值的注意事项和使用技巧基于锁相环(PLL)技术的频率合成器

2021-05-12 06:59:03

锁相环频率合成器是什么原理?基于CD4046的锁相环频率合成器的设计

2021-04-12 06:28:35

控制用微处理器的主要性能有哪些?处理器在调频(FM)调谐器中的应用是什么?数字调谐系统有哪些性质?怎样去设计一种基于PLL(锁相环)合成器的数字调谐系统?

2021-08-17 07:03:36

所示。该器件具有一个输出分频器(在VCO之后),但输出频率和VCO频率都接近20MHz的整数倍。这种设置将迫使任何PLL产生分数杂散。…

2022-11-18 07:51:05

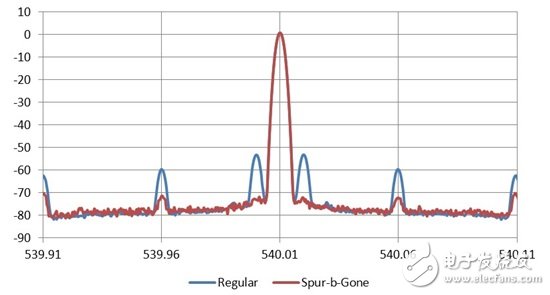

您曾设计过具有分数频率合成器的锁相环(PLL)吗?这种合成器在整数通道上看起来很棒,但在只稍微偏离这些整数通道的频率点上杂散就会变得高很多,是吧?如果是这样的话,您就已经遇到过整数边界杂散现象了

2018-09-06 15:11:00

小弟正在调试一款X波段(9.6-10.8GHz)的锁相环,采用的是内部集成VCO的HMC778LP6CE芯片。在调试中,我发现在距中心频率50Hz整数倍的频率处有很多杂散,请问各位大神这些杂散

2014-07-21 15:47:54

EV-ADF41020EB1Z,用于ADF41020 PLL频率合成器评估板的评估板。评估用于锁相环(PLL)的ADF41020频率合成器。它包含ADF41020合成器,100 MHz TCXO,电源,USB接口和RF输出。板载有一个有源环路滤波器和一个13 GHz VCO

2019-02-28 07:23:02

评估板EVAL-ADF4152HVEB1Z旨在让用户评估ADF4152HV频率合成器的性能,以实现锁相环(PLL)。该板包含ADF4152HV合成器,环路滤波器,1GHz至2GHz倍频程的压控振荡器

2019-03-01 10:17:42

要满足苛刻的频率合成器要求,通常需要做到一定程度的设计灵活性。基本的锁相环(PLL)频率合成器能以低成本、高空间效率、低功耗封装提供合理的频谱纯度和频率捷变,因此它在射频(RF)系统核心位置发挥作用

2019-07-08 06:10:06

DC1705C-C,演示板,采用LTC6946超低噪声和杂散整数频率合成器,集成VCO。 VCO不使用外部组件,无需外部系统支持即可进行内部校准

2019-03-01 10:06:25

DC1705B-A,演示板,采用LTC6946超低噪声和杂散整数频率合成器,集成VCO。 VCO不使用外部组件,无需外部系统支持即可进行内部校准

2019-02-28 09:40:18

驱动高压锁相环频率合成器电路的VCO

2021-01-11 06:02:04

锁相环频率合成器:相位噪声问题和宽带循环:

In this chapter we locate the context of this thesis by introducing

2009-07-25 17:18:33 0

0

文章分析了小数分频频率合成器中存在的相位杂散的问题,介绍了采用Σ — Δ 调

制技术的小数频率合成器。详细介绍了Σ — Δ 调制频率合成器的原

2009-08-19 11:00:37 12

12 应用FPGA,采用PLL频率合成技术,结合教学实验平台的需要,设计出了一个整数/半整数频率合成器,输出范围为1kHz~999.5kHz,步进频率可达到0.5kHz。与以前的教学实验装置相比,系统在性能指

2010-09-01 09:43:34 45

45

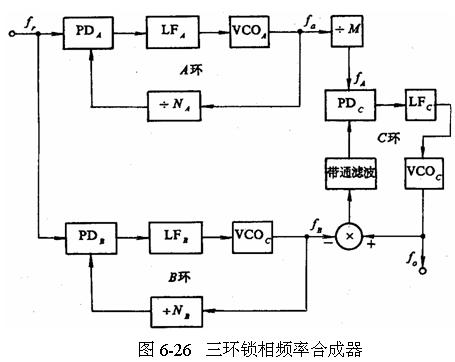

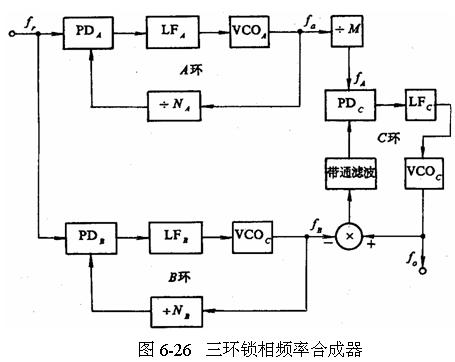

三环锁相频率合成器

2008-04-21 14:30:43 2076

2076

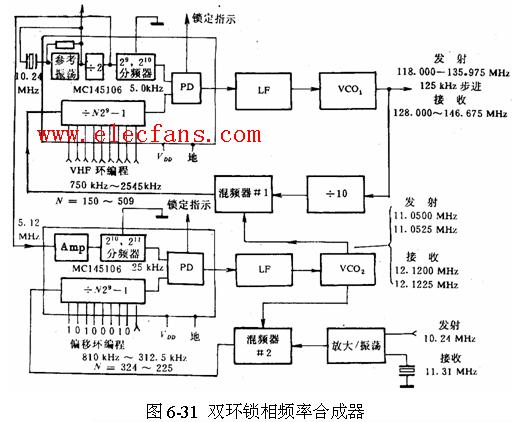

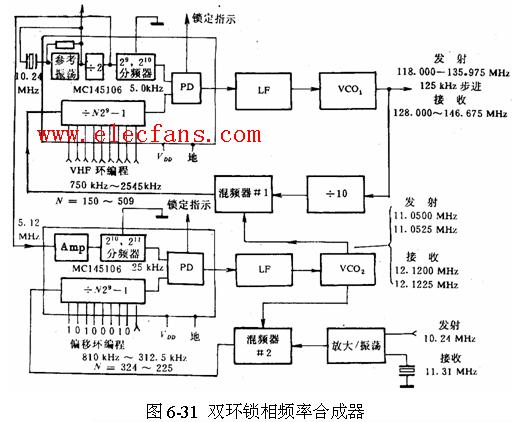

双环锁相频率合成器

2008-04-21 14:38:36 1088

1088

介绍了锁相环路的基本原理,分析了集成锁相环芯片ADF4106的工作特性,给出了集成锁相环芯片ADF4106的一个应用实例,为高频频率合成器的设计提供了很好的思路。

2009-05-05 19:57:57 2585

2585

用AD9850激励的锁相环频率合成器

提出了一种DDS和PLL相结合的频率合成方案,介绍了DDS芯片AD9850的基本工作原理、性能特点及引脚功能,给出了以AD9850作

2009-12-08 15:27:31 1557

1557

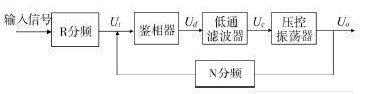

单环锁相频率合成器,单环锁相频率合成器是什么意思

频率合成的历史

频率合成器被人们喻为众多电子系统的“心脏”。现代战争是

2010-03-23 11:36:28 883

883 变模分频锁相频率合成器是什么意思

频率合成的历史

频率合成器被人们喻为众多电子系统的“心脏”。现代战争是争夺电子频谱控

2010-03-23 11:41:23 1384

1384 集成锁相环频率合成器,什么是集成锁相环频率合成器

频率合成的历史

频率合成器被人们喻为众多电子系统

2010-03-23 11:45:44 770

770 频率合成器可以提供大量精确、稳定的频率作为无线通信设备的本振信号。简要介绍了锁相环频率合成器的基本原理,并利用整数N锁相芯片ADF4112设计了一个宽波段的频率合成器。讨论

2011-05-03 18:20:24 101

101 频率合成器作为无线收发器中的核心单元电路是决定收发器性能好坏的关键因素也是实现全集成无线收发器的主要难点。本书书名:锁相环 频率合成器 ,作者:张厥盛,发行地:电子工业

2011-07-10 11:19:43 0

0 为得到性能优良、符合实际工程的锁相环频率合成器,提出了一种以ADI的仿真工具ADIsimPLL为基础,运用ADS(Advanced Design System 2009)软件的快速设计方法。采用此方法设计了频率输出为

2013-01-10 16:50:36 81

81 为了满足宽频段、细步进频率综合器的工程需求,对基于多环锁相的频率合成器进行了分析和研究。在对比传统单环锁相技术基础上,介绍了采用DDS+PLL多环技术实现宽带细步进频综,输

2013-04-27 16:26:51 48

48 结合数字式频率合成器(DDs)和集成锁相环(PLL)各自的优点,研制并设计了以DDS芯片AD9954和集成锁相芯片ADF4113构成的高分 辨率、低杂散、宽频段频率合成器,并对该频率合成器进行了分析

2017-10-27 17:54:21 8

8 无线电系统会因为各种各样的原因而采用基于锁相环(PLL)技术的频率合成器。PLL 的好处包括: (1)易于集成到 IC 中。 (2)无线信道间隔中的灵活性。 (3)可获得高性能。 (4)频率合成器

2017-11-16 15:28:13 15

15 业界领先的射频、微波及毫米波产品供应商美国Pasternack公司推出一系列新型USB控制锁相环(PLL)频率合成器。在将信号完整性作为首要目标的射频和微波通信系统中,锁相环频率合成器可提供高频率

2018-04-26 11:16:00 687

687 频率合成器主要有直接式、锁相式、直接数字式和混合式4种。目前,锁相式和数字式容易实现系列化、小型化、模块化和工程化,性能也越来越好,已逐步成为最为典型和广泛的应用频率合成器[1]。本文主要采用集成锁相环PLLphase-Lockde Loop芯片CD4046,运用FPGA来实现PLL频率合成器。

2019-01-07 09:52:00 3076

3076

PLL频率合成器和ADIsimFrequencyPlanner

2019-07-01 06:12:00 3764

3764 几乎每个RF和微波系统都需要频率合成器。频率合成器产生本振信号以驱动混频器、调制器、解调器及其他许多RF和。频率合成器常被视为系统的心跳,创建方法之一是使用锁相环(PLL)频率合成器。传统

2020-10-15 10:43:00 8

8 利用频率合成器,你可以产生单一参考频率的各种不同倍数的输出频率。其主要应用是为RF信号 的上变频和下变频产生本振(LO)信号。频率合成器在锁相环(PLL)中工作,其中鉴频鉴相器(PFD)将反馈频率

2020-10-12 10:43:00 0

0 UG-160: 整数N分频PLL频率合成器评估板

2021-03-20 10:17:59 6

6 CN-0369:低相位噪声的转换锁相环频率合成器

2021-03-20 13:21:15 5

5 ADF4155:整数N/小数N分频PLL频率合成器

2021-03-20 17:01:57 11

11 UG-369:ADF4151锁相环频率合成器评估板

2021-04-19 20:14:47 6

6 UG-802:用于锁相环的ADF5355频率合成器评估

2021-04-25 12:23:05 3

3 UG-873:评估ADF4355-3小数/整数N锁相环频率合成器

2021-04-28 14:35:35 5

5 UG-804:评估ADF4355-2小数/整数N锁相环频率合成器

2021-05-10 08:26:33 8

8 UG-383:用于锁相环的ADF4159频率合成器评估

2021-05-10 13:26:06 1

1 UG-485:ADF4153A小数N锁相环频率合成器评估板

2021-05-16 13:22:43 8

8 UG-1087:用于锁相环的ADF5356频率合成器评估

2021-05-17 09:38:07 4

4 ADF4217:双射频锁相环频率合成器过时数据表

2021-05-17 11:55:55 2

2 UG-389:ADF4xxx锁相环频率合成器的USB转并行转接板

2021-05-24 11:46:02 6

6 UG-686:ADF4155锁相环频率合成器评估板

2021-05-25 16:46:51 4

4 所设计的频率合成器,要求相位噪声低,输出频率800~1 000 MHz,共88个波道,通过单片机发送的频率控制字进行波道选择。在对比各种大规模集成频率合成芯片性能的基础上,选用了单片大规模集成锁相环频率合成芯片PE3236作为核心电路,构成锁相式频率合成器。

2021-05-28 10:30:08 4153

4153

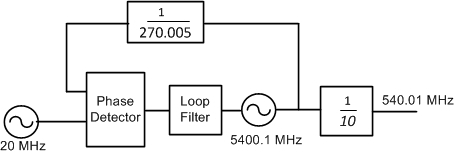

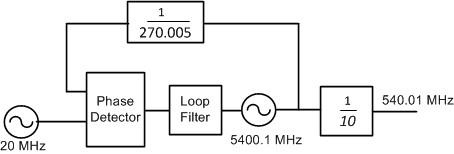

图1所示电路框图是一个低相位噪声转换环路频率合成器(也称为偏移环路)。此电路将ADF4002 锁相环 (PLL) 的较低100 MHz参考频率转换到5.0 GHz至5.4 GHz的较高频率范围

2021-05-29 08:17:44 20

20 ADF4150HV锁相环频率合成器UG-406评估板

2021-06-03 11:16:33 7

7 您曾设计过具有分数频率合成器的锁相环(PLL)吗?这种合成器在整数通道上看起来很棒,但在只稍微偏离这些整数通道的频率点上杂散就会变得高很多,是吧?如果是这样的话,您就已经遇到过整数边界杂散现象了 —— 该现象发生在载波的偏移距离等于到最近整数通道的距离时。

2022-02-06 09:29:00 1679

1679

锁相环(PLL)电路是由压控振荡器(VCO)和鉴相器组成的反馈系统,振荡器信号跟踪施加的频率或相位调制信号是否具有正确的频率和相位。需要从固定低频率信号生成稳定的高输出频率时,或者需要频率快速变化时,都可以使用PLL。典型应用包括采用高频率、电信和测量技术实现滤波、调制和解调,以及实现频率合成。

2022-06-13 16:14:35 3319

3319 ADF435x微波宽带频率合成器搭配外部环路滤波器和外部基准频率使用时,可实现小数N分频或整数N分频锁相环 (PLL) 频率合成器。ADF435x使用一系列分频器,可以在35MHz到 6800MHz范围内运行。

2022-07-23 09:30:42 2

2 时序至关重要:改善分数分频锁相环合成器中的整数边界杂散状况

2022-11-04 09:50:31 1

1 频率信号(经过加减乘除四则运算),产生同样高稳定度和高精度的大量离散频率的技术。根据频率合成原理所组成的设备或仪器称为频率合成器。 pll是锁相环 (phase locked loop),pll是一种用于锁定相位的环路。锁相环的控制量是信号的频率和相位。它是一

2023-02-24 18:19:52 8275

8275

您曾设计过具有分数频率合成器的锁相环(PLL)吗?这种合成器在整数通道上看起来很棒,但在只稍微偏离这些整数通道的频率点上杂散就会变得高很多,是吧?如果是这样的话,您就已经遇到过整数边界杂散现象了 —— 该现象发生在载波的偏移距离等于到最近整数通道的距离时。

2023-04-18 09:29:56 687

687

锁相环频率合成器的优缺点 锁相环频率合成器,又称为PLL(Phase Locked Loop),是一种广泛应用的电路,能够将输入信号的频率合成为电路所需要的频率,并且能够实现对信号的相位和频率

2023-09-02 14:59:33 1216

1216 如何调试锁相环频率合成器? 锁相环频率合成器(PLL)是电路中常见的一个模块,用于生成稳定的高精度频率信号。PLL的核心部分是相位检测器和环路滤波器,其主要工作原理是通过不断调整反馈回来的参考信号

2023-09-02 15:06:37 504

504 基本PLL锁相环、整数型频率合成器和分数型频率合成器。下面将详细介绍这三种模式的作用和特点。 第一种:基本PLL锁相环 基本PLL锁相环是PLLf工作的最基本形式,它主要由比较器、低通滤波器、VCO和分频器组成。其基本工作原理是将输入信号和VCO输出的信号进行

2023-10-13 17:39:48 1102

1102 德赢Vwin官网

网站提供《基于ADF4111的锁相环频率合成器设计.pdf》资料免费下载

2023-10-20 14:45:29 0

0 频率合成器和锁相环是两种常见的电子设备,用于生成稳定的频率信号。尽管它们的功能都是产生特定频率的信号,但它们在工作原理和应用方面有着明显的区别。

2024-02-27 18:22:59 840

840

德赢Vwin官网

App

德赢Vwin官网

App

评论