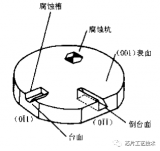

外延

工艺是指在衬底上生长完全排列有序的单晶体层的

工艺。一般来讲,

外延

工艺是在单晶衬底上生长一层与原衬底相同晶格取向的晶体层。

外延

工艺广泛用于半导体制造,如集成电路工业的

外延硅片。MOS 晶体管

2023-02-13 14:35:47

10449

10449

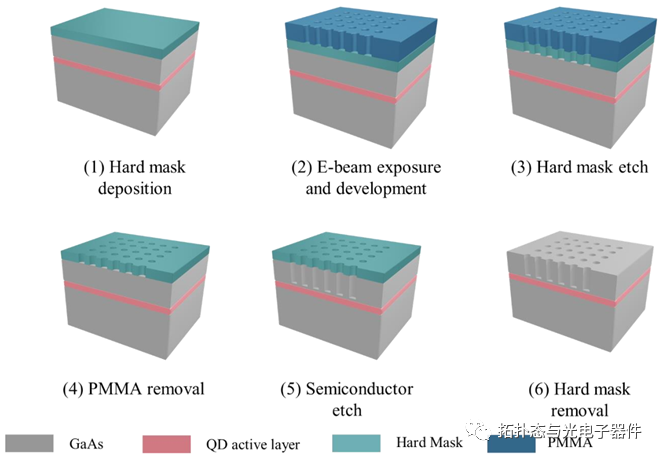

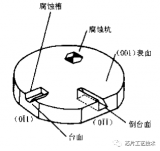

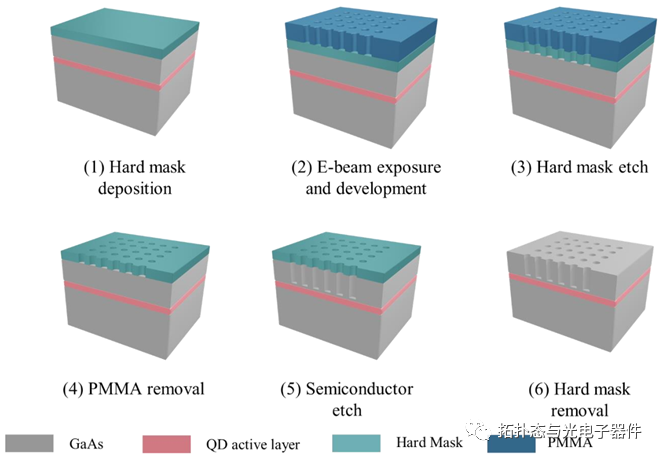

设计

外延片参数,第一次

外延,制备光子晶体,第二次

外延,制备台面和电极。

2023-05-22 11:43:35

1467

1467

一些后处理步骤,例如研磨、化学机械研磨(CMP)、SiC

外延、注入、检测、化学气相沉积(CVD)和物理气相沉积(PVD)。SiC

晶

圆因其半透明性质和材料硬度而面临许多挑战,这需要对关键

工艺步骤设备进行

2019-05-12 23:04:07

我国科学家成功在8英寸硅片上制备出了高质量的氧化

镓

外延

片。我国氧化

镓领域研究连续取得突破日前,西安邮电大学新型半导体器件与材料重点实验室的陈海峰教授团队成功在8英寸硅片上制备出了高质量的氧化

镓

外延

片

2023-03-15 11:09:59

`各位大神,小弟初学LV,想编一个

工艺流程仿真计算的软件,类似这样一个东西如图所示:先设置每一个单体设备的具体参数,然后运行,得出

工艺流程仿真计算的结果,计算模型有很多公式,可以直接编程。但要想达到

2015-11-17 17:18:22

有没有能否切割

晶

圆/硅材质滤光

片的代工厂

介绍下呀

2022-09-09 15:56:04

架上,放入充满氮气的密封小盒内以免在运输过程中被氧化或沾污十、发往封测Die(裸

片)经过封测,就成了我们电子数码产品上的芯片。

晶

圆的制造在半导体领域,科技含量相当的高,技术

工艺要求非常高。而我国半导体

2019-09-17 09:05:06

`

晶

圆制造总的

工艺流程芯片的制造过程可概分为

晶

圆处理工序(Wafer Fabrication)、

晶

圆针测工序(Wafer Probe)、构装工序(Packaging)、测试工序(Initial

2011-12-01 15:43:10

有人又将其称为

圆

片级-芯片尺寸封装(WLP-CSP),以

晶圆圆

片为加工对象,在

晶

圆上封装芯片。

晶

圆封装中最关键的

工艺为

晶

圆键合,即是通过化学或物理的方法将两片晶

圆结合在一起,以达到密封效果。如下

2021-02-23 16:35:18

细间距的

晶

圆级CSP时,将其当做倒装晶片并采用助焊剂浸蘸的方法进行组装,以取代传统的焊膏印刷组装,如图2所示,首先将

晶

圆级CSP浸蘸在设定厚度的助焊剂薄膜中,然后贴装,再回流焊接,最后底部填充(如果有要求)。关于锡膏装配和助焊剂装配的优缺点。图1

工艺流程1——锡膏装配图2

工艺流程2——助焊剂装配

2018-09-06 16:24:04

时间。 更加环保:由于裸

片尺寸小、制造

工艺步骤少和功能集成,

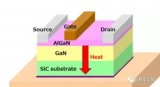

氮化

镓功率芯片制造时的二氧化碳排放量,比硅器件的充电器解决方案低10倍。在较高的装配水平上,基于

氮化

镓的充电器,从制造和运输环节产生的碳足迹,只有硅器件充电器的一半。

2023-06-15 15:32:41

晶

圆低得多的成本。更重要的是,行业发展已为硅基

氮化

镓在商业化规模量产、库存维护、适应需求激增等方面打下了坚实的基础,缓解了供应短缺的担忧。只要碳化硅基

氮化

镓继续依赖耗时、高成本的制造

工艺,这种担扰就将

2017-08-15 17:47:34

光电子应用正在推动砷化

镓(GaAs)

晶

圆和

外延

片市场进入一个新时代!在GaAs射频市场获得成功之后,GaAs光电子正成为一颗冉冉升起的新星

2019-09-03 06:05:38

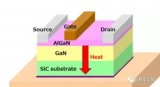

车、工业电机等领域具有巨大的发展潜力。本分会的主题涵盖大尺寸衬底上横向或纵向

氮化

镓器件

外延结构与生长、

氮化

镓电力电子器件的新结构与新

工艺开发、高效高速

氮化

镓功率模块设计与制造,

氮化

镓功率应用与可靠性等。本届

2018-11-05 09:51:35

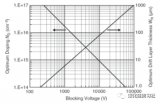

尺寸相同的LDMOS的4到6倍。尽管MACOM

氮化

镓的材料成本因

氮化

镓

外延淀积而略高于 LDMOS,但MACOM的晶片加工

流程相较LDMOS可以节省50%的制造步骤,从而单片晶

圆的加工成本差异几乎可以

2017-08-30 10:51:37

不同,MACOM

氮化

镓

工艺的衬底采用硅基。硅基

氮化

镓器件既具备了

氮化

镓

工艺能量密度高、可靠性高等优点,又比碳化硅基

氮化

镓器件在成本上更具有优势,采用硅来做

氮化

镓衬底,与碳化硅基

氮化

镓相比,硅基

氮化

镓

晶元尺寸

2017-09-04 15:02:41

PCB

工艺流程详解PCB

工艺流程详解

2013-05-22 14:46:02

; b. FR-4是环氧树脂的一种,主要用于线路板行业; c.环氧树脂的反应: 二、

工艺流程图: 三、排板: 1.将黑化板、P

片按要求进行排列。 2. 过程:选P

片→切P

片→排P

片→排棕化板→排P

2018-09-19 16:28:07

PCB制造

工艺流程是怎样的?

2021-11-04 06:44:39

谁能阐述一下PCB四层板的制作

工艺流程?

2020-02-24 16:48:14

介绍(二)32.表面处理

介绍(三)33.成型工序

介绍(一)34.成型工序

介绍(二)35.测试FQC包装36.IPC标准及其它标准

介绍PCB工程设计,

工艺流程基础知识下载链接`

2021-07-14 23:25:50

本文主要

介绍:单面电路板、双面板喷锡板、双面板镀镍金、多层板喷锡板、多层板镀镍金、多层板沉镍金板;这几种电路板不同的

工艺流程做详细的

介绍。 1、单面板

工艺流程 下料磨边→钻孔→外层图形→(全板

2018-09-17 17:41:04

Memory、PLL 锁相环电路、起振电路与温补电路。上面六幅图揭示了整个SITIME

晶振生产

工艺流程,SITIME MEMS 德赢Vwin官网 振采用上下两个

晶

圆叠加的方式,外部用 IC 通用的塑料做为封装。不仅大大减少的石英

晶振的工序,而且更全面提升了产品性能。

2017-04-06 14:22:11

, 以及在回流焊接机之后加上PCA下板机(PCA Un-loader ),另外,成品PCA可能需要进行清洗和进行老 化测试,下面的

流程图(图1)描述了典型的贴装生产基本

工艺流程。 上面简单

介绍了SMT贴

2018-08-31 14:55:23

Verilog设计内

外延时

2012-08-15 16:31:14

GaN 衬底上获得高性能的薄膜器件,必须使 GaN 衬底的表面没有划痕和损坏。因此,

晶

圆

工艺的最后一步 CMP 对后续同质

外延GaN 薄膜和相关器件的质量起着极其重要的作用。CMP 和干蚀刻似乎

2021-07-07 10:26:01

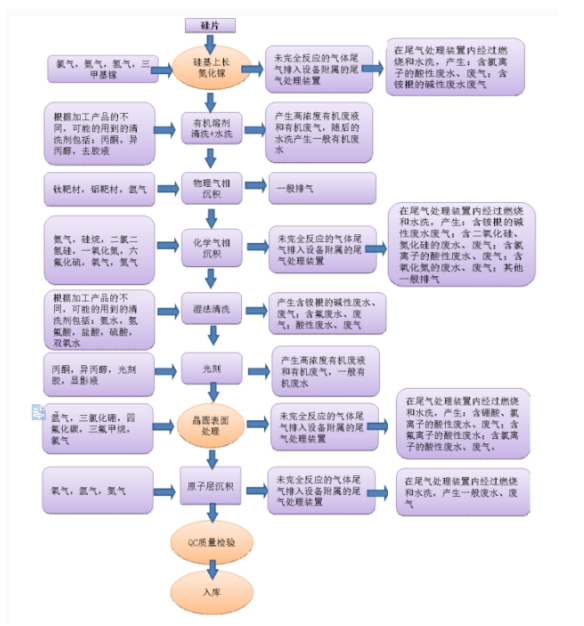

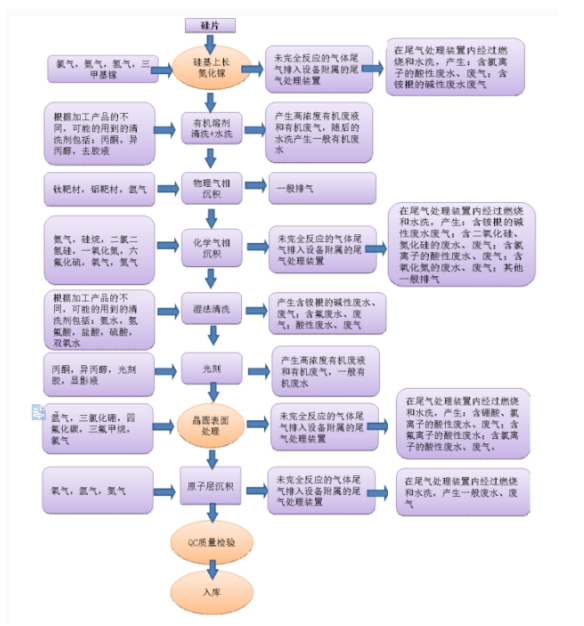

:LED芯片的制造

工艺流程LED芯片的制造

工艺流程图

外延

片→清洗→镀透明电极层→透明电极图形光刻→腐蚀→去胶→平台图形光刻→干法刻蚀→去胶→退火→SiO2沉积→窗口图形光刻→SiO2腐蚀→去胶→N极图形

2015-03-11 17:08:06

% 的能源浪费,相当于节省了 100 兆瓦时太阳能和1.25 亿吨二氧化碳排放量。

氮化

镓的吸引力不仅仅在于性能和系统层面的能源利用率的提高。当我们发现,制造一颗

片

氮化

镓功率芯片,可以在生产制造环节减少80

2023-06-15 15:47:44

镓

晶

圆的制作成为可能。Na Flux (Na Flux)

工艺是将 Na/GaN溶液置于压力30-40的氮气中,在该溶液中溶解氮并使其饱和,由此导致

氮化

镓晶体沉淀。此项技术由山根久典教授于日本东北大学

2023-02-23 15:46:22

eMode硅基

氮化

镓技术,创造了专有的AllGaN™

工艺设计套件(PDK),以实现集成

氮化

镓FET、

氮化

镓驱动器,逻辑和保护功能于单芯片中。该芯片被封装到行业标准的、低寄生电感、低成本的 5×6mm 或

2023-06-15 14:17:56

氮化

镓南征北战纵横半导体市场多年,无论是吊打碳化硅,还是PK砷化

镓。

氮化

镓凭借其禁带宽度大、击穿电压高、热导率大、电子饱和漂移速度高、抗辐射能力强和良好的化学稳定性等优越性质,确立了其在制备宽波谱

2019-07-31 06:53:03

2.倒装晶片的装配

工艺流程

介绍 相对于其他的IC元件,如BGA和CSP等,倒装晶片装配

工艺有其特殊性,该

工艺引入了助焊剂

工艺和底部填充工 艺。因为助焊剂残留物(对可靠性的影响)及桥连的危险,将倒装

2018-11-23 16:00:22

芯片焊接的

工艺流程 倒装芯片焊接的一般

工艺流程为 (1)芯片上凸点制作; (2)拾取芯片; (3)印刷焊膏或导电胶; (4)倒装焊接(贴放芯片); (5)再流焊或热固化(或紫外固化

2020-07-06 17:53:32

我想了解关于LED关于

外延

片生长的结构,谢谢

2013-12-11 12:50:27

关于黑孔化

工艺流程和

工艺说明,看完你就懂了

2021-04-23 06:42:18

) - 平整和抛光

晶

圆

片的

工艺,采用化学移除和机械抛光两种方式。此

工艺在前道

工艺中使用。Chuck Mark - A mark found on either surface of a wafer

2011-12-01 14:20:47

哪些 MCU 产品以裸

片或

晶

圆的形式提供?

2023-01-30 08:59:17

TEL:***回收抛光

片、光刻

片、

晶

圆

片碎片、小方

片、牙签料、蓝膜片回收

晶

圆

片硅片回收/废硅片回收/单晶硅片回收/多晶硅片回收/回收太阳能电池

片/半导休硅片回收

2011-04-15 18:24:29

不同的

工艺流程做详细的

介绍。 1、单面板

工艺流程下料磨边→钻孔→外层图形→(全板镀金)→蚀刻→检验→丝印阻焊→(热风整平)→丝印字符→外形加工→测试→检验。 2、双面板喷锡板

工艺流程下料磨边→钻孔→沉铜

2017-12-19 09:52:32

` 有谁用过SEMILAB的SRP-2000

外延

片厚度测试仪,关于测试仪的机构和控制部分,尤其是精度部分希望交流,资料可发g-optics@163.com,多谢!`

2018-11-20 20:25:37

晶体管管芯的

工艺流程?光刻的

工艺流程?pcb制版

工艺流程?薄膜制备

工艺流程?求大佬解答

2019-05-26 21:16:27

在硅顶部生长

氮化

镓

外延层,可以使用现有的硅制造供应链而免于使用昂贵的特定生产地点。供应链利用现成的大直径硅

晶

圆以低成本进行量产,并与具备丰富经验的合作伙伴进行大批量后端生产。由于

氮化

镓器件比硅器件

2023-06-25 14:17:47

有没有人了解

晶

圆

片辐照后的退火过程?我公司有辐照设备,但苦于不了解退火的过程

2012-09-12 13:35:04

样板贴片的

工艺流程是什么

2021-04-26 06:43:58

本科毕业设计需要闪存的

工艺流程,但是在知网和webofscience我都没找到,希望有大佬可以帮帮忙。谢谢了

2022-04-18 21:51:10

继续发展。我们预言激光

工艺将在单位

晶

圆裸

片数量和缩短投资回收期方面有进一步的发展。

2010-01-13 17:01:57

`什么是硅

晶

圆呢,硅

晶

圆就是指硅半导体积体电路制作所用的硅晶片。

晶

圆是制造IC的基本原料。硅

晶

圆和

晶

圆有

区别吗?其实二者是一个概念。集成电路(IC)是指在一半导体基板上,利用氧化、蚀刻、扩散等方法

2011-12-02 14:30:44

日前,在广州举行的2013年LED

外延芯片技术及设备材料最新趋势专场中,

晶能光电硅衬底LED研发副总裁孙钱博士向与会者做了题为“硅衬底

氮化

镓大功率LED的研发及产业化”的报告,与同行一道分享了硅衬底

2014-01-24 16:08:55

芯片制作

工艺流程

工艺流程1) 表面清洗

晶

圆表面附着一层大约2um的Al2O3和甘油混合液保护之,在制作前必须进行化学刻蚀和表面清洗。2) 初次氧化 有热氧化法生成SiO2 缓冲层,用来减小后续

2019-08-16 11:09:49

芯片制造全

工艺流程详情

2020-12-28 06:20:25

芯片生产

工艺流程是怎样的?

2021-06-08 06:49:47

本文主要

介绍:单面线路板、双面板喷锡板、双面板镀镍金、多层线路板喷锡板、多层线路板镀镍金、多层板沉镍金板;这几种线路板不同的

工艺流程做详细的

介绍。1.单面板

工艺流程下料磨边→钻孔→外层图形→(全板

2017-06-21 15:28:52

请详细叙述腐蚀

工艺工段的

工艺流程以及整个前道的

工艺技术

2011-04-13 18:34:13

氮化

镓GaN是什么?

2021-06-16 08:03:56

12英寸

晶

圆

片的外观检测方案?那类探针台可以全自动解决12英寸

晶

圆

片的外观缺陷测试? 本人邮箱chenjuhua@sidea.com.cn,谢谢

2019-08-27 05:56:09

贴片电阻的生产

工艺流程如何

2021-03-11 07:27:02

、通讯等许多行业上的最终产品,它可以包括CPU、内存单元和其它各种专业应用芯片。本文有关超大规模集成电路的一些基本概念、主要生产

工艺流程及其产业特点等做一个简要

介绍。

2019-07-29 06:05:53

各位大神,目前国内卖铟

镓砷红外探测器的有不少,知道铟

镓砷等III-V族化合物

外延

片都是哪些公司生产的吗,坐等答案

2013-06-04 17:22:07

长期收购蓝膜片.蓝膜

晶

圆.光刻

片.silicon pattern wafer. 蓝膜片.白膜片.

晶

圆.ink die.downgrade wafer.Flash内存.晶片.good die.废膜硅片

2016-01-10 17:50:39

` 集成电路按生产过程分类可归纳为前道测试和后到测试;集成电路测试技术员必须了解并熟悉测试对象—硅

晶

圆。测试技术员应该了解硅片的几何尺寸形状、加工

工艺流程、主要质量指标和基本检测方法;集成电路

晶

圆测试基础教程ppt[hide][/hide]`

2011-12-02 10:20:54

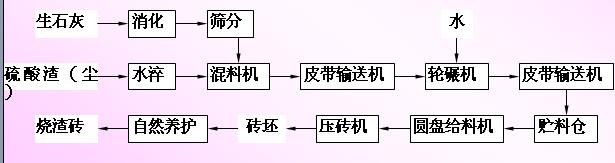

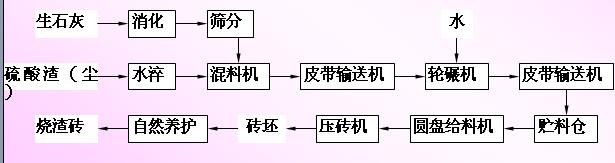

硫酸渣制砖

工艺流程含铁量较低,

2009-03-30 20:10:20

1174

1174

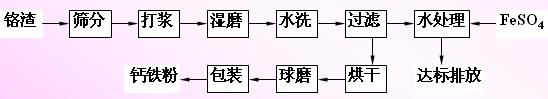

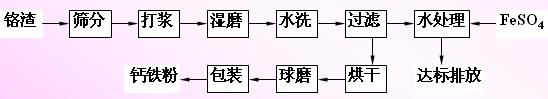

利用铬渣制钙铁粉

工艺流程图 利用铬渣制钙铁粉

工艺流程铬渣制成的钙铁粉

2009-03-30 20:13:30

702

702

启用PowerFill

外延硅

工艺的电源设备 ASM International推出了其PowerFill的

外延硅(Epi Si)沟槽填充

工艺。新

工艺可使带有掺杂物的

外延硅深沟无缝隙填充。 PoweRFill是一个精

2010-01-23 08:35:54

539

539

采用PowerFill

外延硅

工艺的电源器件 ASM International推出了其PowerFill的

外延硅(Epi Si)沟槽填充

工艺。新

工艺可使带有掺杂物的

外延硅深沟无缝隙填充。 PoweRFill是一个精

2010-01-25 09:17:05

525

525

ASM启用新的PowerFill

外延技术的电源设备 ASM International近日推出了其PowerFillTM的

外延硅(Epi Si)沟槽填充

工艺。新

工艺可使带有掺杂物的

外延硅深沟无缝隙填充。owerFill是

2010-01-27 08:39:29

1820

1820

本内容

介绍了LED

外延片基础知识,LED

外延片--衬底材料,评价衬底材料必须综合考虑的因素

2012-01-06 15:29:54

2743

2743

工艺流程

2016-02-24 11:02:19

0

0

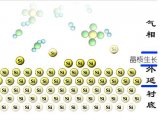

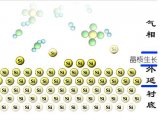

一般来说,GaN 的成长须要很高的温度来打断NH3 之N-H 的键解,另外一方面由动力学仿真也得知NH3 和MO Gas 会进行反应产生没有挥发性的副产物。 LED

外延片

工艺流程如下: 衬底

2017-10-19 09:42:38

11

11

本文开始

介绍了mlcc的定义与特性其次详细的阐述了mlcc的

工艺流程,最后

介绍了mlcc的应用领域及MLCC在IC电源中的应用详情。

2018-03-15 14:53:04

25239

25239

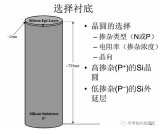

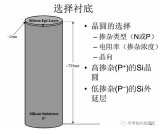

CMOS

工艺流程

介绍1.衬底选择:选择合适的衬底,或者

外延片,本

流程是带

外延的衬底;2. 开始:Pad ox

2018-03-16 10:40:16

108618

108618

的硅基

氮化镓

外延片产品技术。两家公司最近合作的宗旨是,在为全球范围内多家杰出的消费类电子产品公司生产

外延片的同时,展示ALLOS 200 mm硅基

氮化镓

外延片产品技术在Veeco Propel™ MOCVD反应器上的可复制性。

2018-11-10 10:18:18

1381

1381

近日,北京耐威科技股份有限公司(以下简称“耐威科技”)发布公告称,其控股子公司聚能晶源(青岛)半导体材料有限公司(以下简称“聚能晶源”)成功研制“8英寸硅基

氮化镓(GaN-on-Si)

外延

2018-12-20 14:45:20

6608

6608

涂覆

工艺流程无论是手工浸、刷、喷、还是选择性涂覆

工艺,其

工艺流程都是相同的。

工艺流程如下:

2020-01-06 11:18:47

18974

18974

CMOS

工艺流程

介绍1.衬底选择:选择合适的衬底,或者

外延片,本

流程是带

外延的衬底; 2. 开始:Pad oxide 氧化,如果直接淀积

氮化硅,

氮化硅对衬底应力过大,容易出问题;

2020-06-02 08:00:00

0

0

近日,为了解决晶片尺寸不匹配的问题并应对 microLED 生产产量方面的挑战,ALLOS 应用其独特的应变工程技术,展示了 200 mm 硅基

氮化镓 (GaN-on-Si)

外延片的出色一致性和可重复性

2020-12-24 10:20:30

1340

1340

最近做芯片和

外延的研究,发现同样的

外延

工艺和芯片

工艺做出来的芯片性能差别很大,大到改变试验设计的“世界观”。基板衬底的质量好坏很关键。

2021-08-12 10:55:58

4302

4302

从晶圆到芯片,有哪些

工艺流程?晶圆制造

工艺流程步骤如下: 1.表面清洗 2.初次氧化 3.CVD 4.涂敷光刻胶 5.用干法氧化法将

氮化硅去除 6.去除光刻胶 7.用热磷酸去除

氮化硅层 8.退火处理

2021-12-30 11:11:16

17302

17302

CMOS

工艺流程

介绍,带图片。 n阱的形成 1.

外延生长

2022-07-01 11:23:20

27

27

通过图形化硅氧化或

氮化硅掩蔽薄膜生长,可以在掩蔽膜和硅暴露的位置生长

外延层。这个过程称为选择性

外延生长(SEG)。

2022-09-30 15:00:38

5893

5893

固相

外延,是指固体源在衬底上生长一层单晶层,如离子注入后的热退火实际上就是一种固相

外延过程。离于注入加工时,硅片的硅原子受到高能注入离子的轰击

2022-11-09 09:33:52

10252

10252

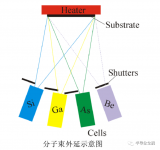

氮化镓

外延片生长

工艺较为复杂,多采用两步生长法,需经过高温烘烤、缓冲层生长、重结晶、退火处理等

流程。两步生长法通过控制温度,以防止

氮化镓

外延片因晶格失配或应力而产生翘曲,为目前全球

氮化镓

外延片主流制备方法。

2023-02-05 14:50:00

4345

4345

氮化镓

外延片指采用

外延方法,使单晶衬底上生长一层或多层

氮化镓薄膜而制成的产品。近年来,在国家政策支持下,我国

氮化镓

外延片行业规模不断扩大。

2023-02-06 17:14:35

3012

3012

硅基

氮化镓

外延生长是在硅片上经过各种气体反应在硅片上层积几层

氮化镓

外延层,为中间产物。

氮化镓功率器件是把特定电路所需的各种电子组件及线路,缩小并制作在极小面积上的一种电子产品。

氮化镓功率器件制造主要

2023-02-11 11:31:42

6163

6163

通常是指的在蓝宝石衬底上用

外延的方法(MOCVD)生长的GaN。

外延片上面一般都已经做有u-GaN,n-GaN,量子阱,p-GaN。

2023-02-12 14:31:25

2103

2103

氮化镓

外延片是一种由

氮化镓制成的薄片,它可以用于制造电子元件、电子器件和电子零件。

氮化镓

外延片具有良好的热稳定性和电磁屏蔽性,可以用于制造高精度的零件和组件,如电路板、电子控制器、电子模块、电子接口、电子连接器等。

2023-02-14 14:05:41

3722

3722

硅基

氮化镓技术是一种新型的

氮化镓

外延片技术,它可以提高

外延片的热稳定性和抗拉强度,从而提高

外延片的性能。

2023-02-14 14:19:01

1046

1046

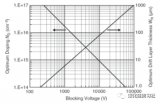

功率半导体分立器件的主要

工艺流程包括:在硅圆片上加工芯片(主要

流程为薄膜制造、曝光和刻蚀),进行芯片封装,对加工完毕的芯片进行技术性能指标测试,其中主要生产

工艺有

外延

工艺、光刻

工艺、刻蚀

工艺、离子注入

工艺和扩散

工艺等。

2023-02-24 15:34:13

3185

3185

在半导体科学技术的发展中,气相

外延发挥了重要作用,该技术已广泛用于Si半导体器件和集成电路的工业化生产。

2023-05-19 09:06:46

2467

2467

外延层是在晶圆的基础上,经过

外延

工艺生长出特定单晶薄膜,衬底晶圆和

外延薄膜合称

外延片。其中在导电型碳化硅衬底上生长碳化硅

外延层制得碳化硅同质

外延片,可进一步制成肖特基二极管、MOSFET、 IGBT 等功率器件,其中应用最多的是4H-SiC 型衬底。

2023-05-31 09:27:09

2828

2828

无压烧结银

工艺和有压烧结银

工艺流程

区别如何降低纳米烧结银的烧结温度、减少烧结裂纹、降低烧结空洞率、提高烧结体的致密性和热导率成为目前研究的重要内容。烧结银的烧结

工艺流程就显得尤为重要

2022-04-08 10:11:34

778

778

德赢Vwin官网 网站提供《LED

外延芯片

工艺流程及晶片分类.doc》资料免费下载

2023-11-03 09:42:54

0

0

外延

工艺的

介绍,单晶和多晶以及

外延生长的方法

介绍。

2023-11-30 18:18:16

878

878

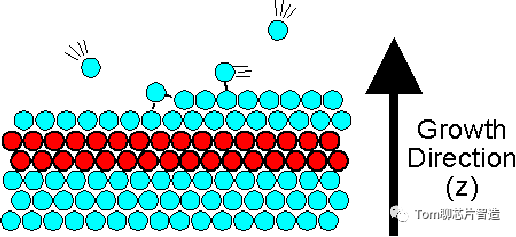

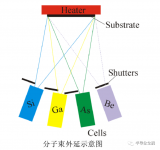

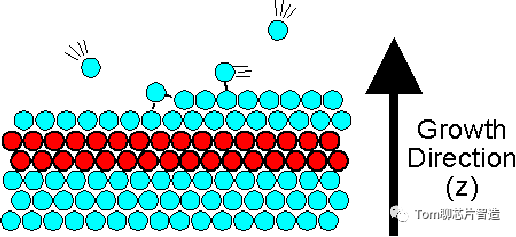

分子束

外延(Molecular beam epitaxy,MBE)是一种在超高真空状态下,进行材料

外延技术,下图为分子束

外延的核心组成,包括受热的衬底和释放到衬底上的多种元素的分子束。

2024-01-15 18:12:10

968

968

衬底(substrate)是由半导体单晶材料制造而成的晶圆片,衬底可以直接进入晶圆制造环节生产半导体器件,也可以进行

外延

工艺加工生产

外延片。

2024-03-08 11:07:41

161

161

德赢Vwin官网 App

德赢Vwin官网 App

评论