大规模多重输入多重输出(Massive MIMO)是一个非常有趣的5G无线研究领域。因为其可针对新一代无线数据网络提供多方面的优势,比如说以更高的数据传输率容纳更多用户,加强稳定度之余,还可降低耗电量。

只要使用大规模MIMO应用架构,研究人员可透过系统设计软件如LabVIEW和软件定义无线电(SDR),打造出一百二十八支天线的MIMO测试台,迅速制作大规模的天线系统原型。由于现场可编程门阵列(FPGA)架构逻辑的设计流程经过简化,高效能处理的部署过程也很顺畅,所以该领域的研究人员可以透过一致的软硬件设计流程,满足这类超复杂系统的原型制作需求。

采大量天线 大规模MIMO提升无线数据传输率

行动装置的数量和所消耗的无线资料量持续激增,促使研究人员须投入新技术的研究,才能满足不断成长的需求。新一代5G无线数据网络必须搭配目前的通讯系统,克服容量限制、网络稳定性、覆盖范围、能源效率和延迟时间等难题。

大规模MIMO为5G的候选技术,在基地台收发站(BTS)采用大量的天线(超过六十四支),能够大幅提升无线数据传输率和链接稳定性。现有标准的BTS架构采用分区拓扑,最多也只有八支天线。

大规模MIMO囊括数百个天线组件,可透过预先编码技巧把能源集中在目标行动用户身上,进一步降低辐射。只要把无线能源导向特定的用户,就能够降低辐射,同时也可避免干扰其他使用者。

就目前受干扰限制的行动网络而言,这是相当吸引人的一点。如果大规模MIMO确实能提供上述效能,未来的5G网络就会变得更快、可容纳更多使用者,提供更出色的稳定性和能源效率。

由于大规模MIMO的天线组件数量很多,也带来了目前网络所没有的系统难题。举例来说,就目前采用LTE或LTE-Advanced的进阶数据网络而言,导引讯号负载(Pilot Overhead)必须和天线数量成比例。

大规模MIMO会透过通道互惠在上行和下行链路之间使用分时双工(TDD),借此管理大量天线的负载。有了信道互惠,即可把上行导引讯号的信道状态信息用于下行预先编码器。实践大规模MIMO的困难之处还包含了扩充十倍的数据总线和接口,或是在大量的独立射频(RF)收发器之间达到更多也更分散的同步化效能。

正因为这些时序、处理和数据收集难题,所以原型制作便显得更重要。如果研究人员要检验理论内容,就得从理论研究转向测试台。只要在实际情境中使用实际波形,研究人员即可开发原型,判断大规模MIMO的可行性和商用价值。就像所有的全新无线标准或技术一样,从概念转移至原型确实会影响实际的部署和商品化程序。

SDR搭配系统设计软件 MIMO系统架构弹性大跃进

完整的大规模MIMO系统应用架构须包含必备的软硬件,借此打造出多功能、可扩充及灵活有弹性的大规模MIMO测试台,以便透过重点频带与带宽提供实时的双向通讯效能给研究社群。

图1 瑞典隆德大学的大规模MIMO测试台采用了USRP RIO(a)和客制化的交叉极化平面天线数组(b)。

借由SDR和系统设计软件,就可以发挥MIMO系统的模块化特性,把数个节点扩充为一百二十八支天线的大规模MIMO系统。透过灵活有弹性的硬件,即可随着无线研究需求变化而重新部署至其他设定,比如说做为分布式节点部署于随建即连(Ad-hoc)网络,也可做为多细胞协调网络。

瑞典隆德大学(Lund University)Ove Edfors和Fredrik Tufvesson教授采用大规模MIMO应用架构,与美商国家仪器(NI)合作开发出全球最大的MIMO系统(图1)。该系统用了五十个SDR,打造出一百支天线的大规模MIMO BTS设定,如表1所示。

NI和隆德大学的研究团队根据SDR的概念,使用类似LTE的物理层和TDD开发出系统软件和物理层,借此提供行动存取功能。这次合作所开发出来的软件已成为大规模MIMO应用架构的软件组件。

就像其他的通讯网络一样,大规模MIMO系统包含BTS和客户端设备(UE)或行动使用者。事实上,大规模MIMO主要是为了行动应用而设计的,包含BTS、UE或行动使用者。然而,大规模MIMO和传统的拓扑很不一样,主要差别在于配置大量的BTS天线,能够同时和多个UE通讯。

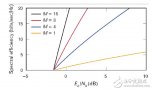

就NI和隆德大学合作开发的系统而言,BTS的系统设计针对每个UE提供十个基地台天线组件,可供十个使用者以完整带宽同时存取一百个天线基地台。经过证实,每个UE有十个基地台天线的设计有助于提高理想增益。

大规模MIMO系统内有一组UE会同时把一组正交导引讯号传输至BTS。接着就可以使用收到的上行导引讯号来评估信道矩阵,在下行时槽内,这项通道评估会用于计算下行讯号的预先编码器。

理论上,每个行动使用者即可透过无干扰的通道接收专属于自己的讯息。预先编码器设定是一种开放的研究领域,可针对不同的系统设计目标加以设计,举例来说,预先编码器可设计为对其他使用者零干扰、尽可能降低辐射功率,也可减少所传输射频讯号的峰均功率比。

透过上述设计,大规模MIMO应用架构可支持高达20MHz的瞬间实时带宽,并从六十四支天线扩充为一百二十八支,还能够提供给多个独立UE使用。表1是在此环境下,部署类似LTE协议的参数状态,其中采用一个2,048个点的快速傅立叶变换(FFT)和0.5毫秒的时槽。0.5毫秒的时槽可确保合适的通道和谐状态,提高行动测试情境(也就是UE移动中)的通道互惠效能。

大规模MIMO系统的四大设计关键如下。

‧ 灵活的SDR,可撷取并传输射频讯号。

‧ 无线电站之间可达到准确的时间与频率同步化。

‧ 高输出率的精确总线,可迁移并汇整大量的数据。

‧ 出色的处理效能,可用于物理层和媒体访问控制(MAC)执行,借此满足实时效能需求。

理论上,这些关键项目可针对不同的研究需求快速完成客制化。本文的应用架构集结了SDR、频率分配模块、高输出率PXI系统和LabVIEW,提供稳健又精确的原型制作平台,进一步满足研究需求。其中,SDR透过一个半宽1U、机架安装式的机壳,提供整合式2×2 MIMO收发器和高效能FPGA,有助于加速基频处理作业(图2)。此外,其可透过PCI Express×4连接至主机控制器和系统控制器,能够以高达800Mbit/s的数据串流速度传输至桌上型或PXI Express主计算机,或透过ExpressCard以200Mbit/s的速度传输至笔记本电脑。

图2 USRP RIO硬件(a)和系统方块图(b)

上述的SDR硬件名为USRP RIO,搭载LabVIEW可重设I/O(RIO)架构,其中结合开放式的系统设计软件和高效能硬件,有助于大幅简化开发作业。紧密的软硬件整合能够降低系统整合的难度,对于如此大规模的系统更是如此,可以让研究人员致力于研究项目。

PXI Express机箱背板

大规模MIMO应用架构采用PXIe-1085这款进阶的18槽式PXI机箱,其中每个插槽皆搭载PCI Express Generation 2技术,可达到高输出、低延迟的应用效能。此机箱可提供4Gbit/s的单插槽带宽、12Gbit/s的系统带宽。

图3 18槽式PXIe-1085机箱(a)和系统方块图(b)

图3为双切换器背板架构。如要建置高信道数系统,可透过菊链方式把多个PXI机箱串联在一起,也可放入星形设定。

高效能可重设FPGA处理模块

大规模MIMO应用架构采用FPGA模块如FlexRIO,在PXI机箱中加入灵活高效能的处理模块,透过LabVIEW FPGA Module即可设计程序。该FPGA模块可独立使用,提供客制化的大型Xilinx Kintex-7 410T和PCI Express Generation 2×8联机功能给PXI Express背板。

八通道频率同步化

另外,OctoClock频率分配模块具有八个信道,可以八种方式透过长度匹配轨迹放大并分割一个外部10MHz参考和每秒脉波数(PPS)讯号,进一步提供频率和时间同步化效能给最多八个USRP装置。

图4 OctoClock-G模块(a)和系统方块图(b)

OctoClock-G使用全球卫星定位系统(GPS)授时的振荡器(GPSDO),额外加入一个内部的时间与频率参考,图4为OctoClock-G系统简图。正面板的切换器可让使用者选择内部GPSDO和外部参考。

LabVIEW系统设计环境

LabVIEW具备整合式工具流,有助于管理系统层级的软硬件细节;透过GUI显示系统信息;开发通用处理器(GPP)、Real-Time和FPGA程序代码;并且把程序代码部署至研究测试台。有了LabVIEW,用户即可整合额外的程序设计语言,包含ANSI C/C++(透过呼叫库节点)、VHDL(透过IP整合节点),甚至是.m档案指令(透过LabVIEW MathScript RT Module)。这样一来即可开发出高效能实作项目,兼顾出色的稳定性和客制化功能。大规模MIMO应用架构运用了LabVIEW的高生产力特性,以及可透过LabVIEW FPGA设计并控制I/O细节的功能。

PXI机箱满足大数据输出需求

上述的软硬件平台元素组合成一个测试台,可把数支天线扩充为超过一百二十八支同步化天线,该天线系统囊括了六十四个双信道SDR装置,连接至四个设为星形架构的PXI机箱。主机箱可汇整所有数据,以便透过FPGA处理器和搭载四核心英特尔(Intel)i7的PXI控制器集中处理这些数据。

图5 PXIe-7976R FlexRIO模块(a)和系统方块图(b)

如图5所示,主机箱把PXIe-1085机箱做为主要的数据汇整节点和实时讯号处理引擎。PXI机箱提供了十七个开放式插槽可用于输入/输出装置,此外还有时序与同步化、可实时处理讯号的FlexRIO FPGA机板、可连接至子机箱的扩充模块。

图6 可扩充的大规模MIMO系统方块图结合PXI和USRP RIO。

一百二十八支天线的大规模MIMO BTS需要出色的数据输出效能,才能够汇整并处理I/Q样本,进而透过一百二十八个信道实时完成收发作业;市面上的PXIe机箱如PXIe-1085则可确实满足此需求,支持的PCI Generation 2×8数据路径能够达到最高3.2GB/s的输出率(图6)。

在主机箱的Slot 1内,PXIe-8135 RT控制器或嵌入式计算机可做为中央系统控制器。PXIe-8135 RT配备2.3GHz的四核心Intel Core i7处理器(单核心Turbo Boost模式可达3.3GHz)。

主机箱装载了四个PXIe-8384(S1到S4)接口模块,可以把子机箱连接至主系统。机箱之间的通讯除了透过MXI之外,还仰赖了PCI Express Generation 2×8,可以在主机箱和其他子节点之间提供高达3.2GB/s的效能。

此系统还配备最多八个FPGA模块,可满足大规模MIMO系统的实时讯号处理需求;插槽位置提供一个范例设定,其中的FPGA可以串联起来,支持每个子节点的数据处理需求。每个FPGA模块都可以彼此透过背板接收或传输资料,甚至可以连接所有的SDR,延迟时间不到5微秒、输出率高达3GB/s。

时序和同步化至关重要

如果系统要部署大量的无线电,时序和同步化都很重要,这都是大规模MIMO系统的关键。BTS系统共享一个10MHz参考频率和一个数字触发器,可启动每个无线电的撷取或产生功能,确保整个系统的同步化效能(图7)。

图7 大规模MIMO 频率分配方块图

PXIe-6674T时序和同步化模块配备OCXO,位于主机箱的Slot 10,可产生稳定又准确的10MHz参考频率(50ppb准确度),并提供数字触发器让装置与主要OctoClock-G频率分配模块达成同步化。

接着OctoClock-G就会供应并缓冲10MHz参考(MCLK)和触发器(MTrig)给OctoClock模块,从第一个到第八个依序完成,然后供应至SDR装置,借此确保每条天线都可以共享10MHz参考频率和主机触发器。此外,上述的控制架构可针对每个无线电/天线组件提供精确的控制功能。

基地台应用架构软件是专门为了满足表1所述的系统目标而设计的,OFDM物理层处理功能会分配至SDR装置的FPGA内,MIMO物理层处理组件则会分配至PXI主机箱的FPGA。

更高阶的MAC函式会在PXI控制器上、Intel为架构的通用处理器(GPP)上执行。此系统架构有助于处理大量资料,同时降低延迟以维持信道互惠效能预先编码参数会直接从接收器传送至传输器,借此优化系统效能。

从天线开始,OFDM物理层处理会在FPGA上执行,这样一来,需要最大量运算资源的处理作业就会在天线附近执行。这样的运算结果就会在MIMO接收器IP结合起来,替每个使用者和每个子载波解析信道信息。

算出来的通道参数会传输至MIMO TX区块,预先编码会在此套用,把能源集中在单一用户的退回路径。虽然MAC有些部分会实作于FPGA,大部分和其他较上层的处理都会实作于GPP。系统每个阶段所使用的特定算法也是相当活跃的研究领域。

UE就是具有单一输入单一输出(SISO)或2×2 MIMO无线功能的手机,或其他无线装置。UE原型可采用市面上的SDR,配备整合式GPSDO,使用接线PCI Express把笔记本电脑连接至ExpressCard(图8)。

图8 标准的UE设定,搭配笔记本电脑和USRP RIO

事实上,GPSDO非常重要,因为它提供更出色的频率准确度,还可提供同步化和地理位置功能,满足未来的系统扩充需求。典型的测试台实作可能包含多个UE系统,其中每个SDR可能代表一或两个UE装置。

UE上的软件实作方式就像BTS一样,然而此软件会做为单一天线系统而实作,把物理层放在SDR的FPGA,把MAC层放在主机PC。

PXI平台推进5G研究时程

透过LabVIEW系统设计软件搭配USRP RIO和PXI平台,彻底改革了高阶研究系统的原型制作方式。本文说明一个建置大规模MIMO系统的实用选项,有助于促进未来的5G研究。

把如此独一无二的NI技术组合用于应用架构,即可针对大量的无线电同步化时间和频率,PCI Express基础架构也可满足输出需求,借此以超过15.7GB/s的速度,在上行和下行传输并汇整I/Q样本。FPGA的设计流程可简化物理层和MAC层的高效能处理作业,满足实时的时序需求。

责任编辑:gt

德赢Vwin官网

App

德赢Vwin官网

App

评论