pcb布线规则,布板需要注意的点很多,但是基本上注意到了下面的这此规则,LAYOUT PCB应该会比较好,不管是高速还是低频电路,都基本如此。

1.一般规则

1.1 PCB板上预划分数字、vwin 、DAA信号布线区域。

1.2数字、模拟元器件及相应走线尽量分开并放置於各自的布线区域内。

1.3高速数字信号走线尽量短。

1.4敏感模拟信号走线尽量短。

1.5合理分配电源和地。

1.6 DGND、AGND、实地分开。

1.7电源及临界信号走线使用宽线。

1.8数字电路放置於并行总线/串行DTE接口附近,DAA电路放置於电话线接口附近。

2.元器件放置

2.1在系统电路原理图中:

a)划分数字、模拟、DAA电路及其相关电路;

b)在各个电路中划分数字、模拟、混合数字/模拟元器件;

2.2初步划分数字、模拟、DAA电路在PCB板上的布线区域(一般比例2/1/1),数字、模拟元器件及其相应走线尽量远离并限定在各自的布线区域内。

Note:当DAA电路占较大比重时,会有较多控制/状态信号走线穿越其布线区域,可根据当地规则限定做调整,如元器件间距、高压抑制、电流限制等。

2.3初步划分完毕後,从Connector和Jack开始放置元器件:

a) Connector和Jack周围留出插件的位置;

b)元器件周围留出电源和地走线的空间;

c) Socket周围留出相应插件的位置。

2.4首先放置混合型元器件(如Modem器件、A/D、D/A转换芯片等):

a)确定元器件放置方向,尽量使数字信号及模拟信号引脚朝向各自布线区域;

b)将元器件放置在数字和模拟信号布线区域的交界处。

2.5放置所有的模拟器件:

a)放置模拟电路元器件,包括DAA电路;

b)模拟器件相互靠近且放置在PCB上包含TXA1、TXA2、RIN、VC、VREF信号走线的一面;

c) TXA1、TXA2、RIN、VC、VREF信号走线周围避免放置高噪声元器件;

d)对於串行DTE模块,DTE EIA/TIA-232-E

系列接口信号的接收/驱动器尽量靠近Connector并远离高频时钟信号走线,以减少/避免每条线上增加的噪声抑制器件,如阻流圈和电容等。

2.6放置数字元器件及去耦电容:

a)数字元器件集中放置以减少走线长度;

b)在IC的电源/地间放置0.1uF的去耦电容,连接走线尽量短以减小EMI;

c)对并行总线模块,元器件紧靠

Connector边缘放置,以符合应用总线接口标准,如ISA总线走线长度限定在2.5in;

d)对串行DTE模块,接口电路靠近Connector;

e)晶振电路尽量靠近其驱动器件。

2.7各区域的地线,通常用0 Ohm电阻或bead在一点或多点相连。

3.信号走线

3.1 Modem信号走线中,易产生噪声的信号线和易受干扰的信号线尽量远离,如无法避免时要用中性信号线隔离。

Modem易产生噪声的信号引脚、中性信号引脚、易受干扰的信号引脚如下表所示:

3.2数字信号走线尽量放置在数字信号布线区域内;

模拟信号走线尽量放置在模拟信号布线区域内;

(可预先放置隔离走线加以限定,以防走线布出布线区域)

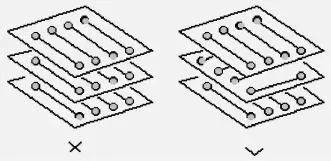

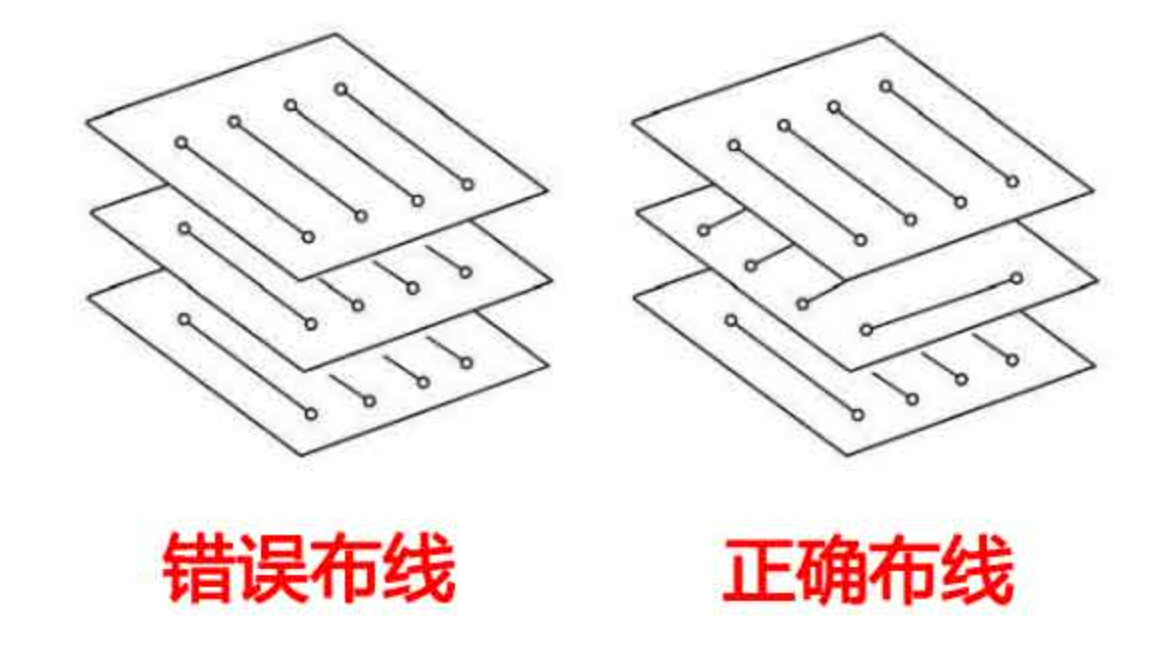

数字信号走线和模拟信号走线垂直以减小交叉耦合。

3.3使用隔离走线(通常为地)将模拟信号走线限定在模拟信号布线区域。

a)模拟区隔离地走线环绕模拟信号布线区域布在PCB板两面,线宽50-100mil;

b)数字区隔离地走线环绕数字信号布线区域布在PCB板两面,线宽50-100mil,其中一面PCB板边应布200mil宽度。

3.4并行总线接口信号走线线宽>10mil(一般为12-15mil),如/HCS、/HRD、/HWT、/RESET。

3.5模拟信号走线线宽>10mil(一般为12-15mil),如MICM、MICV、SPKV、VC、VREF、TXA1、TXA2、RXA、TELIN、TELOUT。

3.6所有其它信号走线尽量宽,线宽>5mil(一般为10mil),元器件间走线尽量短(放置器件时应预先考虑)。

3.7旁路电容到相应IC的走线线宽>25mil,并尽量避免使用过孔。

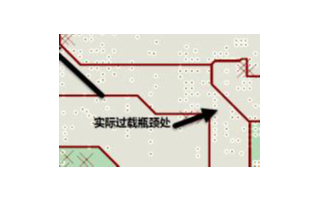

3.8通过不同区域的信号线(如典型的低速控制/状态信号)应在一点(首选)或两点通过隔离地线。如果走线只位於一面,隔离地线可走到PCB的另一面以跳过信号走线而保持连续。

3.9高频信号走线避免使用90度角弯转,应使用平滑圆弧或45度角。

3.10高频信号走线应减少使用过孔连接。

3.11所有信号走线远离晶振电路。

3.12对高频信号走线应采用单一连续走线,避免出现从一点延伸出几段走线的情况。

3.13 DAA电路中,穿孔周围(所有层面)留出至少60mil的空间。

3.14清除地线环路,以防意外电流回馈影响电源。

4.电源

4.1确定电源连接关系。

4.2数字信号布线区域中,用10uF电解电容或钽电容与0.1uF瓷片电容并联後接在电源/地之间.在PCB板电源入口端和最远端各放置一处,以防电源尖峰脉冲引发的噪声干扰。

4.3对双面板,在用电电路相同层面中,用两边线宽为200mil的电源走线环绕该电路。(另一面须用数字地做相同处理)

4.4一般地,先布电源走线,再布信号走线。

5.地

5.1双面板中,数字和模拟元器件(除DAA)周围及下方未使用之区域用数字地或模拟地区域填充,各层面同类地区域连接在一起,不同层面同类地区域通过多个过孔相连:Modem DGND引脚接至数字地区域,AGND引脚接至模拟地区域;数字地区域和模拟地区域用一条直的空隙隔开。

5.2四层板中,使用数字和模拟地区域覆盖数字和模拟元器件(除DAA);Modem DGND引脚接至数字地区域,AGND引脚接至模拟地区域;数字地区域和模拟地区域用一条直的空隙隔开。

5.3如设计中须EMI过滤器,应在接口插座端预留一定空间,绝大多数EMI器件(Bead/电容)均可放置在该区域;未使用之区域用地区域填充,如有屏蔽外壳也须与之相连。

5.4每个功能模块电源应分开。功能模块可分为:并行总线接口、显示、数字电路(SRAM、EPROM、Modem)和DAA等,每个功能模块的电源/地只能在电源/地的源点相连。

5.5对串行DTE模块,使用去耦电容减少电源耦合,对电话线也可做相同处理。

5.6地线通过一点相连,如可能,使用Bead;如抑制EMI需要,允许地线在其它地方相连。

5.7所有地线走线尽量宽,25-50mil。

5.8所有IC电源/地间的电容走线尽量短,并不要使用过孔。

6.晶振电路

6.1所有连到晶振输入/输出端(如XTLI、XTLO)的走线尽量短,以减少噪声干扰及分布电容对Crystal的影响。XTLO走线尽量短,且弯转角度不小於45度。(因XTLO连接至上升时间快,大电流之驱动器)

6.2双面板中没有地线层,晶振电容地线应使用尽量宽的短线连接至器件上离晶振最近的DGND引脚,且尽量减少过孔。

6.3如可能,晶振外壳接地。

6.4在XTLO引脚与晶振/电容节点处接一个100 Ohm电阻。

6.5晶振电容的地直接连接至Modem的GND引脚,不要使用地线区域或地线走线来连接电容和Modem的GND引脚。

7.使用EIA/TIA-232接口的独立Modem设计

7.1使用金属外壳。如果须用塑料外壳,应在内部贴金属箔片或喷导电物质以减小EMI。

7.2各电源线上放置相同模式的Choke。

7.3元器件放置在一起并紧靠EIA/TIA-232接口的Connector。

7.4所有EIA/TIA-232器件从电源源点单独连接电源/地。电源/地的源点应为板上电源输入端或调压芯片的输出端。

7.5 EIA/TIA-232电缆信号地接至数字地。

针对模拟信号,再作一些详细说明:

模拟电路的设计是工程师们最头疼、但也是最致命的设计部分,尽管目前数字电路、大规模集成电路的发展非常迅猛,但是模拟电路的设计仍是不可避免的,有时也是数字电路无法取代的,例如RF射频电路的设计!这里将模拟电路设计中应该注意的问题总结如下,有些纯属经验之谈,还望大家多多补充、多多批评指正!...

(1)为了获得具有良好稳定性的反馈电路,通常要求在反馈环外面使用一个小电阻或扼流圈给容性负载提供一个缓冲。

(2)积分反馈电路通常需要一个小电阻(约 560 欧)与每个大于 10pF 的积分电容串联。

(3)在反馈环外不要使用主动电路进行滤波或控制EMC的 RF 带宽,而只能使用被动元件(最好为 RC 电路)。仅仅在运放的开环增益比闭环增益大的频率下,积分反馈方法才有效。在更高的频率下,积分电路不能控制频率响应。

(4)为了获得一个稳定的线性电路,所有连接必须使用被动滤波器或其他抑制方法(如光电隔离)进行保护。

(5)使用 EMC 滤波器,并且与 IC 相关的滤波器都应该和本地的 0V 参考平面连接。

(6)在外部电缆的连接处应该放置输入输出滤波器,任何在没有屏蔽系统内部的导线连接处都需要滤波,因为存在天线效应。另外,在具有数字信号处理或开关模式的变换器的屏蔽系统内部的导线连接处也需要滤波。

(7)在模拟 IC 的电源和地参考引脚需要高质量的 RF 去耦,这一点与数字 IC 一样。但是模拟 IC 通常需要低频的电源去耦,因为模拟元件的电源噪声抑制比(PSRR)在高于 1KHz 后增加很少。在每个运放、比较器和数据转换器的模拟电源走线上都应该使用 RC 或 LC 滤波。电源滤波器的拐角频率应该对器件的 PSRR 拐角频率和斜率进行补偿,从而在整个工作频率范围内获得所期望的 PSRR 。

(8)对于高速模拟信号,根据其连接长度和通信的最高频率,传输线技术是必需的。即使是低频信号,使用传输线技术也可以改善其抗干扰性,但是没有正确匹配的传输线将会产生天线效应。

(9)避免使用高阻抗的输入或输出,它们对于电场是非常敏感的。

(10)由于大部分的辐射是由共模电压和电流产生的,并且因为大部分环境的电磁干扰都是共模问题产生的,因此在模拟电路中使用平衡的发送和接收(差分模式)技术将具有很好的 EMC 效果,而且可以减少串扰。平衡电路(差分电路)驱动不会使用 0V 参考系统作为返回电流回路,因此可以避免大的电流环路,从而减少 RF 辐射。

(11)比较器必须具有滞后(正反馈),以防止因为噪声和干扰而产生的错误的输出变换,也可以防止在断路点产生振荡。不要使用比需要速度更快的比较器(将 dV/dt 保持在满足要求的范围内,尽可能低)。

(12)有些模拟 IC 本身对射频场特别敏感,因此常常需要使用一个安装在 PCB 上,并且与 PCB 的地平面相连接的小金属屏蔽盒,对这样的模拟元件进行屏蔽。注意,要保证其散热条件。

德赢Vwin官网 App

德赢Vwin官网 App

评论