PCB布线设计时寄生电容的计算方法

- 电容(147007)

相关推荐

如何消除寄生电容的电路设计方案

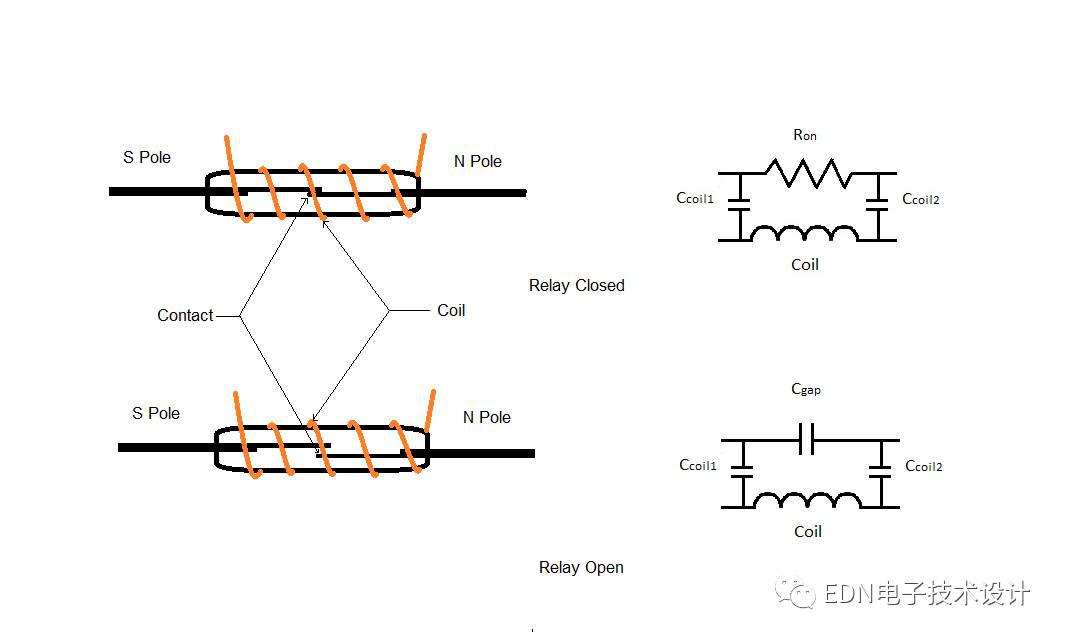

在被测点阻抗较高时,即使该点仅有较小的电容,其带宽也会受限。在基于磁簧继电器的多路选择器中,由于各磁簧继电器的寄生电容会在输出端并联,加大了输出端的电容,使得电路的带宽变窄。

2018-12-14 15:14:47 21352

21352

21352

21352

PCB布局的DC电阻,寄生电容和寄生电感

实际系统的很多方面都会在PCB布局,IC或任何其他电气系统中产生意外的寄生现象。重要的是在尝试使用SPICE仿真提取寄生效应之前,请注意电路图中无法考虑的内容。

2020-12-31 12:01:41 8249

8249

8249

8249

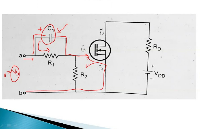

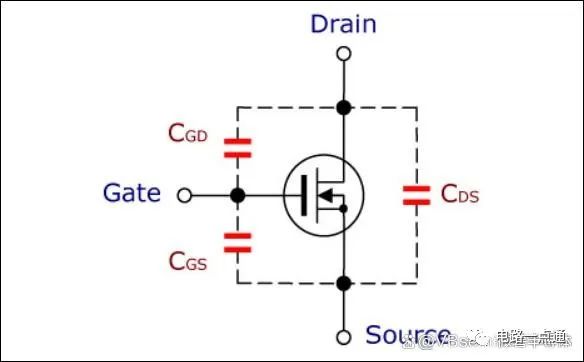

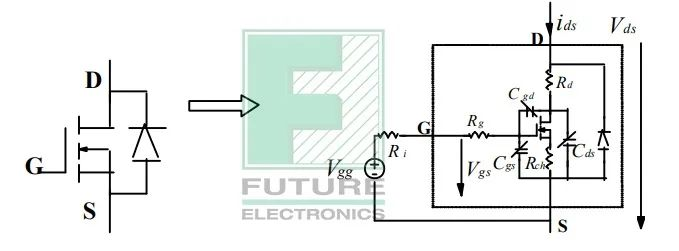

MOSFET寄生电容参数如何影响开关速度

我们应该都清楚,MOSFET 的栅极和漏源之间都是介质层,因此栅源和栅漏之间必然存在一个寄生电容CGS和CGD,沟道未形成时,漏源之间也有一个寄生电容CDS,所以考虑寄生电容时,MOSFET

2021-01-08 14:19:59 15830

15830

15830

15830

PCB杂散电容大小计算方法 PCB杂散电容怎么消除

在整个PCBA生产制造过程中, PCB 设计是至关重要的一部分,今天主要是关于 PCB 杂散电容、影响PCB 杂散电容的因素,PCB 杂散电容计算,PCB杂散电容怎么消除。

2023-09-11 09:41:20 770

770

770

770

PCB寄生电容的影响 PCB寄生电容计算 PCB寄生电容怎么消除

寄生电容有一个通用的定义:寄生电容是存在于由绝缘体隔开的两个导电结构之间的虚拟电容(通常不需要的),是PCB布局中的一种效应,其中传播的信号表现得好像就是电容,但其实并不是真正的电容。

2024-01-18 15:36:14 866

866

866

866

PCB布线

布线需要考虑的问题很多,但是最基本的的还是要做到周密,谨慎。 寄生元件危害最大的情况 印刷电路板布线产生的主要寄生元件包括:寄生电阻、寄生电容和寄生电感。例如:PCB的寄生电阻由元件之间的走

2011-11-06 14:32:56

PCB布线设计(三)

PCB布线设计(三)印刷电路板布线产生的主要寄生元件包括:寄生电阻、寄生电容和寄生电感。例如:PCB的寄生电阻由元件之间的走线形成;电路板上的走线、焊盘和平行走线会产生寄生电容;寄生电感的产生途径

2017-11-10 10:02:54

PCB布线设计(三)

布线需要考虑的问题很多,但是最基本的的还是要做到周密,谨慎。 寄生元件危害最大的情况 印刷电路板布线产生的主要寄生元件包括:寄生电阻、寄生电容和寄生电感。例如:PCB的寄生电阻由元件之间的走

2018-11-23 11:07:46

PCB布线设计-模拟和数字布线的异同

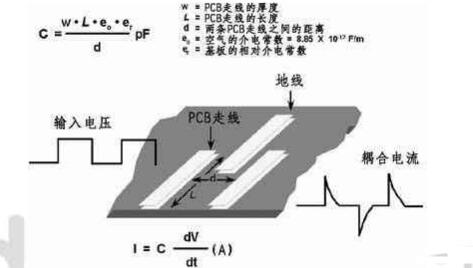

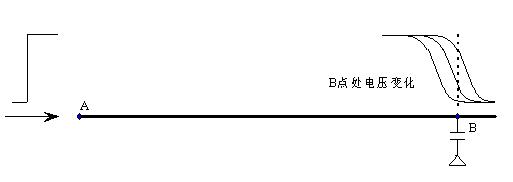

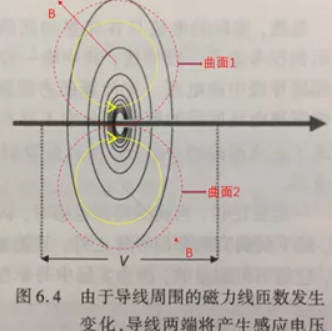

在PCB上布两条靠近的走线,很容易形成寄生电容。由于这种电容的存在,在一条走线上的快速电压变化,可在另一条走线上产生电流信号 图6 如果不注意走线的放置,PCB中的走线可能产生线路感抗和互感。这种

2011-09-02 09:36:14

pcb布线规则(2)

。很显然,在高速,高密度的PCB设计时,设计者总是希望过孔越小越好,这样板上可以留有更多的布线空间,此外,过孔越小,其自身的寄生电容也越小,更适合用于高速电路。但孔尺寸的减小同时带来了成本的增加,而且过孔

2015-07-24 12:29:05

寄生电容器是什么?

低频下,所有三种电容器均未表现出寄生分量,因为阻抗明显只与电容相关。但是,铝电解电容器阻抗停止减小,并在相对低频时开始表现出电阻特性。这种电阻特性不断增加,直到达到某个相对高频为止(电容器出现电感)。铝聚合物电容器为与理想状况不符的另一种电容器。

2019-08-15 06:33:32

寄生电容有什么含义?

寄生电容一般是指电感,电阻,芯片引脚等在高频情况下表现出来的电容特性。实际上,一个电阻等效于一个电容,一个电感,和一个电阻的串联,在低频情况下表现不是很明显,而在高频情况下,等效值会增大,不能忽略。

2019-09-29 10:20:26

LTC6268-10为了使寄生电容降到最低,对电路板的材料类型和厚度有什么要求吗?

在LTC6268-10芯片手册中,为了减小寄生反馈电容的影响,采用反馈电阻分流的方式减小寄生电容。

请问,在这种工作方式下,为了使寄生电容降到最低,对电路板的材料类型和厚度有什么要求吗?

2023-11-16 06:28:44

MOSFET寄生电容对LLC串联谐振电路ZVS的影响

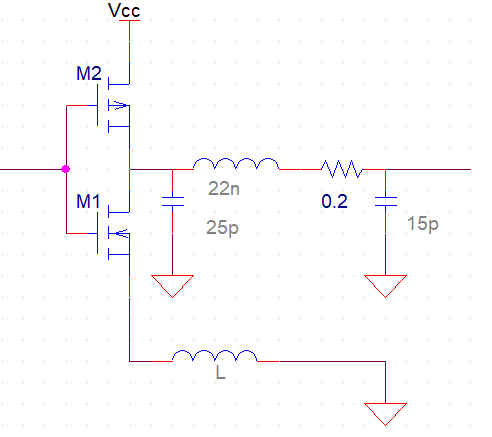

MOSFET的工作波形。由于感性负载下,电流相位上会超前电压,因此保证了MOSFET运行的ZVS。要保证MOSFET运行在感性区,谐振电感上的谐振电流必须足够大,以确保MOSFET源漏间等效的寄生电容上存储

2018-11-21 15:52:43

MOSFET寄生电容对LLC串联谐振电路ZVS的影响

感性负载下,电流相位上会超前电压,因此保证了MOSFET运行的ZVS。要保证MOSFET运行在感性区,谐振电感上的谐振电流必须足够大,以确保MOSFET源漏间等效的寄生电容上存储的电荷可以在死区时间内被

2018-07-13 09:48:50

mos管寄生电容是什么

寄生电容是指电感,电阻,芯片引脚等在高频情况下表现出来的电容特性。实际上,一个电阻等效于一个电容,一个电感,一个电阻的串联,低频情况下表现不明显,而高频情况下,等效值会增大。在计算中我们要考虑

2021-01-11 15:23:51

【我是德赢Vwin官网 】实现高速PCB之布线问题探讨(转)

问题的寄生源时,可能用得着几个计算上述那些寄生电容尺寸的基本公式。(公式一)是计算平行极板电容器的公式,如(图五)。(公式一)(1)C表示电容值;(2)A表示以cm2为单位的极板面积;(3)k表示PCB

2017-06-19 16:18:30

【转帖】PCB布线技巧

盘区。这两部分的尺寸大小决定了过孔的大小。很显然,在高速,高密度的PCB设计时,设计者总是希望过孔越小越好,这样板上可以留有更多的布线空间,此外,过孔越小,其自身的寄生电容也越小,更适合用于高速电路

2017-06-26 17:25:08

【高速PCB布线指南(2)】寄生效应

的公式(参见图8)。T表示PCB的厚度,d表示以cm为单位的通孔直径。公式(4)示出了如何计算通孔(参见图8)引起的寄生电容值。er表示PCB材料的相对磁导率。T表示PCB的厚度。D1表示环绕通孔的焊

2018-10-19 13:46:56

从实践角度来探讨高速电路布线问题

接地平面的脉冲响应通孔是另外一种寄生源,它们能引起寄生电感和寄生电容。公式(3)是计算寄生电感的公式。公式(3)中:T表示PCB的厚度,d表示以cm为单位的通孔直径。公式(4)是如何计算通孔

2019-12-16 09:21:50

关于车用BMS高压电路中做绝缘电阻检测时如何考虑高压正负极对地的寄生电容对AD采集影响?

在高压回路中,正负极对地会产生一个寄生电容,而寄生电容与回路中的电阻会组成一个RC充放电电路。在使用国标电流桥检测电路方法时,正负极对地的寄生电容和电阻的大小会影响到AD采集。在RC充满的时间一般为3RC以上,在此过程中如何探讨RC电路充满电压的时间?

2020-07-27 23:14:10

再读大牛的一篇经典好文章——实现高速PCB之布线问题探讨

减小寄生电感的影响。(图七) 有接地平面和没有接地平面的脉冲回应 通孔是另外一种寄生源;它们能引起寄生电感和寄生电容。(公式三)是计算寄生电感的公式,请参考(图八)。 (公式三)(1)T表示PCB

2018-08-10 08:56:18

如何处理好电源中的寄生电容获得符合EMI标准的电源?

从开关节点到输入引线的少量寄生电容(100毫微微法拉)会让您无法满足电磁干扰(EMI)需求。那100fF电容器是什么样子的呢?在Digi-Key中,这种电容器不多。即使有,它们也会因寄生问题而提

2019-05-14 08:00:00

实现高速PCB之布线问题探讨

源时,可能用得着几个计算上述那些寄生电容尺寸的基本公式。(公式一)是计算平行极板电容器的公式,如(图五)。 (公式一)(1)C表示电容值;(2)A表示以cm2为单位的极板面积;(3)k表示PCB材料

2018-10-12 10:22:31

当寄生电容直接耦合到电源输入电线时会发生的情况分析

大部分传导 EMI 问题都是由共模噪声引起的。而且,大部分共模噪声问题都是由电源中的寄生电容导致的。对于该讨论主题的第 1 部分,我们着重讨论当寄生电容直接耦合到电源输入电线时会发生的情况1. 只需

2022-11-22 07:29:30

提高PCB布线的一些经验

),二是钻孔周围的焊盘区。这两部分的尺寸大小决定了过孔的大小。很显然,在高速,高密度的PCB设计时,设计者总是希望过孔越小越好,这样板上可以留有更多的布线空间,此外,过孔越小,其自身的寄生电容也越小,更适合

2018-05-07 08:20:06

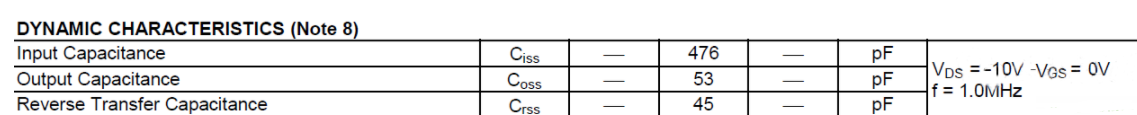

理解功率MOSFET的寄生电容

的差异相互扩散,也会在PN结的两侧产生电荷存储效应,这些因素作用在一起,在任何半导体功率器件内部,就会产生相应的寄生电容。MOSFET的寄生电容是动态参数,直接影响到其开关性能,MOSFET的栅极电荷

2016-12-23 14:34:52

磁芯对电感寄生电容的影响分析

;strong>减小电感寄生电容的方法<br/></strong>如果磁芯是导体,首先:&

2009-12-23 16:07:01

超强PCB布线设计经验谈附原理图(3)

:寄生电阻、寄生电容和寄生电感。例如:PCB的寄生电阻由元件之间的走线形成;电路板上的走线、焊盘和平行走线会产生寄生电容;寄生电感的产生途径包括环路电感、互感和过孔。当将电路原理图转化为实际的PCB

2008-10-28 09:26:35

飞捷教你二极管如何去降低寄生电容?

,寄生电容的影响已经不能忽视了。在系统中,这些不期望的电容来自方方面面,比如PCB的材质、厚度、板层结构、走线平行度,这些都是影响PCB板的寄生电容,还有元器件本身的寄生电容,最可恶的是这些东西还受

2020-12-15 15:48:52

pcb布线经验精华

布线需要考虑的问题很多,但是最基本的的还是要做到周密,谨慎。寄生元件危害最大的情况印刷电路板布线产生的主要寄生元件包括:寄生电阻、寄生电容和寄生电感

2008-07-23 17:13:40 0

0

0

0铁氧体环形电感器寄生电容的提取

铁氧体电感器在较高频率时可等效为“电阻、电感”的串联支路与一寄生电容的并联,该电容的存在对电感器的高频性能有重要影响。本文建立了铁氧体环形电感器2D平行平面场和3D

2009-04-08 15:45:17 66

66

66

66PCB布线设计3

印刷电路板布线产生的主要寄生元件包括:寄生电阻、寄生电容和寄生电感。例如:PCB的寄生电阻由元件之间的走线形成;电路板上的走线、焊盘和平行走线会产生寄生电容;寄生

2009-10-17 15:36:29 42

42

42

42PCB板寄生元件的危害

PCB板寄生元件的危害:印刷电路板布线产生的主要寄生元件包括:寄生电阻、寄生电容和寄生电感。例如:PCB的寄生电阻由元件之间的走线形成;电路板上的走线、焊盘和平行走线会

2009-11-15 22:28:47 0

0

0

0寄生电容对电磁干扰滤滤器效能的影响

寄生电容对电磁干扰滤滤器效能的影响

本文將針對交換式電源供應器在高頻切換所帶來的傳導性電磁干擾(Conducted Electromagnetic Interference)問題,藉由不同繞

2010-06-19 16:30:37 54

54

54

54PCB布线设计(之三)

寄生元件危害最大的情况印刷电路板布线产生的主要寄生元件包括:寄生电阻、寄生电容和寄生电感。例如:PCB的寄生电阻由元件之间的走线形成;电路板上的走线、焊盘和平行

2006-09-25 14:37:59 342

342

342

342电容的串并联计算方法

电容的串并联计算方法

电容串联后容量是减小了,但是这样可以增加他的耐压值。计算公式是:C1*C2/(C1+C2) 电容并联后容量是增大了,并联耐压数值按最小的计

2008-12-13 22:24:17 119276

119276

119276

119276

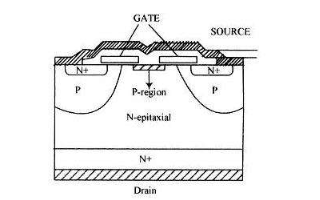

一种减少VDMOS寄生电容的新结构

一种减少VDMOS寄生电容的新结构

0 引 言 VDMOS与双极晶体管相比,它的开关速度快,开关损耗小,输入电阻高,驱动电流小,频率特性好,跨导高度线性

2009-11-25 17:49:50 1002

1002

1002

1002一种减少VDMOS寄生电容的新结构

一种减少VDMOS寄生电容的新结构

0 引 言 VDMOS与双极晶体管相比,它的开关速度快,开关损耗小,输入电阻高,驱动电流小,频率特性好,跨

2009-11-27 09:24:23 613

613

613

613一种减少VDMOS寄生电容的新结构

一种减少VDMOS寄生电容的新结构

0 引 言 VDMOS与双极晶体管相比,它的开关速度快,开关损耗小,输入电阻高,驱动

2010-01-11 10:24:05 1321

1321

1321

1321寄生电容耦合到电源_共模EMI问题的最常见来源

电磁干扰EMI中电子设备产生的干扰信号是通过导线或公共电源线进行传输,互相产生干扰称为传导干扰。传导干扰给不少电子工程师带来困惑,如何解决传导干扰?这里,我们先着重讨论当寄生电容直接耦合到电源输入

2018-05-18 01:17:00 2785

2785

2785

2785

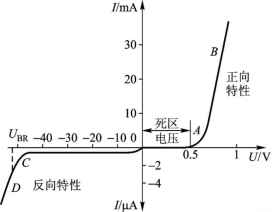

如何妙用二极管减少寄生电容

二极管以其单向导电特性,在整流开关方面发挥着重要的作用;其在反向击穿状态下,在一定电流范围下起到稳压效果。令人意外的是,利用二极管的反偏压结电容,能够有效地减少信号线上的接入寄生电容,这里将近一步讨论这个运用。

2017-03-21 11:31:30 3813

3813

3813

3813

寄生电容影响升压变压器的设计

升压设计中最关键的部件之一像图1是变压器。变压器的寄生组件,可以使他们偏离它们的理想特性和寄生电容与二次关联可引起大共鸣开关电流前沿的电流尖峰波形。这些尖峰可以导致调节器显示表现为义务的不稳定的操作

2017-05-02 14:15:40 19

19

19

19一文读懂二极管在寄生电容处理间的妙用

大家最熟悉的就是二极管的单向导电性,二极管如何减少寄生电容。正向接入方法,二极管接在信号线与附件功能模块之间,这表示附加功能模块使能时是高电平输出的。

2017-09-23 09:40:09 9649

9649

9649

9649

去耦电容的选择、容值计算和pcb布局布线详解

去耦电容的应用的非常广泛,在电路应用过程中对于去耦电容的容值计算和PCB电路布局布线有一些我们必须要了解的技巧。

2018-01-28 18:28:00 14406

14406

14406

14406如何消除寄生电容的影响

寄生电容一般是指电感,电阻,芯片引脚等在高频情况下表现出来的电容特性。实际上,一个电阻等效于一个电容,一个电感,和一个电阻的串连,在低频情况下表现不是很明显,而在高频情况下,等效值会增大,不能忽略。

2018-01-31 10:09:29 21526

21526

21526

21526

什么是“寄生电容”?寄生电容与三种电容器!

寄生电容一般是指电感,电阻,芯片引脚等在高频情况下表现出来的电容特性。实际上,一个电阻等效于一个电容,一个电感,和一个电阻的串连,在低频情况下表现不是很明显,而在高频情况下,等效值会增大,不能忽略。

2018-01-31 10:57:56 26011

26011

26011

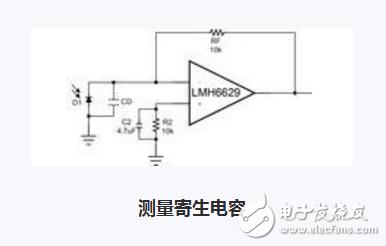

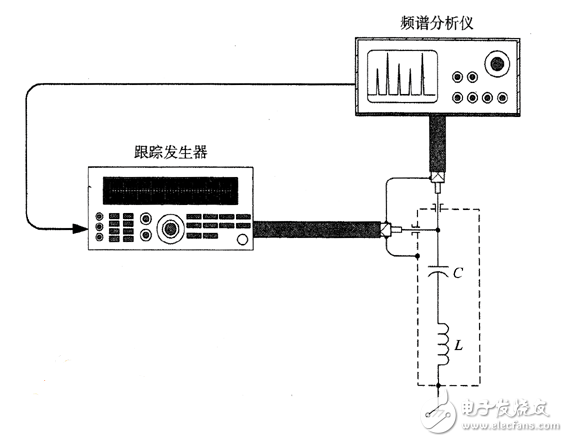

26011测量寄生电容与寄生电感

电容的寄生电感和寄生电阻主要是指它的引线和极板形成的电感和电阻,尤其是容量较大的电容更为明显。如果你解剖过电容器,会看到它的极板是用长达1米的金属薄膜卷曲而成的,其层状就像一个几十、甚至上百圈的线圈

2018-01-31 13:44:55 37299

37299

37299

37299

寄生电感怎么产生的_寄生电感产生原因是什么

本文开始阐述了寄生电感的概念和和寄生元件危害,其次阐述了寄生电感测量仪的设计和寄生电感产生原因或产生方式,最后介绍了PCB过孔的寄生电容和电感的计算以及使用。

2018-03-28 14:50:42 39049

39049

39049

39049

PCB电路中信号终端电容的作用介绍

信号的接收端可能是集成芯片的一个引脚,也可能是其他元器件。不论接收端是什么,实际的器件的输入端必然存在寄生电容,接受信号的芯片引脚和相邻引脚之间有一定的寄生电容,和引脚相连的芯片内部的布线也会存在寄生电容,另外引脚和信号返回路径之间也会存在寄生电容。

2019-06-21 15:57:47 3143

3143

3143

3143

寄生电容与分布电容的区别

分布电容强调的是均匀性。寄生跟强调的是意外性,指不是专门设计成电容,却有着电容作用的效应,比如三极管极间电容。单点说,两条平行走线之间会产生分布电容,元器件间在高频下表现出来的容性叫寄生电容。

2019-04-30 15:56:30 19502

19502

19502

19502

什么是寄生电感_PCB寄生电容和电感计算

寄生电感一半是在PCB过孔设计所要考虑的。在高速数字电路的设计中,过孔的寄生电感带来的危害往往大于寄生电容的影响。它的寄生串联电感会削弱旁路电容的贡献,减弱整个电源系统的滤波效用。我们可以用下面的公式来简单地计算一个过孔近似的寄生电感。

2019-10-11 10:36:33 19063

19063

19063

19063什么是寄生电容_寄生电容的危害

寄生的含义就是本来没有在那个地方设计电容,但由于布线之间总是有互容,互容就好像是寄生在布线之间的一样,所以叫寄生电容,又称杂散电容。

2020-09-17 11:56:11 27665

27665

27665

27665mos管寄生电容是什么看了就知道

寄生电容是指电感,电阻,芯片引脚等在高频情况下表现出来的电容特性。实际上,一个电阻等效于一个电容,一个电感,一个电阻的串联,低频情况下表现不明显,而高频情况下,等效值会增大。在计算中我们要考虑进去。

2020-10-09 12:04:17 34943

34943

34943

34943去耦电容的容值计算方法是怎样的

量C。 ⊿U是实际电源总线电压所允许的降低,单位为V。 I是以A(安培)为单位的最大要求电流; ⊿t是这个要求所维持的时间。 去耦电容容值计算方法:推荐使用远大于1/m乘以等效开路电容的电容值。 此处m是在IC的电源插针上所允许的电源总线电压变化的最大百分

2021-04-06 10:59:06 2521

2521

2521

2521基于寄生电容的MOS等效模型

之间或电路模块之间,由于相互靠近所形成的电容,是设计时不希望得到的电容特性,一般来说在低频应用中我们一般不考虑,但是对于MOS管驱动电路来说,寄生电容的存在是个不可绕过的考虑因素。

2022-04-07 09:27:12 4967

4967

4967

4967

什么是寄生电容,什么是寄生电感

本来没有在那个地方设计电容,但由于布线之间总是有互容,互容就好像是寄生在布线之间的一样,所以叫寄生电容 寄生电容: 本质上还是电容,满足i=c*du/dt。 电容是用来衡量储存电荷能力的物理量。根据

2022-07-27 14:23:55 15288

15288

15288

15288

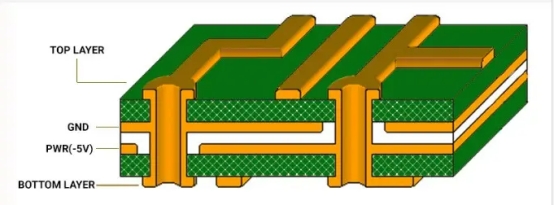

分享一些PCB布线小知识

合理选择PCB层数。用中间的电源层(vcclayer)和地层(Gndlayer)可以起到屏蔽作用,有效降低寄生电感和寄生电容,也可大大缩短布线的长度,减少信号间的交叉干扰。

2022-10-25 10:47:08 1447

1447

1447

1447

过孔的两个寄生参数是什么?它有什么影响?应该怎么消除?

近似用以下公式来计算:C=1.41εTD1/(D2−D1)。 过孔的寄生电容会给电路造成的主要影响是延长了信号的上升时间,降低了电路的速度。比如说,对于一块厚度为50mil的PCB板,如果使用内径为10mil,焊盘直径为20mil的过孔,焊盘与地铺铜区的距离为32

2022-10-30 13:15:18 2725

2725

2725

2725PCB常见布线规则

合理选择PCB层数。用中间的电源层(vcc layer)和地层(Gnd layer)可以起到屏蔽作用,有效降低寄生电感和寄生电容,也可大大缩短布线的长度,减少信号间的交叉干扰。

2023-01-03 16:11:27 2000

2000

2000

2000PCB阻抗不连续解决方法分析

过孔的寄生电容可以导致信号上升时间延长,传输速度减慢,从而恶化信号质量。 同样,过孔同时也存在寄生电感,在高速数字PCB中,寄生电感带来的危害往往大于寄生电容。

2023-01-12 15:01:27 415

415

415

415MOSFET的寄生电容及其温度特性

继前篇的Si晶体管的分类与特征、基本特性之后,本篇就作为功率开关被广为应用的Si-MOSFET的特性作补充说明。MOSFET的寄生电容:MOSFET在结构上存在下图所示的寄生电容。

2023-02-09 10:19:24 1995

1995

1995

1995

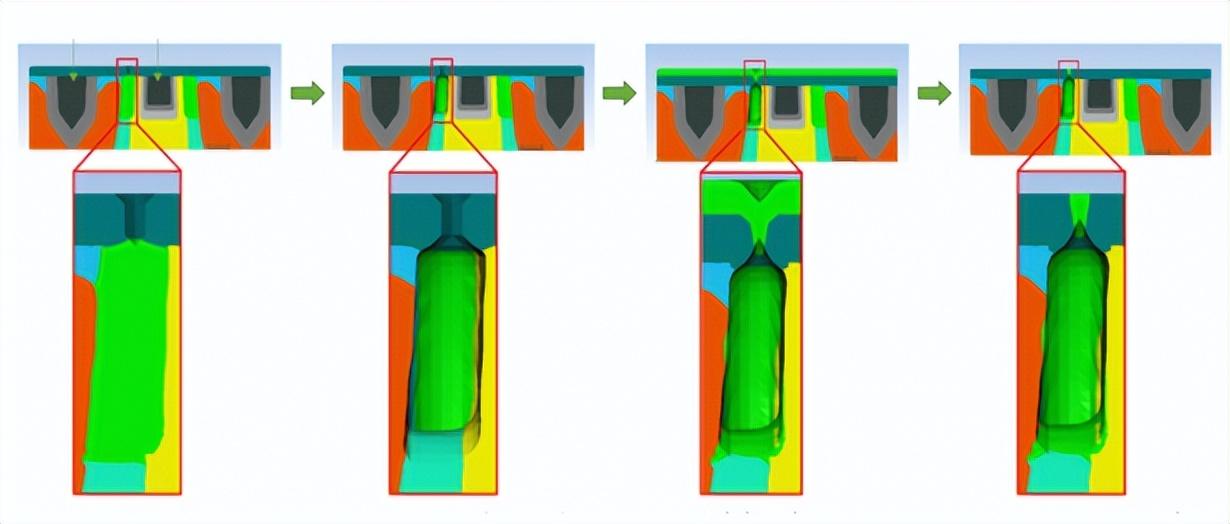

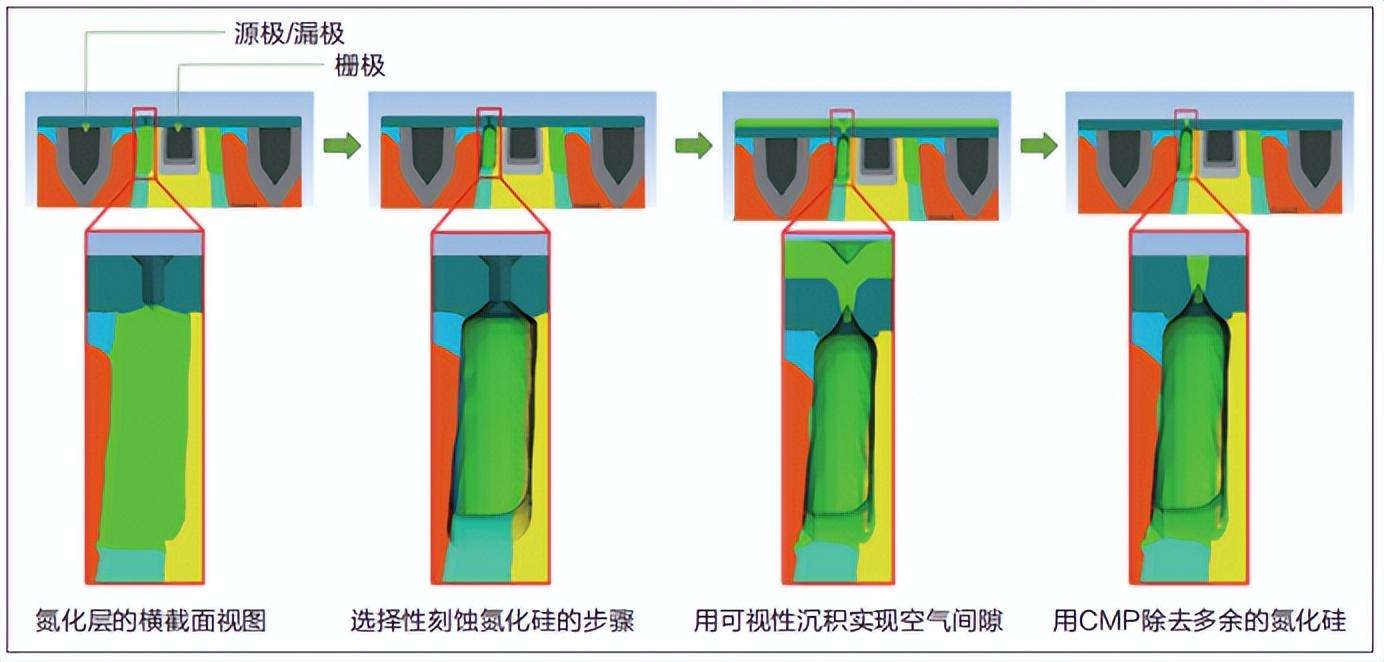

引入空气间隙以减少前道工序中的寄生电容

可以减少器件的开关延迟。减少寄生电容的方法之一是设法降低栅极和源极/漏极之间材料层的有效介电常数,这可以通过在该位置的介电材料中引入空气间隙来实现。这种类型的方式过去已经用于后道工序 (BEOL) 中,以减少金属互连之间的电容 [1-4]。本文中,我们将专注于前道工序 (FEOL

2023-03-28 17:19:08 559

559

559

559

浅谈PCB布线设计的重要参数

合理选择PCB层数。用中间的电源层(vcc layer)和地层(Gnd layer)可以起到屏蔽作用,有效降低寄生电感和寄生电容,也可大大缩短布线的长度,减少信号间的交叉干扰。

2023-04-05 06:51:00 386

386

386

386引入空气间隙以减少前道工序中的寄生电容

和晶体管的源极/漏极接触之间的寄生电容可以减少器件的开关延迟。减少寄生电容的方法之一是设法降低栅极和源极/漏极之间材料层的有效介电常数,这可以通过在该位置的介电材料中引入空气间隙来实现。这种类型的方式过去已经用于后道工序(BEOL)中,以减少金属互连之间的电容[1-4]。本文中,

2023-06-02 17:31:46 305

305

305

305

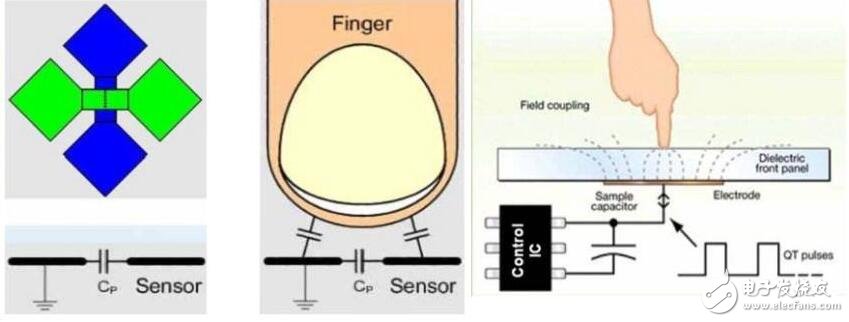

技术资讯 | 在高速设计中如何消除寄生电容?

本文要点寄生电容的定义寄生电容影响电路机理消除寄生电容的方法当你想到寄生虫时,你可能会想到生物学上的定义——一种生活在宿主身上或在宿主体内的有机体,从宿主身上吸取食物。从这个意义上说,寄生虫可能是

2022-05-31 11:09:01 1730

1730

1730

1730

PCB寄生电容的影响、计算公式和消除措施

寄生电容有一个通用的定义:寄生电容是存在于由绝缘体隔开的两个导电结构之间的虚拟电容(通常不需要的),是 PCB 布局中的一种效应,其中传播的信号表现得好像就是电容,但其实并不是真正的电容。

2023-07-24 16:01:36 5431

5431

5431

5431

pcb连线寄生电容一般多少

电容可能会对电路的性能和稳定性产生影响。因此,在 PCB 布线设计中,充分了解寄生电容的产生原因和处理方法是非常必要的。 什么是 PCB 连线寄生电容 维基百科上对于 PCB 连线寄生电容的定义是“由于 PCB 上信号线之间的相互耦合而导致的电容效应”。

2023-08-27 16:19:44 1606

1606

1606

1606寄生电容对MOS管快速关断的影响

寄生电容对MOS管快速关断的影响 MOS(Metal Oxide Semiconductor)管是一种晶体管,它以其高性能和可靠性而广泛应用于许多电子设备,如功率放大器和开关电源。尽管MOS管具有

2023-09-17 10:46:58 1242

1242

1242

1242PCB的过孔该怎么做?PCB如何使用过孔?

在高速,高密度的PCB设计时,设计者总是希望过孔越小越好,这样板上可以留有更多的布线空间,此外,过孔越小,其自身的寄生电容也越小,更适合用于高速电路。

2023-10-19 12:37:15 1488

1488

1488

1488

详解MOS管的寄生电感和寄生电容

寄生电容和寄生电感是指在电路中存在的非意图的电容和电感元件。 它们通常是由于电路布局、线路长度、器件之间的物理距离等因素引起的。

2024-02-21 09:45:35 245

245

245

245

德赢Vwin官网

App

德赢Vwin官网

App

评论