PCB中的RF辐射是什么东西啊?带状线什么屏蔽RF辐射,还有带状线和微带线有什么区别呢?

2023-04-06 17:18:53

:传导型(低频)EMI、辐射型(高频)EMI、ESD(静电放电)或雷电引起的EMI。传导型和辐射型EMI具有差模和共模表现形式。在处理各种形式的EMI时,必须具体问题具体分析。对于ESD和雷电

2010-03-22 16:55:57

印制电路板中的电磁干扰问题包括公共阻抗耦合、串扰、高频载流导线产生的辐射,以及印制线条对高频辐射的感应等。以下阐述了在PCB设计时为满足电磁兼容性必须注意的事项。

2019-07-25 06:55:47

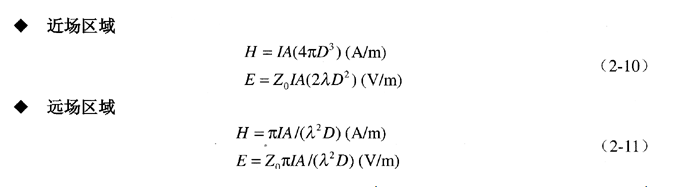

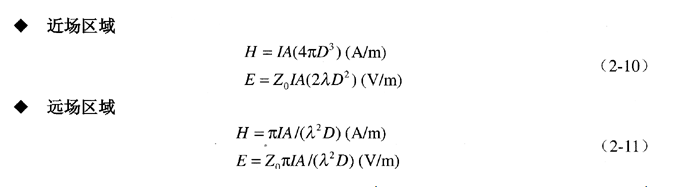

过寄生电容流动。这种电流称为共模电流,其产生的辐射称为共模辐射。 电缆的辐射主要以共模辐射为主。用电流环路模型来分析差模辐射,可分别得出近场区域和远场区域的辐射电磁场。 式中,I为环路电流;A为

2018-09-03 11:06:39

积。但是PCB板的制作成本会增加。在实际执行时确实很难达到完全平行与等长,不过还是要尽量做到。除此以外,可以预留差分端接和共模端接,以缓和对时序与信号完整性的影响 4、如何尽可能的达到EMC要求,又不致造成

2018-08-07 21:55:35

PCB设计中如何处理串扰问题 变化的信号(例如阶跃信号)沿

2009-03-20 14:04:47

,以抑制差分传输中的部分共模信号,但从理论上看这种做法是不可取的,阻抗如何控制?不给共模信号提供地阻抗回路,势必会造成EMI辐射,这种做法弊大于利。误区二:认为保持等间距比匹配线长更重要。在实际

2017-11-13 08:45:52

?不给共模信号提供地阻抗回路,势必会造成EMI辐射,这种做法弊大于利。 误区二:认为保持等间距比匹配线长更重要。在实际的PCB布线中,往往不能同时满足差分设计的要求。由于管脚分布,过孔,以及走线

2018-09-17 17:31:52

面面积对传输线参数没有影响,或者说忽略影响。 3.在EMC测试中发现时钟信号的谐波超标十分严重,只是在电源引脚上连接去耦电容。在PCB设计中需要注意哪些方面以抑止电磁辐射呢? EMC的三要素为辐射源,传播

2019-05-29 17:12:35

电路的地电流流经共地阻抗。电路1的地电位被地电流2调制。噪声信号或DC补偿经共地阻抗从电路2耦合到电路1。辐射耦合经辐射的耦合通称串扰,串扰发生在电流流经导体时产生电磁场,而电磁场在邻近的导体中感应

2014-11-19 14:07:27

。电路1的地电位被地电流2调制。噪声信号或DC补偿经共地阻抗从电路2耦合到电路1。辐射耦合经辐射的耦合通称串扰,串扰发生在电流流经导体时产生电磁场,而电磁场在邻近的导体中感应瞬态电流。辐射发射 辐射

2014-12-22 15:15:30

在何电源线上传导扰信号。均可用差模和共模信号来表示。差模干扰在两导线之间化输,属于对称性干扰:共模干扰在导线与地(机壳)之间传输,属于非对称性干扰。在一般情况下,差模干扰幅度小、频率低、所造成的于扰

2021-11-12 08:12:45

想给某电子设备定一个自己的EMC标准,如何选取辐射抗扰度的场强值?

2015-12-07 23:07:43

EMI如果超出了容许范围,就需要采取降噪对策。特别需要记住的是,在考虑辐射噪声对策时,针对共模噪声的对策是非常重要的。关于具体对策,后续会逐步介绍,其中最原则性的噪声对策是差模噪声要减少环路面积S(比如

2019-03-18 03:00:58

的正负电流无法抵消,于是其电源中就有共模电流份量在流动。研究过EMI的人都知道,共模辐射是最难对付的。图2差分信号转共模信号的现象,在李玉山教授翻译的Bogatin的《信号完整性》一书中第11.15章和

2020-11-04 09:40:06

爱特梅尔公司 (Atmel® Corporation) 发布用于太空应用的全新抗辐射SPARC® 处理器,在整个温度和电压范围内,AT697之F版本在100 MHz 时达到90 MIPs性能,功耗仅为0.7W。

2019-08-28 08:02:21

【作者】:卫宁;王剑峰;杜婕;周聪莉;郭旗;文林;【来源】:《信息与电子工程》2010年01期【摘要】:用特种复合屏蔽材料和缝焊封接工艺进行抗辐射封装,在普通封装存储器28C256的基础上,研制了抗

2010-04-22 11:44:45

本帖最后由 逸興遄飛 于 2016-4-15 14:08 编辑

辐射抗扰:10V 有点不明白

2016-04-15 09:24:44

本帖最后由 一只耳朵怪 于 2018-6-26 14:46 编辑

多频辐射抗扰度测试系统MT06000 多个频点干扰信号, 一般辐射抗扰度测试需要大量的时间来完成全频段测试。大多数测试人员都

2018-06-26 13:38:34

1.ISO 11452-2以及IEC 61000-4-3,为什么辐射抗扰度测试都是从80MHz开始。2.根据个人的辐射抗扰度测试经验,发现产品在80MHz~100MHz容易出现异常。无论是汽车电子产品,还是民品,都有此问题。这是什么原因?

2019-06-09 16:55:17

Susceptibility)---电磁抗扰度测试此测试之目的为:检测电器产品能否在电磁环境中稳定工作,不受影响。EMS测试主要包含什么内容?ESD-静电抗扰度测试RS-射频电磁场辐射抗扰度测试CS-射频场感应的传导

2018-04-11 18:41:01

于模拟接地。在数字电路设计中,有经验的PCB布局和设计工程师会特别注意高速信号和时钟。在高速情况下,信号和时钟应尽可能短并邻近接地层,因为如前所述,接地层可使串扰、噪声和辐射保持在可控制的范围。数字信号也

2023-12-19 09:53:34

EMC原理 之 传导(共模差模)辐射(近场远场)

2015-08-03 18:29:21

模线圈来进行抑制和衰减。我们常见的低通滤波器一般同时具有抑制共模和差模干扰的功能。第二章、感应干扰(近场)常见的电场 如两个金属板两端加电压。常见的磁场 如两个磁铁之间的磁场电磁波的速度在空气中接近于

2017-06-30 17:12:24

,也有称为电磁抗扰度,是指能忍受其它电器产品的电 磁干扰的程度。因此,电磁兼容性 EMC 一方面要滤除从电源线上引入的外部电磁干扰(辐射+传导),另一方面还能避 免本身设备向外部发出噪声干扰,以免

2019-02-14 22:31:40

,也有称为电磁抗扰度,是指能忍受其它电器产品的电 磁干扰的程度。因此,电磁兼容性 EMC 一方面要滤除从电源线上引入的外部电磁干扰(辐射+传导),另一方面还能避 免本身设备向外部发出噪声干扰,以免

2022-06-23 10:29:56

我们将更详细地讨论4个EMC预兼容性测试中的2个 - 辐射测试,辐射和抗扰度。辐射测试如之前的EMC基础知识博客中所述,辐射测试需要表征电子设备无意释放的电磁能量。辐射测试是全球最常见的EMC测试

2018-07-25 18:12:31

导线上产生感应电压,而产生共模电流 我再来分析PCB布局布线思路! 大环面积带来的问题: A.辐射发射大,抗扰度差 B.磁通大,使串扰增大 电源完整性 A.当大量芯片内的电路输出级同时动作

2023-04-19 16:27:17

。显然此时的正负波形不能严格对称,差分电路中的正负电流无法抵消,于是其电源中就有共模电流份量在流动。研究过 EMI 的人都知道,共模辐射是最难对付的。图 1图 2差分信号转共模信号的现象,在李玉山教授

2020-10-12 09:35:22

形式,差模EMI和共模EMI,电路中器件输出的电流流入一个负载时,就会产生差模EMI。电流流经多个导电平面,如PCB上的导线组或电缆,就会产生共模辐射。 差模辐射的计算其中Ip表示电流强度,f表示共模

2009-04-14 16:35:13

形式,差模EMI和共模EMI,电路中器件输出的电流流入一个负载时,就会产生差模EMI。电流流经多个导电平面,如PCB上的导线组或电缆,就会产生共模辐射。 差模辐射的计算其中Ip表示电流强度,f表示共模

2009-04-14 16:42:41

1.5.4 辐射抗扰度测试实质1.5.5 共模传导性抗扰度测试实质1.5.6 差模传导性抗扰度测试实质1.5.7 差模共模混合的传导性抗扰度测试实质······下载链接:`

2017-09-25 17:19:55

噪声即EMI如果超出了容许范围,就需要采取降噪对策。特别需要记住的是,在考虑辐射噪声对策时,针对共模噪声的对策是非常重要的。关于具体对策,后续会逐步介绍,其中最原则性的噪声对策是差模噪声要减少环路面积S

2021-03-16 09:15:22

Susceptibility)—电磁抗扰度测试

此测试之目的为:检测电器产品能否在电磁环境中稳定工作,不受影响。

EMS测试主要包含什么内容?

ESD-静电抗扰度测试

RS-射频电磁场辐射抗扰度测试

2023-06-13 09:45:16

。对于8Gbps及以上的高速应用更应该注意避免此类问题,为高速数字传输链路提供更多裕量。本文针对PCB设计中由小间距QFN封装引入串扰的抑制方法进行了仿真分析,为此类设计提供参考。那么,什么是小间距QFN封装PCB设计串扰抑制呢?

2019-07-30 08:03:48

昌晖仪表结合案例分享仪表辐射发射测试步骤、辐射发射测试结果分析及展频技术在辐射发射测试不合格项整改中的应用,对仪表工程师提升仪表电气兼容性能的设计水平有很好借鉴作用。1、电磁兼容概述通俗易懂来说

2018-08-11 18:06:07

另一端接有一台设备,相当于一个容性负载的天线,即天线的端点接有一块金属板,这时天线上流过均匀电流。设天线指向为最大场强,则得到最大场强计算公式为:式中,f是信号频率,ICM是电路中的共模电流,L为辐射

2019-05-11 16:54:43

共模辐射的大小为: E=4π*10^(-7)*f*I*L*sinθ/D。但是为什么L>λ/2时, E=60I/D ??????

2015-11-16 21:51:12

干扰通过X电容和差模线圈来抑制。 二、近场与远场骚扰通过空间传输实质上是骚扰源的电磁能以场的形式向四周空间传播。场被划分为近场和远场。其中一部分电磁场能量在辐射源周围空间及辐射源之间周期性地来回

2018-07-09 11:31:10

的原因有:图 共模和差模电流· 外界电磁场在电路走线中的所有导线上感应出来电压(这个电压相对于大地是等幅和同相的),由这个电压产生的电流;· 由于电路走线两端的器件所接的地电位不同,在这个地电位差的驱动下

2011-11-18 09:40:36

共模辐射主要从哪里进行辐射的啊,如果想要减小共模辐射有什么技巧吗?

2021-03-06 08:15:39

存在两种形式,差模EMI和共模EMI,电路中器件输出的电流流入一个负载时,就会产生差模EMI。电流流经多个导电平面,如PCB上的导线组或电缆,就会产生共模辐射。 差摸辐射的计算 其中Ip表示电流强度

2018-09-05 16:38:36

要尽可能减小不同性质信号线之间的并行长度,加宽它们之间的间距,改变某些线的线宽和高度。当然,影响串扰的因素还有许多,比如电流流向、干扰源信号频率上升时间等,应综合考虑。结语在本次控制单元高速PCB设计中

2015-01-07 11:30:40

真实世界中,为了确保汽车内的电子元器件仍旧稳健和有效,它们需要在一个受控环境中进行EMI干扰测试。辐射抗扰室是一个完全密封的传导空间,是一个理想的EMI测试环境,因为它能够完全控制空间中产生的电磁场

2019-06-10 08:23:39

射频电路PCB设计的关键在于如何减少辐射能力以及如何提高抗干扰能力,合理的布局与布线是设计时频电路PCB的保证。文中所述方法有利于提高射频电路PCB设计的可靠性,解决好电磁干扰问题,进而达到电磁兼容的目的。

2021-04-25 06:16:26

到空间或能量以电磁波形式在空间传播的现象。凡是电子产品都有相应的辐射骚扰要求。抑制辐射骚扰的最好方法还是重新对PCB的设计进行修正并重新合理设计,但在我们在实际工作中也经常发现,如用户在摩尔实验室

2020-10-22 07:39:25

请问一下,有没有抗辐射的瓷片电容??或者在辐射环境下相对而言比较能够抗辐射的,,,,,我们现在正准备做一种能够在辐射环境下使用的MSP430.。。。

2015-02-02 09:35:21

。对于8Gbps及以上的高速应用更应该注意避免此类问题,为高速数字传输链路提供更多裕量。本文针对PCB设计中由小间距QFN封装引入串扰的抑制方法进行了仿真分析,为此类设计提供参考。二、问题分析在PCB设计

2018-09-11 11:50:13

开关电源差模电流辐射干扰的模拟与分析

2019-05-16 11:16:08

开关电源的共模干扰和差模干扰对电路的影响是不同的,通常低频时差模噪声占主导地位,高频时共模噪声占主导地位,而且共模电流的辐射作用通常比差模电流的辐射作用要大得多,因此,区分电源中的差模干扰和共模干扰

2021-12-30 06:52:22

在设计过程的早期就考虑关于辐射发射、辐射敏感性、抗扰度、传导发射和传导敏感性/抗扰性的管制标准。由于全球大气污染,越来越难以找到一个能够对设备进行全频谱测试的开阔试验场地(OATS)。在某些国家和地区,现在

2018-10-19 09:39:36

一个拇指大小的运放电路,4层PCB,双运放,约放大10000倍。因为添加屏蔽罩不方便,那么怎么设计PCB可以提高这个PCB的抗辐射干扰,周围有设备时,总是有杂波。我的想法是,运放往下4层,分别

2014-12-10 12:38:49

重点分析一下电容和接地过孔在保证信号低阻抗回路中所起的作用,这也是多层PCB板设计中有效抑制EMI的重要方面之一。多层PCB设计中,由于布线密度,拓补结构的要求,信号走线经常需要在层间切换,如果它所

2019-05-20 08:30:00

引言 随着IC 器件集成度的提高、设备的逐步小型化和器件的速度愈来愈高,电子产品中的EMI问题也更加严重。从系统设备EMC /EMI设计的观点来看,在设备的PCB设计阶段处理好EMC/EMI

2018-09-14 16:32:58

与参考接地板之间的容性耦合导致辐射发射原理为什么晶振布置在PCB边缘时会导致辐射超标,而向板内移动后,可以使辐射发射测试通过呢?从以上分析已经可以看出,晶振与参考接地板之间的耦合导致电缆共模辐射的实质是晶

2020-12-25 15:02:07

高速数字电路中控制破坏信号完整性因素的一项有效措施。在印制电路板(PCB抄板)上的差分线,等效于工作在准TEM模的差分的微波集成传输线对。其中,位于PCB顶层或底层的差分线等效于耦合微带线,位于多层

2018-12-11 19:48:52

有没有谁知道抗辐射的电子元器件啊,主要是能够代替瓷片电容的,,还有电阻,要用在msp430上,不胜感激~~~~

2015-02-02 09:46:22

连接(双绞线每一圈的长度对应于噪声半波长的整数倍)。如果大家打开电脑机箱,就可以看到主板到前面板 USB 接口就是用双绞线进行连接,可见双绞线连接对于抗干扰和降低辐射的重要性。9、对于数据排线,尽量在

2022-04-16 14:30:53

电磁辐射。这里可以看到,频率不同,电磁波在空间的传输距离不同。电磁辐射的特点决定我们在有些地方需要利用,而在另外场合又需要避免:如无线通信。又如电磁辐射会导致电子系统的串扰、电磁兼容性(EMC)等

2017-03-14 09:38:32

针对当前严峻的电磁环境,分析了电磁干扰的来源,通过产品开发流程的分解,融入电磁兼容设计,从原理图设计、PCB设计、元器件选型、系统布线、系统接地等方面逐步分析,总结概括电磁兼容设计要点,最后,介绍了

2019-05-31 06:43:44

,12MHZ的晶体正好布置在了PCB边缘,当产品放置与辐射发射的测试环境中时,被测产品的高速器件与实验室中参考接地会形成一定的容性耦合,产生寄生电容,导致出现共模辐射,寄生电容越大,共模辐射越强;而寄生电容实质

2020-06-09 15:44:58

、不对称千扰或接地干扰,是载流体与大地之间的干扰。 差模干扰存在于电源相线与零线及相线与相线之间。差模干扰有时也称常模干扰、横模千扰或对称千扰,是载流导体之间的干扰。共模干扰是由于辐射或串扰藕合到电路中

2014-10-11 15:03:03

另一端接有一台设备,相当于一个容性负载的天线,即天线的端点接有一块金属板,这时天线上流过均匀电流。设天线指向为最大场强,则得到最大场强计算公式为:式中,f是信号频率,ICM是电路中的共模电流,L为辐射

2019-08-17 04:00:00

一、 产品问题描述 某称重显示仪产品在进行电磁抗扰度试验时,产品会出现数值跳动、显示异常等现象。该产品要求进行静电/浪涌/电快速脉冲群/传导抗干扰/辐射抗干扰/电压跌落 6 项测试,原始样机进行摸底

2016-08-06 10:16:05

的影响,甚至使其失效。针对各种辐射效应,在器件的材料、电路设计、结构设计、工艺制造及封装等各个环节采取加固措施,使其具有一定的抗辐射性能。选择抗辐射加固的器件应用在空间辐射环境中,将能提高航天器

2019-07-02 07:10:06

在PCB电路设计中有很多知识技巧,之前我们讲过高速PCB如何布局,以及电路板设计最常用的软件等问题,本文我们讲一下关于怎么解决PCB设计中消除串扰的问题,快跟随小编一起赶紧学习下。 串扰是指在一根

2020-11-02 09:19:31

的布线方向规则相邻两层间的走线必须遵循垂直走线的原则,否则会造成线间的串扰,增加EMI辐射。简而言之,相邻的布线层遵循横平竖垂的布线方向,垂直的布线可以抑制线间的串扰。规则六:高速PCB设计中的拓扑结构

2017-11-02 12:11:12

。在开关电源输入电源线中向外传播的骚扰,既有差模骚扰、又有共模骚扰,共模骚扰比差模骚扰产生更强的辐射骚扰。传导骚扰的测试频率范围为150KHz~30MHz,限值要求如下表1 所示:在0.15MHz

2020-03-27 14:57:30

ST MEMS麦克风的RF抗扰度是多少?塑料包装如何抑制辐射干扰?以上来自于谷歌翻译以下为原文 What is the RF immunity of the ST MEMS microphones

2018-12-05 16:15:46

`请教!做辐射抗扰度试验时,频点在80MHz、150MHz时出现干扰,电源通道滤波电容C1、C2容值100nF,信号通道底层C4容值1nF,请各位帮忙指导一下如何调整规避这两个干扰点。`

2019-02-20 16:10:53

太赫兹辐射(THz)在材料光谱分析、断层摄影成像、生物材料表征等方面有广泛的应用前景。THz成像技术和应用中辐射源的产生和检测技术是两个关键问题。目前迄今为止,对有关THz辐射的产生人们提出了多种多样的方案,但缺少高功率、低价和小型的THz辐射源仍然是目前这项技术应用的重大障碍。

2019-08-05 08:22:48

,结合系统架构,确定辐射源。之后,通过对辐射源数字电路进行设计改进,加入芯片去耦电容和输出信号线的滤波电容,优化PCB设计,最终使该产品的空间辐射通过验证标准,并由此提出了空间辐射超标频谱分析法的步骤。

2015-08-05 15:58:43

电磁辐射干扰问题无线通信非常复杂,要分基带和射频,在数字电子线路设计中,多数工程师常常对电磁兼容性(EMC)的问题感到困扰。EMC是指电子系统在目标电磁环境下保持良好性能且不会向该环境中引入大量电磁

2022-04-07 15:19:16

高速PCB设计中的电磁辐射检测技术目前大部分硬件工程师还只是凭经验来设计PCB,在调试过程中,很多需要观测的信号线或者芯片引脚被埋在PCB中间层,无法使用示波器等工具去探测,如果产品不能通过功能测试

2013-10-28 14:39:24

高速PCB设计中的电磁辐射检测技术,总结的太棒了

2021-04-25 07:38:23

边缘辐射问题。6、布线层的投影平面应该在其回流平面层区域内。原因:布线层如果不在回流平面层的投影区域内,会导致边缘辐射问题,并且导致信号回路面积增大,从而导致差模辐射增大。7、多层板中,单板TOP

2014-12-25 10:19:32

,相邻的布线层遵循横平竖垂的布线方向,垂直的布线可以抑制线间的串扰。 规则六:高速PCB设计中的拓扑结构规则 在高速PCB设计中,线路板特性阻抗的控制和多负载情况下的拓扑结构的设计,直接决定着产品

2016-01-19 22:50:31

在硬件系统设计中,通常我们关注的串扰主要发生在连接器、芯片封装和间距比较近的平行走线之间。但在某些设计中,高速差分过孔之间也会产生较大的串扰,本文对高速差分过孔之间的产生串扰的情况提供了实例仿真分析

2018-09-04 14:48:28

方向的间距时,就要考虑高速信号差分过孔之间的串扰问题。顺便提一下,高速PCB设计的时候应该尽可能最小化过孔stub的长度,以减少对信号的影响。如下图所1示,靠近Bottom层走线这样Stub会比较短。或者

2020-08-04 10:16:49

去耦电容。在PCB设计中需要注意哪些方面以抑止电磁辐射呢? EMC的三要素为辐射源,传播途径和受害体。传播途径分为空间辐射传播和电缆传导。所以要抑制谐波,首先看看它传播的途径。电源去耦是解决传导方式

2019-05-31 13:19:06

FDP抗辐射石英光纤 Polymicro旗下的FDP系列石英光纤运行波长低至190nm.,超高紫外传输,超低紫外老化,具有出色的抗辐射性能。说明:Polymicro旗下的FDP系列石英光纤

2021-10-19 15:30:03

高速PCB设计中的电磁辐射检测技术

目前大部分硬件工程师还只是凭经验来设计PCB,在调试过程中,很多需要观测的信号线或者芯

2009-11-17 09:15:30 1235

1235 线路板的辐射主要产生于PCB走线和“I/O”电缆。前面介绍了共模和差模电流,从这两种电流的模式出发,可把辐射分为差模辐射和共模辐射两种。

2023-08-29 14:23:20 427

427

在PCB设计中需要注意哪些方面以抑止电磁辐射呢? 在PCB设计中,为了抑制电磁辐射,需要注意以下几个方面: 1. 地线布线 地线是抑制电磁辐射的重要手段之一。在PCB设计中,要保证地线的连续性

2023-11-23 10:07:31 356

356

德赢Vwin官网

App

德赢Vwin官网

App

评论