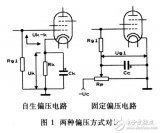

本文提供一个简单实用的电子管测试装置电路(Tube Tester),适用于DIY发烧友使用。工欲善其事,必先利其器,利用此装置能比较精确地检测电子管的静态工作点、互导和配对特性等,在胆机制作或摩机时就胸有成竹,成功在望。

2015-01-07 10:22:48 22347

22347

,是不可能产生爆发性创新的。华为要开放地吸取“宇宙”能量,华为胸有成竹在2020年销售收入超过1500亿美元。

2016-06-02 16:24:06 2655

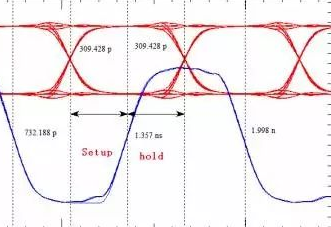

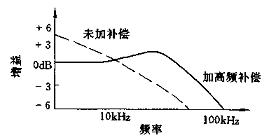

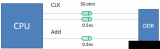

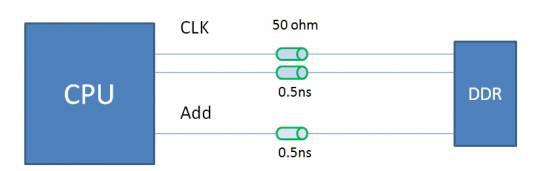

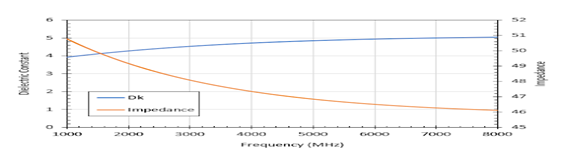

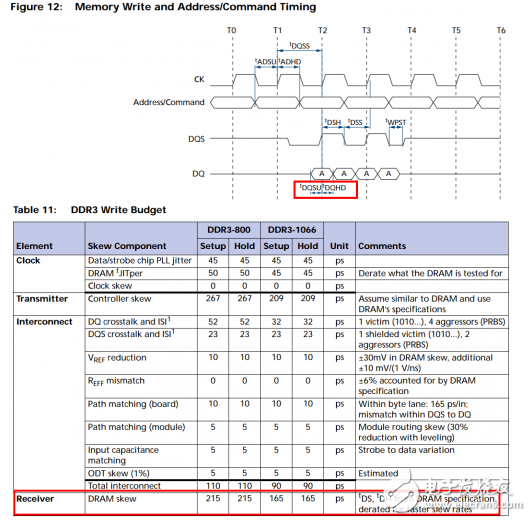

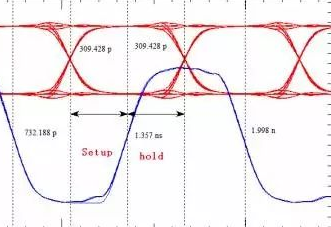

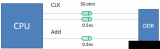

2655 DDR布线在PCB设计中占有举足轻重的地位,设计成功的关键就是要保证系统有充足的时序裕量。要保证系统的时序,

2017-09-26 11:39:47 6363

6363

多年前,无线时代(Beamsky)发布了一篇文章关于DDR布线指导的一篇文章,当时在网络上很受欢迎,有很多同

2017-10-16 09:22:08 36277

36277

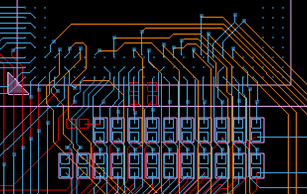

本文首先列出了DDR2布线中面临的困难,接着系统的讲述了DDR2电路板设计的具体方法,最后给出个人对本次电路设计的一些思考。

2020-11-20 10:28:35 6386

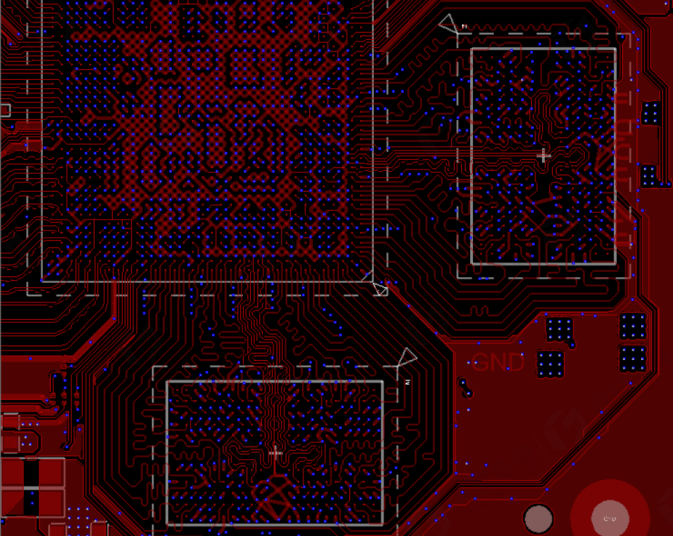

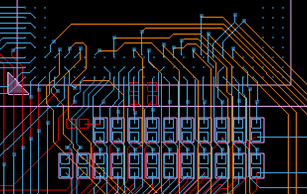

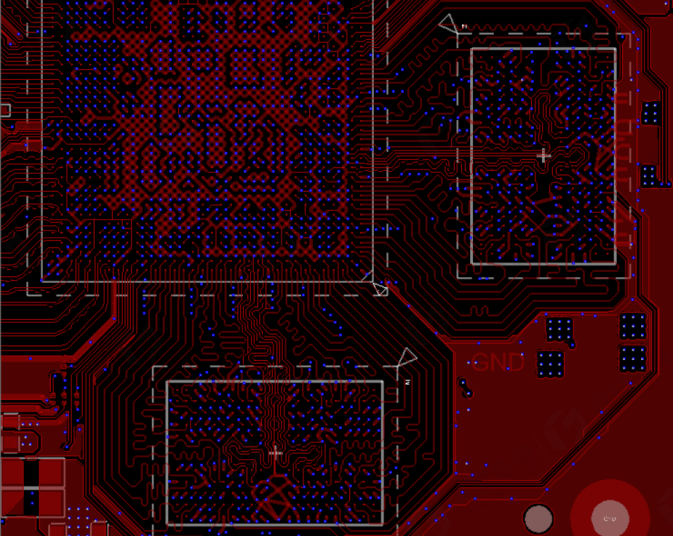

6386 上期和大家聊的电源PCB设计的重要性,那本篇内容小编则给大家讲讲存储器的PCB设计建议,同样还是以大家最为熟悉的RK3588为例,详细介绍一下DDR模块电路的PCB设计要如何布局布线。

2023-08-16 15:20:58 1378

1378

上期和大家聊的电源PCB设计的重要性,那本篇内容小编则给大家讲讲存储器的PCB设计建议,同样还是以大家最为熟悉的RK3588为例,详细介绍一下DDR模块电路的PCB设计要如何布局布线。 由于

2023-08-21 17:16:50 563

563

上期和大家聊的电源PCB设计的重要性,那本篇内容小编则给大家讲讲存储器的PCB设计建议,同样还是以大家最为熟悉的RK3588为例,详细介绍一下DDR模块电路的PCB设计要如何布局布线。 由于

2023-08-24 08:40:05 899

899

[table=98%][tr][td]刚刚入手一个51开发板,兴致勃勃的编起了程序,很是胸有成竹。因为之前在proteus上仿真了不少。可是在开发板上却是处处碰壁啊。就说一个简单的检测按键是否按下

2012-07-15 10:48:43

看懂,如果你看不懂,那么请按这样一个通用的基本法则做: (1)DDR和主控芯片尽量靠近(2)高速约束中设置所有信号、时钟线等长(最多允许50mils的冗余),所有信号、时钟线长度不超过1000mils(3

2015-01-15 10:39:37

主要是针对DDR2 667内存的设计。信号分组:DDR2的布线中习惯把信号分成若干组来进行设计,分成同组的信号具有相关或者相似的信号特性。时钟组:差分时钟信号,每一对信号都是同频同相的。ckp0

2011-10-27 14:53:32

共享交流一下,DDR3布线技巧

2016-01-08 08:17:53

这篇帖子跟大家一起来讨论下DDR3布线的那些事:DDR3的设计有着严格等长要求,归结起来分为两类(以64位的DDR3为例): 数据 (DQ,DQS,DQM):组内等长,误差控制在20MIL以内,组间

2016-10-28 10:25:21

DDR2,DDR3等 因频率不同,可以会有不同的要求,就一般而言,DDR布线时,要将DDR的网络分成几个组:地址线,控制线,数据线,时钟等差分线。我的疑问是,在6层板中,需不需要将地址线与数据线分别

2015-11-04 13:40:02

DDR布线参考Hardware and Layout Design Considerations for DDR Memory InterfacesEmbedded systems

2009-11-19 10:08:48

DDR-Topology DDR布线通常是一款硬件产品设计中的一个重要的环节,也正是因为其重要性,网络上也有大把的人在探讨DDR布线规则,有很多同行故弄玄虚,把DDR布线说得很难,我在这里要

2019-05-31 07:52:36

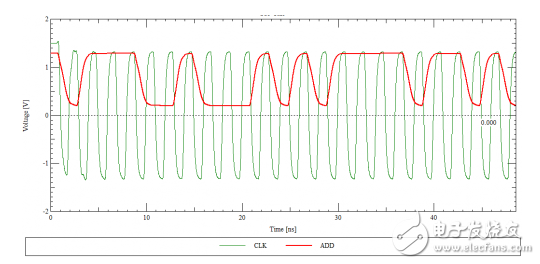

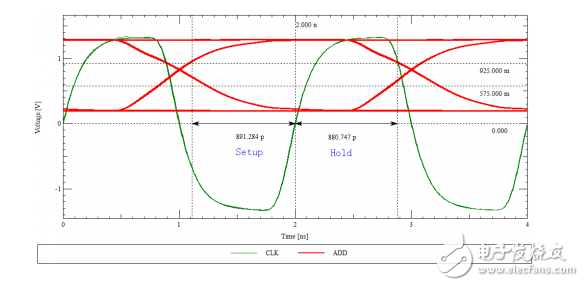

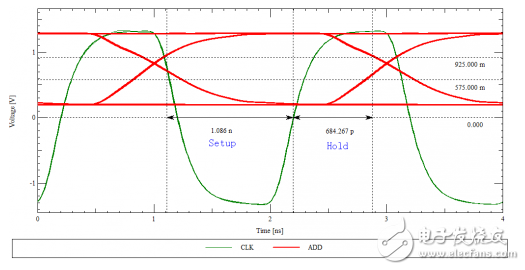

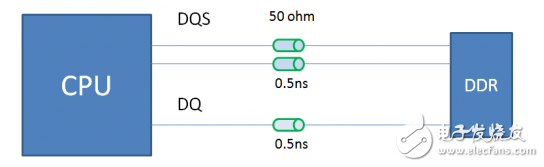

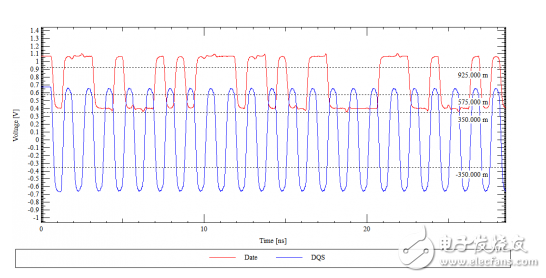

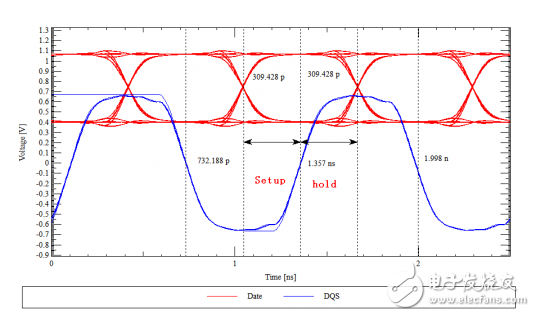

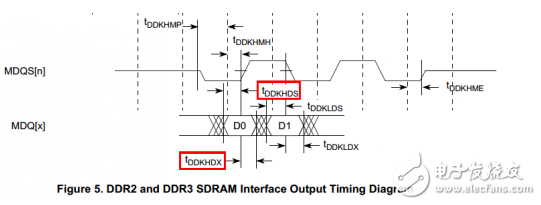

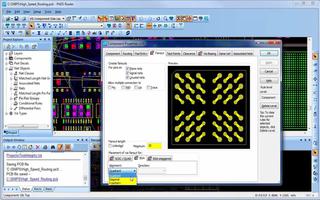

800Mbps。但是DDR的数据信号却是双倍速率的,如果DQS频率为800MHz,那么数据信号的速率就应该为1600Mbps。下面将通过具体的仿真实例来看一下。有兴趣的朋友可戳附件下载。

2016-11-08 16:59:51

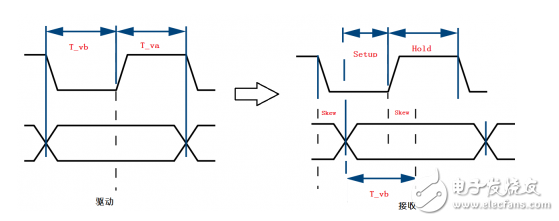

考虑时钟抖动以及数据信号的抖动,以及串扰、码间干扰带来的影响,如果把这些因素都考虑进来,留给我们布线偏差的裕量就比较小了。综上所述,时序控制的目的就是要保证数据在接收端有充足的建立时间与保持时间,明白了这一点,我们在线长匹配这个问题上就能做到胸有成竹,游刃有余了。

2018-09-20 10:29:55

层,用来抑制EMI; 导线走线长度:所有DDR的差分时钟线CK与CK#必须在同一层布线,误差+-20mil,最好在内层布线以抑制EMI。如果系统有多个DDR器件的话,要用阻值100~200ohm的电阻进行差

2012-12-29 19:20:36

上期和大家聊的电源PCB设计的重要性,那本篇内容小编则给大家讲讲存储器的PCB设计建议,同样还是以大家最为熟悉的RK3588为例,详细介绍一下DDR模块电路的PCB设计要如何布局布线。

由于

2023-08-16 15:15:53

并不会注意一些数字上的差异,如DDR3和DDr2,或许大多数人都会追求时髦选择DDR3,但是你真的了解DDR2与DDR3的区别吗?作为消费者,其实我们可主宰自己的命运,用知识的武器捍卫自己的选择。下面

2011-12-13 11:29:47

有了之前的硬件设计前期准备,大家已经能够做到对整个方案的硬件设计(PCB板子)胸有成竹了,可谓是“万事俱备,只欠东风”。(注:关于AD10的使用不在本手记的内容范围,但这里假设大家都已

2012-03-30 10:18:07

有了之前的硬件设计前期准备,大家已经能够做到对整个方案的硬件设计(PCB板子)胸有成竹了,可谓是“万事俱备,只欠东风”。(注:关于AD10的使用不在本手记的内容范围,但这里假设大家都已

2012-12-04 23:14:03

请问 在TI 给出的 EVM 参考设计中 DDR 的走线都串入一个22欧姆的电阻,按照SI 的理论这个电阻是保证匹配减少过冲的,在POWER PC 及MIPS 架构的CPU DDR布线中不需要增加这个电阻 ,请问这个电阻在TI ARM 的CPU 中一定需要吗?

2018-05-15 09:35:28

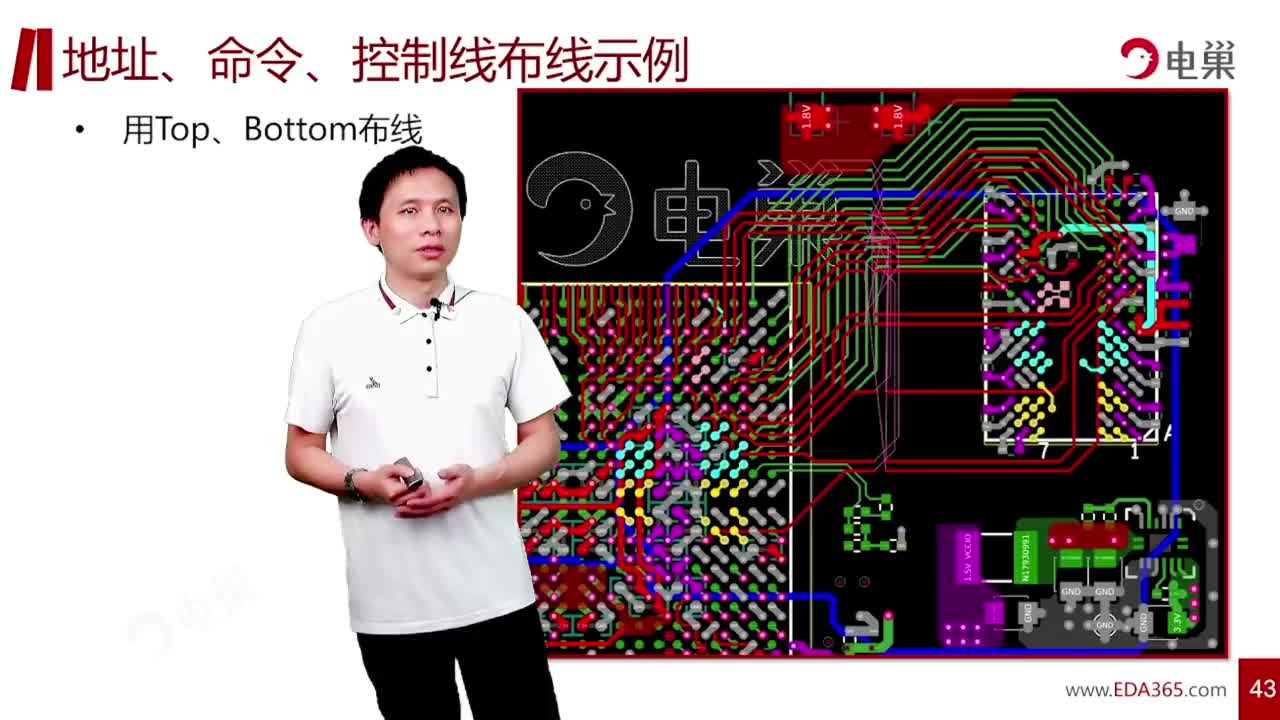

`直播链接:http://t.elecfans.com/live/574.html直播内容及亮点:详解DDR高速存储器模块的布局布线的设计思路,从原理图分析到PCB布局布线,从一片到两片、四片DDR

2018-10-10 11:49:20

问题:在HW-USB-FLYLEADS-G电缆上使用的最大布线长度是多少?请看下面的图片。背景:我使用HW-USB-FLYLEADS-G电缆和DLC10平台电缆USB II连接到我板的JTAG端口

2020-05-20 07:45:06

,SI攻城狮很喜欢;作为一种片内端接,由于去掉了PCB上的终端电阻,大大的简化了设计,Layout攻城狮很钟意;作为一种可以灵活配置的片内端接,硬件攻城狮也爱不释手。总而言之,喜大普奔。早在DDR2时代

2022-12-28 14:47:13

分信号布线问:在pcb上靠近平行走高速差分信号线对的时候,在阻抗匹配的情况下,由于两线的相互耦合,会带来很多好处。但是有观点认为这样会增大信号的衰减,影响传输距离。是不是这样,为什么?我在一些大公司

2014-12-31 14:32:05

在PCB设计中,通讯模块天线的布线是十分重要的。大家来探讨一下其注意事项有哪些?我列举一下:1、天线的线宽最好多宽;2、天线的线长,天线都有一个匹配电阻,那么这个线长是不是根据公式R=p*(L/S

2013-08-26 11:41:17

多年前,无线时代(Beamsky)发布了一篇文章关于DDR布线指导的一篇文章,当时在网络上很受欢迎,有很多同行参与了转载。如今看来,那篇文章写得不够好,逻辑性不强,可操作性也不强。在近几年的硬件产品

2022-08-11 09:07:02

平面。特征阻抗控制在50~60 Ω。信号线宽参考具体设计实施细则。信号组与其他非DDR信号间距至少保持在20 mil以上。组内信号应该与DDR时钟线长度匹配,差距至少控制在25 mil内。串联匹配

2017-10-16 15:30:56

,以及串扰、码间干扰带来的影响,如果把这些因素都考虑进来,留给我们布线偏差的裕量就比较小了。 综上所述,时序控制的目的就是要保证数据在接收端有充足的建立时间与保持时间,明白了这一点,我们在线长匹配这个问题上就能做到胸有成竹,游刃有余了。

2018-09-20 10:59:44

问题,保证内存正确访问,你的内存电路就设计成功了。有了这个指导思想,内存布线就可以按部就班地完成。不过,不同的RAM类型,虽然目标都是避免判决和时序错误,但实现方法因工作模式不同而有较大差异。 高速系统一

2014-11-10 10:09:13

SDRAM和DDR布线技巧ecos应用是与硬件平台无关的,虽然开发板没有涉及到SDRAM和DDR,不过,在某些高端平台上使用ecos可能会遇到内存布线问题,为了完整叙述,这里一并给出说明。&

2010-03-18 15:33:07

存储器控制器用户指南列出了数据,地址,控制和时钟信号的长度匹配要求。给出的数字是否必须补偿FPGA和DDR2封装内的键合线长度?如果是这样,我在哪里可以找到这些长度?谢谢,TL以上来自于谷歌翻译以下

2019-03-15 10:06:16

led显示屏参数看这一篇就够了

2021-06-01 07:17:31

、码间干扰带来的影响,如果把这些因素都考虑进来,留给我们偏差的裕量就比较小了。 综上所述,时序控制的目的就是要保证数据在接收端有充足的建立时间与保持时间,明白了这一点,我们在线长匹配这个问题上就能做到胸有成竹,游刃有余了。

2018-09-19 16:21:47

的影响后,自动布线的质量在一定程度上可以得到保证。7、布线的整理如果你所使用的EDA工具软件能够列出信号的布线长度,检查这些数据,你可能会发现一些约束条件很少的信号布线的长度很长。这个问题比较容易处理,通过

2018-10-04 16:50:52

Altium18.0.11无法正常显示From-To两点的布线长度,这是软件的bug吗

2019-09-27 05:35:33

的接口连接。DDR2芯片的连接电路如图2.27所示。 图2.27 DDR2芯片接口电路DDR2芯片接口以及PCB layout,通常需要遵循以下的原则。● 单端信号的电路板阻抗一般控制在50 ohm

2016-08-12 17:59:50

信号);2. 布局时应注意以下几点:(1)对于DIMMs,匹配电阻应靠近第一个DIMMs 放置对于SOP/BGA,匹配电阻应根据不同的芯片确定放置端,若时钟有加匹配电配,则电阻可靠控制芯片放置;(2

2012-09-17 21:15:33

DDR总线结构是什么嵌入式DDR总线的布线分析

2021-04-25 07:36:29

体会到一种心里清澈明亮的感觉,因为在设计的时候,你要对要实现的逻辑要非常的了解,要胸有成竹。看到小梅哥写代码,对着系统框图一气呵成,思路很清晰。这不仅仅是对设计系统整体的把握了然于胸,对底层细节也是

2015-11-03 21:31:23

设计问题案例集”两大内容体系系统化指导学习,让工程师对“设计规范”游刃有余、对“价格影响”胸有成竹。可一键计价、警示价格趋势、建议调整方向,揭露板厂定价内幕、消除行业潜规则。扫码加入华秋DFM用户交流群

2021-04-25 14:06:14

大家好,我正在研究我的第一个Kintex7 DDR3接口。为了实现RAM,我想在PCB上包含长度匹配的封装走线长度。要获取包延迟信息,我使用了命令(在Vivado中)link_design

2020-08-12 10:17:19

新东西且不断地实践之,在疑问中找到成长的路径。为了利用有限的实验时间获得最大的收益,我们希望每一个做实验的人都能做到以下四点:1.做实验之前熟读相关的资料,做到胸有成竹,最好能在课前准备好程序2.不放过

2011-03-03 16:58:36

且不断地实践之,在疑问中找到成长的路径。为了利用有限的实验时间获得最大的收益,我们希望每一个做实验的人都能做到以下四点:1.做实验之前熟读相关的资料,做到胸有成竹,最好能在课前准备好程序2.不放过实验

2011-03-09 13:52:59

根据需要进行处理; 7.4信号越不重要,自动布线工具对其布线的自由度就越大。 8、布线的整理 如果你所使用的EDA工具软件能够列出信号的布线长度,检查这些数据,你可能会发现一些约束条件很少的信号布线

2018-08-23 17:02:59

的长度匹配关系。其他信号走线长度应按照组为单位来进行匹配,每组内信号长度差应该严格控制在一定范围内。不同组的信号间虽然不像组内信号那样要求严格,但不同组长度差同样也有一定要求。信号组布线顺序为了确保

2015-10-21 10:37:10

对于平行线布线时是不是走线长度越短越好?

2014-02-14 09:56:19

PCB布线设计的好坏直接影响到硬件电路能否正常工作或运行多快的速度。而在高速数字PCB设计中,DDR2是非常常见的高速缓存器件,且其工作频率很高本文将针对DDR2的PCB布线进行讨论。DDR

2016-12-26 16:56:05

面对4片ddr3改怎么布局,我想双面对称布局改怎么走拓弧结构,第一次画没经验忘指导。还有都有什么需要等长,都在什么上面有要求C:\Users\yg\Desktop

2019-06-03 03:00:21

DDR3布线时CPU到DDR3的地址线长2037mil ,数据线长1613mil,这样会不会有问题

2019-06-05 03:34:28

本帖最后由 gk320830 于 2015-3-5 12:38 编辑

飞思卡尔的关于DDR内存布线设计资料,主要涉及了内存高频控制线的等长,阻抗匹配的等设计

2013-08-26 13:31:20

本期讲解的是高速PCB设计中,关于DDR布线知识。一.DDR信号功能与网络名了解DDR的各个信号功能与网络名。与DDR相比,DDR2/3最大差别多了功能OTD与OCD。重要信号线1.DQS信号

2017-10-27 10:48:26

SDRAM与DDR布线指南:ecos应用是与硬件平台无关的,虽然开发板没有涉及到SDRAM和DDR,不过,在某些高端平台上使用ecos可能会遇到内存布线问题,为了完整叙述,这里一并给出说明。 很

2010-03-18 15:29:08 0

0 本章先对自制电子管功放的元件选配、安装程序、调试技巧及关键制作要领作一简要介绍。当你胸有成竹,跃跃欲试时,就可以动手操作了。

电子管音频功率

2010-06-04 09:41:52 7959

7959

研究了MPC8379E处理器的相关资料和DDR2的特性,以及它们之间PCB布线的规则和仿真设计。由于MPC8379E和DDR2都具有相当高的工作频率,所以他们之间的走线必须满足高速PCB布线规则,还要结

2013-03-12 15:22:26 80

80 PCB的DDR布局布线规则与实例教程说明

2015-11-13 16:13:47 0

0 DDR2_DDR3_SDRAM,PCB布线规则指导

2017-10-31 10:06:48 78

78 DDR布线在PCB设计中占有举足轻重的地位,设计成功的关键就是要保证系统有充足的时序裕量。要保证系统的时序,线长匹配又是一个重要的环节。我们来回顾一下,DDR布线,线长匹配的基本原则是:地址,控制

2017-11-28 11:34:58 0

0 DDR布线在PCB设计中占有举足轻重的地位,设计成功的关键就是要保证系统有充足的时序裕量。要保证系统的时序,线长匹配又是一个重要的环节。我们来回顾一下,DDR布线,线长匹配的基本原则是:地址,控制

2018-03-23 10:05:00 1334

1334

DDR布线在PCB设计中占有举足轻重的地位,设计成功的关键就是要保证系统有充足的时序裕量。要保证系统的时序,线长匹配又是一个重要的环节。我们来回顾一下,DDR布线,线长匹配的基本原则是:地址,控制/命令信号与时钟做等长。

2018-09-27 09:56:00 6659

6659

在普通印制电路板的布线中由于信号是低速信号,所以在3W原则的基本布线规则下按照信号的流向将其连接起来,一般都不会出现问题。但是如果信号是100M以上的速度时,布线就很有讲究了。由于最近布过速度高达300M的DDR信号,所以仔细说明一下DDR信号的布线原则和技巧。

2019-03-24 10:00:06 6902

6902

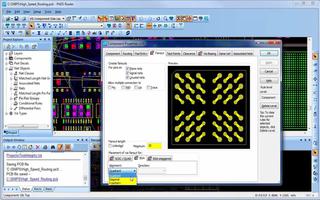

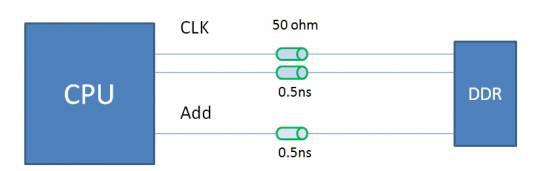

PADS 为高速网络布线提供了一个可扩展的环境,在该环境中可进行交互和自动两种模式。高速网络的规则,例如匹配长度、差分对等,非常容易设置。在布线过程中,您将得到针对关键和敏感网络的实时布线长度反馈。PADS 高速布线可成为提高您 PCB 设计生产率的“利器”。

2019-05-14 06:02:00 3230

3230

在现代高速数字电路的设计过程中,工程师总是不可避免的会与DDR或者DDR2,SDRAM打交道。DDR的工作频率很高,因此,DDR的布线(或者Layout)也就成为了一个十分关键的问题,很多时候,DDR的布线直接影响着信号完整性。下面本文针对DDR的布线问题(Layout)进行讨论。

2019-06-08 14:35:00 4347

4347 他们很少用奇技淫巧。他们写的代码质量高,并清楚知道代码会如何演化,对整个代码结构胸有成竹。他们最多编写一个设计文档,他们的代码就是文档。

2019-07-18 10:09:06 1738

1738 、消费多元化,电子商务完善、整装渠道崛起、商业成本提升等方面的影响,现今家居建材行业的生意越来越难做。这两年来,面对该如何转型破局的问题,行业及大部分企业从开始的胸有成竹逐渐变得迷茫和怀疑。 厚积薄发 隐形巨头的智慧商道 被誉为

2019-12-09 17:50:28 267

267 DDR布线在pcb设计中占有举足轻重的地位,设计成功的关键就是要保证系统有充足的裕量。要保证系统的时序,线长又是一个重要的环节。

2020-01-14 14:46:10 1187

1187 本文档的主要内容详细介绍的是DDR和DDR2与DDR3的设计资料总结包括了:一、DDR的布线分析与设计,二、DDR电路的信号完整性,三、DDR Layout Guide,四、DDR设计建议,六、DDR design checklist,七、DDR信号完整性

2020-05-29 08:00:00 0

0 如果您阅读了许多PCB设计指南,尤其是有关并行协议和差分对布线的指南,则将看到很多关于走线长度匹配的内容。当您需要进行迹线长度匹配时,您的目标是最大程度地减少串行协议中的差分对,并行协议中的多个

2021-01-05 10:56:22 3656

3656

IT史上有一个经典故事。那就是在1943年,IBM的董事长老托马斯·沃森胸有成竹地告诉人们:未来5台计算机就可以满足全世界的市场。

2020-12-15 00:36:22 138

138 DDR4布线之allegro约束规则设置综述

2021-09-08 10:34:29 0

0 受委托让我整理一个关于PCIe的主题分享文章,半月有余实在没办法交差,首先,我自己本身,对PCIe并没有做到胸有成竹,我的PCIe知识也只是停留在理论阶段,我并没有实际做过任何有关PCIe的东西

2022-11-28 10:25:52 6522

6522 根据 50 欧姆阻抗线宽进行布线,尽量从焊盘中心出线,线成直线,尽量走在表层。在需要拐弯的地方做成45 度角或圆弧走线,推荐在电容或电阻两边进行拐弯。如果遇到器件走线匹配要求的,请严 格按照datasheet上面的参考值长度走线。比如,一个放大管与电容之间的走线长度(或电感之间的走线长度)要求等等。

2023-04-19 14:10:50 479

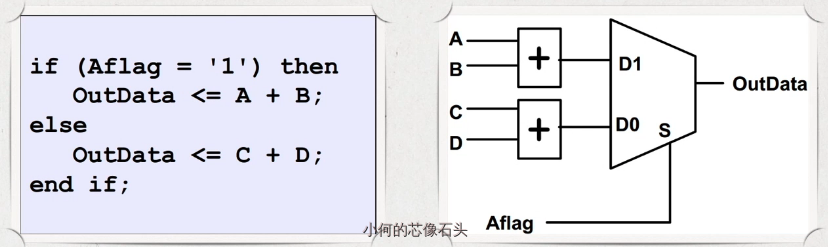

479 HDL 语言仅是对已知硬件电路的文本表现形式编写前,对所需实现的硬件电路“胸有成竹”

2023-06-27 11:16:32 898

898

上期和大家聊的电源PCB设计的重要性,那本篇内容小编则给大家讲讲存储器的PCB设计建议,同样还是以大家最为熟悉的RK3588为例,详细介绍一下DDR模块电路的PCB设计要如何布局布线。 由于

2023-08-17 18:15:02 325

325

上期和大家聊的电源PCB设计的重要性,那本篇内容小编则给大家讲讲存储器的PCB设计建议,同样还是以大家最为熟悉的RK3588为例,详细介绍一下DDR模块电路的PCB设计要如何布局布线。由于

2023-08-18 08:09:43 384

384

SDRAM与DDR布线指南

2022-12-30 09:20:50 10

10 再谈DDR内存布线

2022-12-30 09:21:08 2

2 PCB的DDR4布线指南和PCB的架构改进

2023-12-07 15:15:58 759

759 DDR加终端匹配电阻和不加信号质量的区别 DDR(双倍数据传输速率)是一种常用于计算机内存的高速数据传输技术。在DDR中,终端匹配电阻和信号质量是对于数据传输稳定性至关重要的两个方面。下面将详细

2023-12-29 13:54:22 316

316 话说,转魔方真真是特别解压的事情!虽然未必能如高手那样胸有成竹“咔咔咔"几下,行云流水间就还原。但,谁还不会“抠籽归位”大法呢?不过,当有人为你递上一个不知经历了什么的神奇魔方,又满怀期待

2024-01-13 08:04:39 488

488

德赢Vwin官网

App

德赢Vwin官网

App

评论