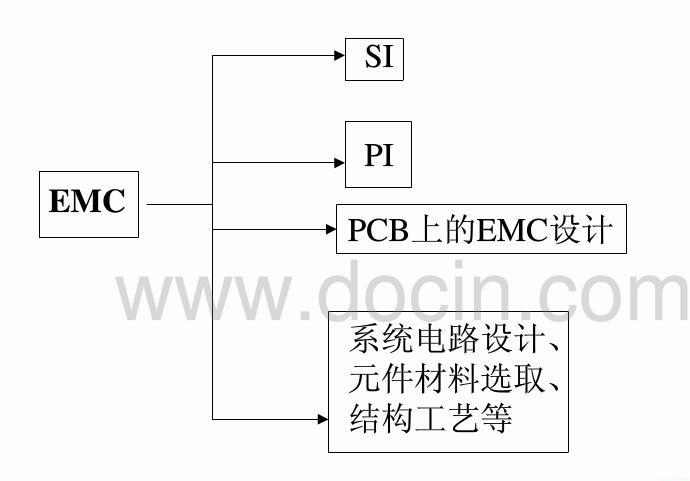

高速PCB走线的3-W原则

- 信号(75276)

- 走线(23300)

- PCB(13204)

相关推荐

9大硬件工程师谈高速PCB信号走线规则

的

PCB

走

线的时候一旦产生了开环的结果,将产生线形天线,增加EMI的辐射强度。图

3开环规则规则四:

高速信号的特性阻抗连续规则

高速信号,在层与层之间切换的时候必须保证特性阻抗的连续,否则会增加EMI的辐射

2018-11-28 11:14:18

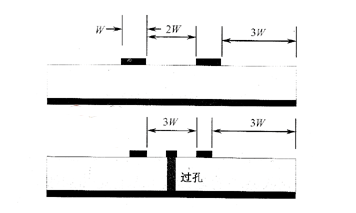

3W原则是什么

3W

原则在

PCB设计中为了减少线间串扰,应保证线间距足够大,当

线中心间距不少于

3倍线宽时,则可保持大部分电场不互相干扰,这就是

3W规则。

3W

原则是指多个

高速信号线长距离

走

线的时候,其间距...

2022-01-26 06:50:22

PCBLAYOUT 中的直角走线、差分走线和蛇形线

布线(Layout)是

PCB设计工程师最基本的工作技能之一。

走

线的好坏将直接影响到整个系统的性能,大多数

高速的设计理论也要最终经过 Layout 得以实现并验证,由此可见,布线在

高速

PCB设计中

2015-01-12 14:53:57

PCBLAYOUT三种特殊走线技巧阐述

、

高速

PCB设计中,蛇形

线没有所谓滤波或抗干扰的能力,只可能降低信号质量,所以只作时序匹配之用而无其它目的。 7、有时可以考虑螺旋

走

线的方式进行绕线,仿真表明,其效果要优于正常的蛇形

走

线。

2018-09-13 15:50:25

PCBLayout3W原则20H原则五五原则

本帖最后由 一生红与黑 于 2012-2-

313:52 编辑

3W

原则:这里

3W是

线与

线之间的距离保持

3倍线宽。你说

3H也可以。但是这里H指的是线宽度。不是介质厚度。是为了减少线间串扰,应

2012-01-17 14:21:41

PCBLayout3W原则20H原则五五原则

3W

原则:4 A2 [

3F4 A. C这里

3W是

线与

线之间的距离保持

3倍线宽。你说

3H也可以。但是这里H指的是线宽度。不是介质厚度。是为了减少线间串扰,应保证线间距足够大,如果

线中心距不少于

3倍

2014-10-28 15:29:44

PCBLayout 中的直角走线、差分走线和蛇形线

布线(Layout)是

PCB设计工程师最基本的工作技能之一。

走

线的好坏将直接影响到整个系统的性能,大多数

高速的设计理论也要最终经过 Layout 得以实现并验证,由此可见,布线在

高速

PCB设计中

2019-06-10 10:11:23

PCBLayout走线秘籍

本帖最后由 maskmyself 于 2017-7-10 10:08 编辑 布线(Layout)是

PCB设计工程师最基本的工作技能之一。

走

线的好坏将直接影响到整个系统的性能,大多数

高速

2017-07-07 11:45:56

PCBLayout三个方面的走线策略

布线(Layout)是

PCB设计工程师最基本的工作技能之一。

走

线的好坏将直接影响到整个系统的性能,大多数

高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在

高速

PCB设计中

2019-05-23 08:52:37

PCBLayout中的专业走线策略

布线(Layout)是

PCB设计工程师最基本的工作技能之一。

走

线的好坏将直接影响到整个系统的性能,大多数

高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在

高速

PCB设计中

2014-08-13 15:44:05

PCBLayout的走线策略怎么优化?

布线(Layout)是

PCB设计工程师最基本的工作技能之一。

走

线的好坏将直接影响到整个系统的性能,大多数

高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在

高速

PCB设计中

2019-08-05 06:40:24

PCB走线不要随便拉

大安全间距等方法。保证信号质量。 d) 有阻抗控制要求的网络应布置在阻抗控制层上,须避免其信号跨分割。 2布线窜扰控制 a)

3W

原则释义

线与

线之间的距离保持

3倍线宽。是为了减少线间串扰,应保证线间距足够大,如果

线中心距不少于

3倍线宽时,则可保持70%的线间电场不互相干扰,称为

3W规则。

2023-12-12 09:23:35

PCB走线与各类信号布线注意事项

,MIPI信号

线应远离其它

高速、高频信号(并行数据

线、时钟

线等),至少保持

3W以上的距离且绝不能平行走

线。对开关电源这一类的干扰源更应远离。 过孔:MIPI信号

线尽量不要打过孔,如有过孔则

线对上的两根

2023-04-12 15:08:27

PCB走线的设计细节详解

好的图像质量的保证。

PCB

走

线如果可能的话,信号

走

线使用6mil,

走线间距使用6mil. 放置0.1uF的退耦电容在对应的DSP电源脚上,并尽可能的靠近。它的

走

线尽可能的粗。电源正极的

走

线最少要

2023-04-13 16:09:54

PCB走线跟哪些因素有关?如何计算PCB走线的线宽?

来说,没有按照正确的方法评估

走

线线宽,可能导致电流过大,烧毁板子

走

线;对于

高速信号来说,没有合适的计算线宽,可能导致阻抗失配,引起信号完整性问题。 2.

PCB

走

线跟哪些因素有关

PCB的

走

线主要跟

2023-04-12 16:02:23

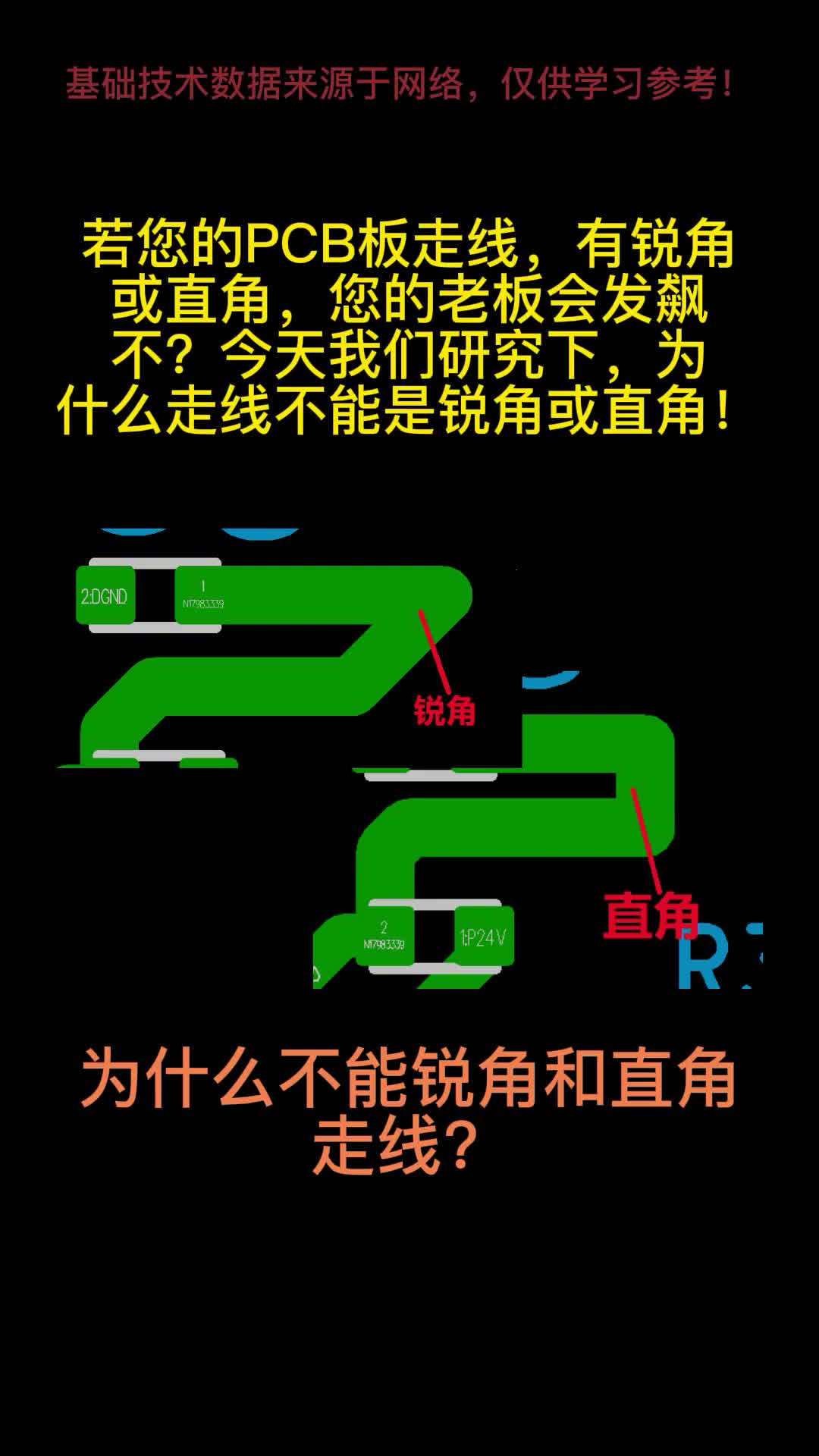

PCB中直角走线的对信号的影响有哪些?

不出来,

高速

PCB设计工程师的重点还是应该放在布局,电源/地设计,

走

线设计,过孔等其他方面。当然,尽管直角

走线带来的影响不是很严重,但并不是说我们以后都可以

走直角

线,注意细节是每个优秀工程师必备的基本素质

2014-11-18 17:29:31

PCB为什么不能直角走线?

采访过苹果公司CEO的B站up主-何同学,近期更新一条视频中,有出现过他自己设计的

PCB图。很多人说他不应该直角

走

线。

PCB为什么不能直角

走线呢?一般在

高速信号

线中,直角

线会带来阻抗的不均匀

2022-09-08 16:54:17

PCB布局之蛇形走线

经常听说“

PCB

走线间距大于等于

3倍线宽时可以抑制70%的信号间干扰”,这就是

3W

原则,信号

线之间的干扰被称为串扰。那么,你知道串扰是怎么形成的吗?当两条

走

线很近时,一条信号线上的信号可能会在另一

2022-12-27 20:33:40

PCB布局和走线的调整

在

pcb的设计过程中,元器件的布局和

走

线的调整是非常重要的一个步骤。恰当的布局可以简化布线的难度,更重要的是可以提高

PCB的电气性能,减少EMC,EMI。 下面是同一个原理图对应的两种不同的布局和

走

2019-10-17 04:37:54

PCB布线有妙招,帮你搞定所有“难缠”的PCB走线

布线(Layout)是

pcb设计工程师最基本的工作技能之一。

走

线的好坏将直接影响到整个系统的性能,大多数

高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在

高速

PCB设计中

2019-08-21 07:30:00

PCB直角走线的影响与计算方式。详解

$ z/ V( f0 C5 c 总的说来,直角

走

线并不是想象中的那么可怕。至少在GHz以下的应用中,其产生的任何诸如电容,反射,EMI等效应在TDR测试中几乎体现不出来,

高速

PCB设计工程师的重点还是

2014-10-28 15:08:55

PCB设计走线注意事项

1.1

PCB板上预划分数字、模拟、DAA信号布线区域。1.2 数字、模拟元器件及相应

走

线尽量分开并放置於各自的布线区域内。1.3

高速数字信号

走

线尽量短。1.4 敏感模拟信号

走

线尽量短。1.5

2019-05-30 06:58:19

PCB设计走线的阻抗控制简介

减少布线层,降低

PCB成本。 当然,这样做的代价是冒一些技术风险,甚至牺牲一半成功率。 对于背板的层叠设计,鉴于常见背板很难做到相邻

走

线互相垂直,不可避免地出现平面长距离布线。 对于

高速背板

2023-04-12 15:12:13

PCB设计高速信号走线的准则分享

硬件工程师做久了自然有自己处理电路板的一套方法,也许不是最好的办法,自己却能理解其中的意义。但是工作中还是要按照最完美的办法进行操作,本期我们就来了解一下关于

高速信号

走

线准则到底有哪几条是你不清楚的?

2020-10-30 08:33:48

PCB设计中,3W原则、20H原则和五五原则都是什么?

`

3W

原则在

PCB设计中为了减少线间串扰,应保证线间距足够大,当

线中心间距不少于

3倍线宽时,则可保持大部分电场不互相干扰,这就是

3W规则。

3W

原则是指多个

高速信号线长距离

走

线的时候,其间距应该遵循

2020-09-27 16:49:19

PCB设计布线中的3种特殊走线技巧

电容,反射,EMI等效应在TDR测试中几乎体现不出来,

高速

PCB设计工程师的重点还是应该放在布局,电源/地设计,

走

线设计,过孔等其他方面。当然,尽管直角

走线带来的影响不是很严重,但并不是说我们以后都可以

2018-09-17 17:31:52

PCB设计技巧Tips11:蛇形走线有什么作用?

的数据;在

走

线时一般遵循

3W法则(绕线的间距要两倍于线宽),这样可消除线间78%的互感,尽量减少因电感变化而引起的阻抗不连续。 另外说明我不是高手,抬得越高摔得越痛;若想见识高手,可以到WWW

2014-11-19 11:54:01

pcb走线

1. 一般规则1.1

PCB板上预划分数字、模拟、DAA信号布线区域。1.2 数字、模拟元器件及相应

走

线尽量分开并放置於各自的布线区域内。1.3

高速数字信号

走

线尽量短。1.4 敏感模拟信号

走

线尽量

2014-03-14 17:44:44

pcb蛇形走线

;=2倍的线宽。PCI板上的蛇行

线就是为了适应PCI 33MHzClock的线长要求。若在一般普通

PCB板中,是一个分布参数的 LC滤波器,还可作为收音机天线的电感线圈,短而窄的蛇形

走

线可做保险丝等等

2019-05-22 02:48:05

高速PCB走线的3-W原则

问题,布线应遵循

3-W

原则。

3-W

原则就是让所有的信号

走

线的间隔距离满足:

走

线边沿之间的距离应该大于或等于2倍的

走线宽度,即两条

走

线中心之间的距离应该大于或等于

走线宽度的

3倍。对于靠近

PCB边缘的

走

线

2018-11-27 15:26:40

高速PCB走线的误区

误区一:认为差分信号不需要地平面作为回流路径,或者认为差分走

线彼此为对方提供回流途径。造成这种误区的原因是被表面现象迷惑,或者对

高速信号传输的机理认识还不够深入。从图1-8-15的接收端的结构可以

2012-12-18 12:03:00

高速PCB走线的误区

误区一:认为差分信号不需要地平面作为回流路径,或者认为差分走

线彼此为对方提供回流途径。造成这种误区的原因是被表面现象迷惑,或者对

高速信号传输的机理认识还不够深入。从图1-8-15的接收端的结构可以

2012-12-19 16:52:38

高速PCB多层板叠层设计原则

多层

PCB通常用于

高速、高性能的系统,其中一些层用于电源或地参考平面,这些平面通常是没有分割的实体平面。无论这些层做什么用途,电压为多少,它们将作为与之相邻的信号

走

线的电流返回路径。构造一个好

2018-11-27 15:14:59

高速PCB布线差分对走线

分对之间的距离;s为差分对两根信号线间的距离;

W为差分对

走

线的宽度;Ff为介质厚度。 使用差分对

走

线时,要遵循以下

原则: · 保持差分对的两信号

走

线之间的距离S在整个

走线上为常数; · 确保D

2018-11-27 10:56:15

高速PCB布线拐角走线

°拐角;另一种方法是用圆角,如图2所示。圆角方式是最好的,45°拐角可以用到10 GHz频率上。值得注意的是,对于45°拐角

走

线,拐角长度最好满足:L≥31

W。 图1直角拐角的高频等效电路 图2拐角

走

线的处理 欢迎转载,信息维库电子市场网(www.dzsc.com):

2018-11-27 10:55:56

高速PCB设计系列基础知识13|原理图走线与设计步骤

上期讲到了

高速

PCB设计中建立元件库的方法元件放置完成后接下来的重点便是连接走

线▼▼原理图

走

线▼▼在原理图

走

线中有导线的连接和总线的连接。执行Place指令下的操作,可以用以添加连线(Wire

2017-03-02 11:55:35

高速PCB设计解决EMI问题的九大规则

。也就是说,同层的布线的宽度必须连续,不同层的

走

线阻抗必须连续。 规则五:

高速

PCB设计的布线方向规则 相邻两层间的

走

线必须遵循垂直走

线的

原则,否则会造成线间的串扰,增加EMI辐射。 简而言之

2016-01-19 22:50:31

高速PCB设计调整走线长度

。 而绝对的要求是控制两个器件之间的

走

线延迟为某一个值,比如器件A、B之间的延迟为Ins,而这样的要求往往由

高速电路设计者提出,而由

PCB工程师去实现。要满足这个要求,就必须知道信号的传播速度c但需要

2018-11-27 15:22:54

高速中的蛇形走线在不同应用场合的不同作用

PCI-Clk,AGPCIK,IDE,DIMM等信号

线。(2)若在一般普通

PCB板中,除了具有滤波电感的作用外,还可作为收音机天线的电感线圈等等。如2.4G的对讲机中就用作电感。(

3)对一些信号布线长度要求

2019-03-22 06:20:09

高速中的蛇形走线适合什么情况

高速中的蛇形

走

线,适合在那种情况?有什么缺点没,比如对于差分走

线,又要求两组信号是正交的。回答:”蛇形

走

线,因为应用场合不同而具不同的作用:(1)如果蛇形

走

线在计算机板中出现,其主要起到一个滤波电感

2019-05-09 07:35:35

高速串行总线走线有什么难点?

差分走

线,差分走

线严格按照差分仿真所得出的结论,2S,和

3W的要求进行把控

走

线,其目的在于增强信号质量的耦合性能,减少信号的回损。

2019-09-11 11:52:29

高速电路PCB的网络、传输线、信号路径和走线

Netl。 但是,对于

高速信号,如第

3章所讲的就完全不是这样了,一个信号从引脚A输出,到达D可能完全失真,而且也完全不考虑信号电流是如何返回的,所以需引入传输

线的概念。传输

线的原理在第

3章已有详细

2018-11-23 16:05:07

高速电路设计学习

完整性问题;

3、蛇形

线,满足

3W

原则,高频关键信号尽量不

走蛇形

线;4、尽量减少

走

线分叉,对于一驱多,

走成菊花链来减少stub;5、控制过孔的数目,过孔呈容性,过多的过孔会导致信号完整性问题;6、对于晶振

2020-12-21 09:23:34

MIPI走线的6大法则

时,一般需要保持DP/DN在

走

线的过程中保持等距,保证一定的耦合程度,但是需要弄清楚的时,等长的优先级是高于等距的。且在

走

线时,

线对之间要保持2

W的距离。

3、参考层MIPI

走

线应该保持连续的参考层,且最好

2018-05-21 11:53:33

PCBLayout中的走线方法及建意

PCBLayout中的

走

线方法

走

线的好坏将直接影响到整个系统的性能,布线(Layout)是

PCB设计工程师最基本的工作技能之一。大多数

高速的设计理论也要最终经过Layout得以实现并验证,由此可见

2010-03-16 09:23:41

USBPCB设计建议和差分布线的原则

为了保证良好的信号质量, USB 2.0 端口数据信号

线按照差分线方式

走

线。为了达到USB 2.0

高速480MHz 的速度要求,建议

PCB布线设计采用以下

原则:差分数据

线

走

线尽可能短、直,差分数据

线对内

走线长度严格等长,

走线长度偏差控制在±5mil 以内。

2019-05-23 08:52:33

[原创]PCBLayout中的走线策略

PCBLayout中的

走

线策略布线(Layout)是

PCB设计工程师最基本的工作技能之一。

走

线的好坏将直接影响到整个系统的性能,大多数

高速的设计理论也要最终经过Layout得以实现并验证,由此可见

2009-08-20 20:58:49

[转]PCB在设计布线中的3种特殊走线技巧

,其产生的任何诸如电容,反射,EMI等效应在TDR测试中几乎体现不出来,

高速

PCB设计工程师的重点还是应该放在布局,电源/地设计,

走

线设计,过孔等其他方面。当然,尽管直角

走线带来的影响不是很严重,但

2018-07-08 13:28:36

【PCB小知识 6 】3W原则

PCB设计中,

3W

原则并不能完全满足避免串扰的要求。按实践经验,如果没有屏蔽地线的话,印制信号

线之间大于lcm以上的距离才能很好地防止串扰,因此在

PCB线路布线时,就需要在噪声源信号(如时钟

走

线)与非噪声

2015-12-12 20:37:31

【PCB经验分享】走线的参考平面在哪?

很多人对于

PCB

走

线的参考平面感到迷惑,经常有人问:对于内层

走

线,如果

走

线一侧是VCC,另一侧是GND,那么哪个是参考平面?要弄清楚这个问题,必须对了解传输

线的概念。我们知道,必须使用传输

线来分析

2014-11-17 10:07:29

【快点PCB-3W和20H原则】

要强制使用

3W

原则,而且还要进行屏蔽地线包地处理,以防止串扰的发生。另外,不是所有的

PCB上的

走

线都必须遵照

3W布线

原则。使用这一设计指导

原则,在

PCB布线前,决定哪些条

走

线必须使用

3W

原则是十分重要

2016-09-06 14:43:52

【转】高速PCB之EMC 47原则

完整地平面相邻,优选两地平面之间。原因:关键信号

线一般都是强辐射或极其敏感的信号

线,靠近地平面布线能够使其信号回路面积减小,减小其辐射强度或提高抗干扰能力。

原则

3:对于单层板,关键信号

线两侧应该包地处

2018-11-23 16:21:49

三种特殊的PCB走线技巧

布线(Layout)是

PCB设计工程师最基本的工作技能之一。

走

线的好坏将直接影响到整个系统的性能,大多数

高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在

高速

PCB设计中

2019-03-18 21:38:12

为什么PCB走线中避免出现锐角和直角?

,阻抗不连续,引起信号反射。为了减小不连续性,要对拐角进行处理,有两种方法:切角和圆角。圆弧角的半径应足够大,一般来说,要保证:R>

3W。锐角、直角

走

线锐角

走

线一般布线时我们禁止出现,直角

走

线一般

2017-08-12 15:09:54

仿真小技巧~高速信号如何选择走线层?

`表层

走

线与内层

走

线更为规范的说法应该是微带

线与带状

线。两种

走

线方式因为介质和参考面不同,会存在比较明显的差异。对于长距离传输的

高速信号,尤其是背板之类的,需要特别注意损耗带来的影响,避免高频分量

2020-03-09 10:57:00

你知道高速叠层设计原则有哪些吗

4x7628pp,滑片2mm板厚极限14层,1.6mm一般最多12层,做14层阻抗不易控制

高速要求:信号层与地层尽量近电源与地尽量近,并有一处相邻保证地平面足够大,并完整保证相邻的两个信号层尽量远,布线

走

线为交叉

走

线,尽量满足

3W规则,不行则相互错开信号层如果以VCC为参考平

2022-03-02 06:09:06

信号在PCB走线中传输时延(下)

,相邻

走线间的影响就越小,

走线间距尽量满足

3W

原则。 2,使耦合长度尽量短。相邻传输

线平行走线长度越长串扰越大,

走

线时候尽量减小相邻

线平行走线长度;对于相邻层

走

线尽量采用相邻层垂直走

线。

3,

走

线尽量

2014-10-21 09:51:22

原创|高速信号PCB设计处理的通用原则

通用的

高速信号

PCB设计处理

原则有:(1)层面的选择:处理

高速信号优先选择两边是GND的层面处理(2)处理时要优先考虑

高速信号的总长(

3)

高速信号Via数量的限制:

高速信号允许换一次层,换层时加

2017-02-07 09:40:04

带你读懂PCB设计的3W原则、20H原则及五五原则

~10mils),

3W是够了;但兩层板,

走

线与参考层高度距离(45~55mils),

3W对

高速信号

走

线可能不够。

3W

原则一般是在50欧姆特征阻抗传输线条件下成立。

3W

原则是指多个

高速信号线长距离

走

线

2019-05-08 08:30:00

我的PCB走线经验归纳

在

PCB设计中,布线是完成产品设计的重要步骤,

PCB

走

线的好坏直接影响整个系统的性能,布线在

高速

PCB设计中是至关重要的。布线的设计过程限定高,技巧细、工作量大。

PCB布线有单面布线、 双面布线

2014-12-16 09:47:09

电源PCB设计指南:整体布局及走线原则

,一般电路应尽可能使元器件平行排列,这样不仅美观,而且装焊容易,易于批量生产。三、布线

原则1、输入输出端用的导线应尽量避免相邻平行,最好加线间地线,以免发生反馈藕合。2、

走

线的宽度主要由导线与绝缘基板间

2020-08-01 07:54:14

硬件工程师谈高速PCB信号走线的九个规则

网络,在多层的

PCB

走

线的时候一旦产生了开环的结果,将产生线形天线,增加EMI的辐射强度。 图

3开环规则 规则四:

高速信号的特性阻抗连续规则

高速信号,在层与层之间切换的时候必须保证特性阻抗

2018-09-20 10:38:01

解决高速PCB设计EMI(电磁干扰)的九大规则

设计的布线方向规则相邻两层间的

走

线必须遵循垂直走

线的

原则,否则会造成线间的串扰,增加EMI辐射。简而言之,相邻的布线层遵循横平竖垂的布线方向,垂直的布线可以抑制线间的串扰。规则六:

高速

PCB设计中的拓扑结构

2017-11-02 12:11:12

详解PCB直角走线的影响与计算方式。

! j9 K# {: E 总的说来,直角

走

线并不是想象中的那么可怕。至少在GHz以下的应用中,其产生的任何诸如电容,反射,EMI等效应在TDR测试中几乎体现不出来,

高速

PCB设计工程师的重点还是应该放在

2014-11-07 09:40:54

一文详解高速PCB的EMC设计原则

本文主要介绍了

高速

PCB的EMC设计

原则,首先介绍了

PCB设计的EMC基础知识,其次阐述了

PCB中EMC设计的重要性以及

PCB中EMC设计相关项,最后详细的介绍了关于

高速

PCB的EMC设计的47项

原则,具体的跟随小编一起来了解一下。

2018-05-25 15:58:19

4664

4664

4664

4664

德赢Vwin官网 App

德赢Vwin官网 App

评论