一、信号走线下方添加公共接地层

根据经验,在信号走线下方添加一个公共接地层,这样可以确保PCB中任意2个接地点之间的阻抗最小。

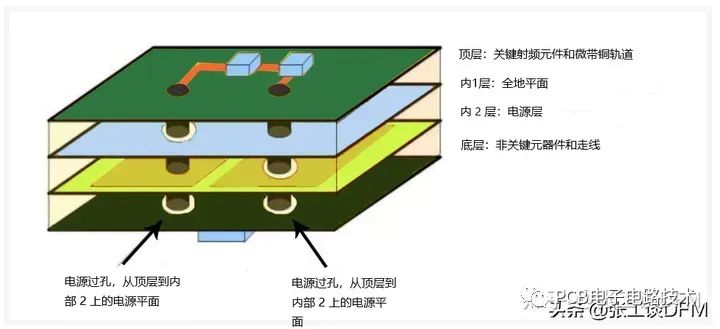

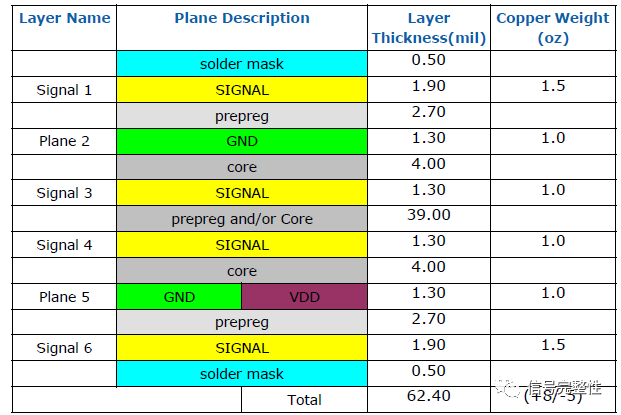

当靠近地平面的外层用于安装高速组件时,如果用微带线或者共面线的RF组件,另一侧安装不太重要的组件。第二个内层用于电源平面,电源平面尽可能大,这样可以降低阻抗。

4层PCB结构

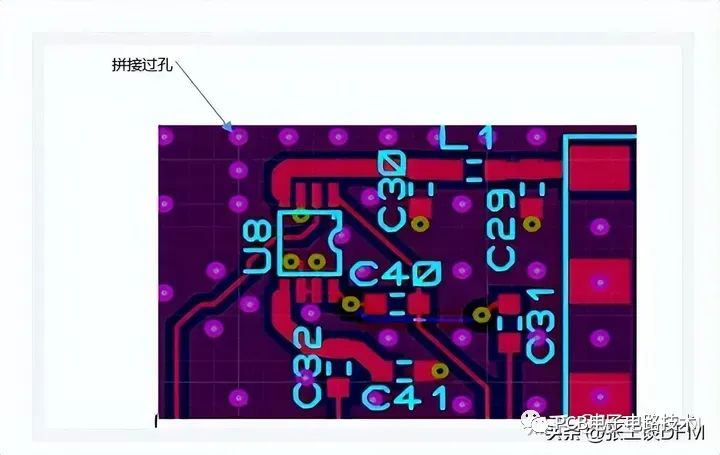

如果想要降低成本,那最好的就是双面PCB,这个时候就是通过大量过孔互连的走线两侧添加地平面,如果下图所示。

显示拼接接地层的过孔的PCB

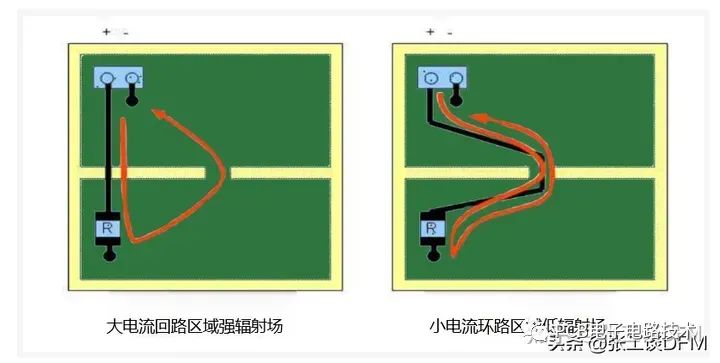

在单点互连的逻辑和vwin 组件设置隔离的接地平面可以降低接地平面的噪声。这样的话就需要将一个区域到另一个区域的走线都排在互联点的上方。如下图所示。如果不这样的话,就可以添加天线,发送或者接收杂散信号。建议使用完整的单一接地。

返回电流回路

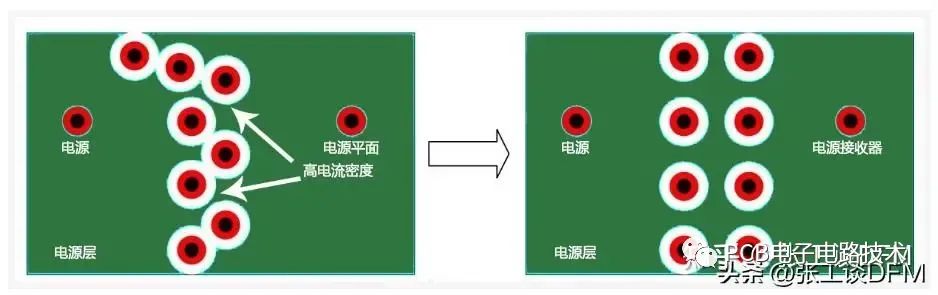

二、在网格中添加过孔来避免热点

信号过孔会在电源层和接地层中产生空隙。过孔定位不当会产生电流密度增加的平面区域,这些区域称为热点。

必须要避免这些热点,最好的解决方法是如下图所示,将过孔放置在网格中,并在过孔之间留出足够的空间供电源层通过,过孔间隔15密耳。

以网格图案布线过孔以避免热点

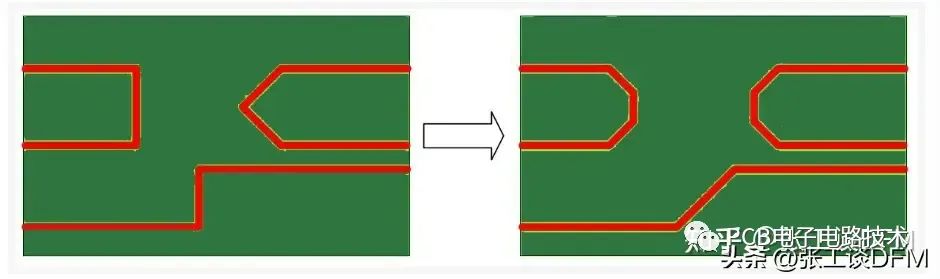

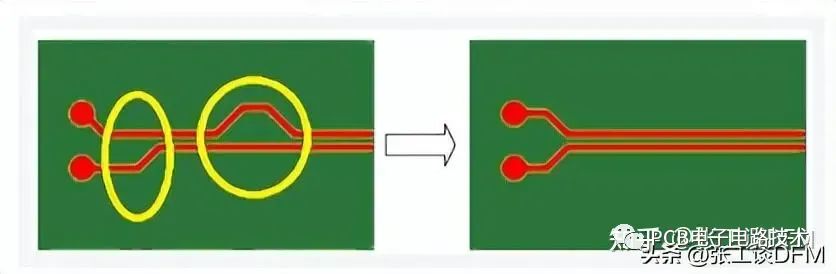

三、在路由高速信号,135°走线弯曲而不是90°

在路由高速信号时,弯曲应保持最小。如果需要弯曲,建议135°而不是90°。如下图(右侧)所示,在九十°时,不能保证顺利的PCB蚀刻。此外非常高速的锋利边缘充当天线。

保持135°弯曲而不是90°

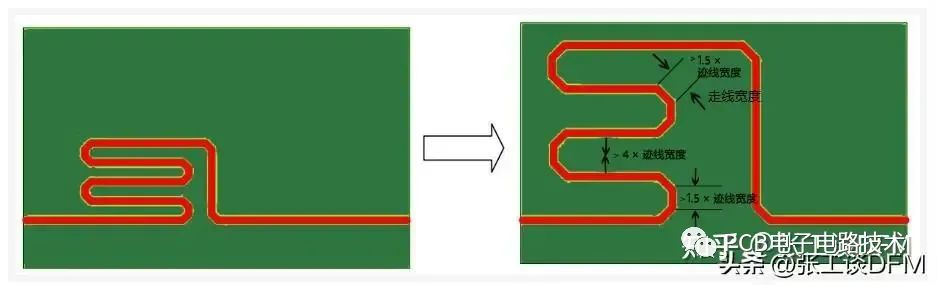

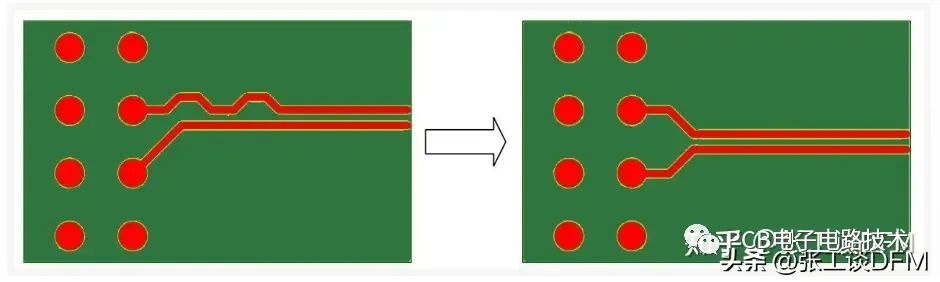

为了达到特特定的走线长度,需要蛇形走线。如下图所示,同一走线中相邻铜之间的最小距离必须保持为走线宽度的4倍,每段弯曲应为走线宽度的1.5倍。

保持弯曲处的最小距离和线段长度

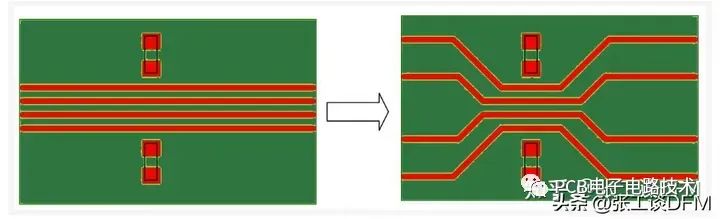

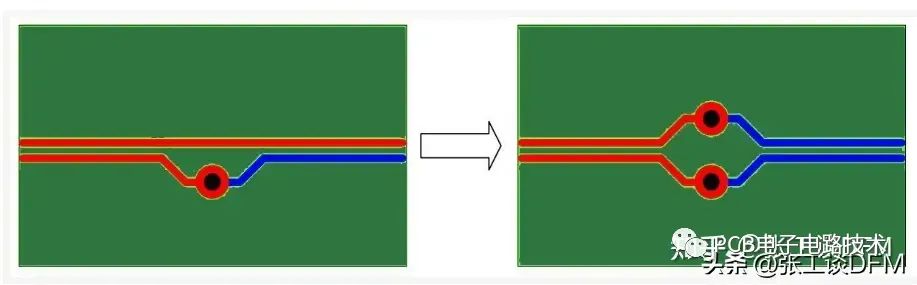

四、增加瓶颈区域外的信号之间的距离以避免串扰

走线之间应该保持最小距离,最大程度地减少串扰。串扰水平取决于两条走线的长度和距离。在某些区域,走线的布线达到了走线比预期更近的瓶颈。这个时候就需要增加额外信号之间的距离。也就是满足最低要求,间距也可以再增加一点。

尽可能增加走线之间的间距

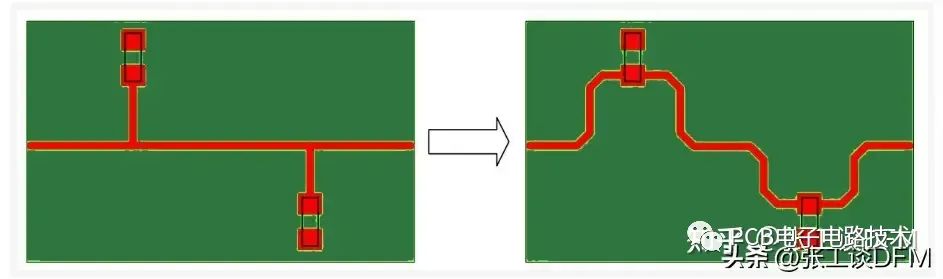

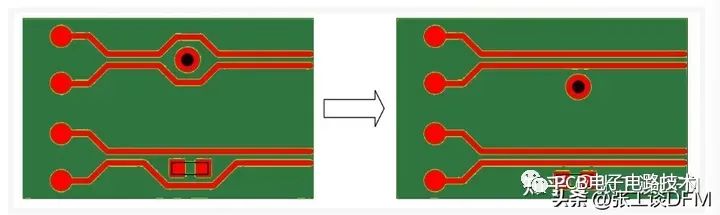

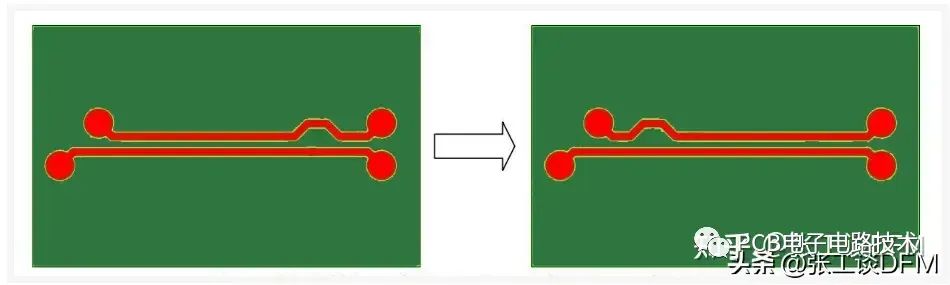

五、增加菊花链路来保持信号完整性,避免长存根走线

长短截线可能充当天线,从而增加符合EMC标准的问题。存根走线还会产生信号完整性产生负面影响的反射。高速信号上的上拉或下拉电阻是存根的常见来源。如果需要此类电阻,就需要此类电阻将信号路由为菊花链。如下图所示:

通过实施菊花路由避免存根跟踪

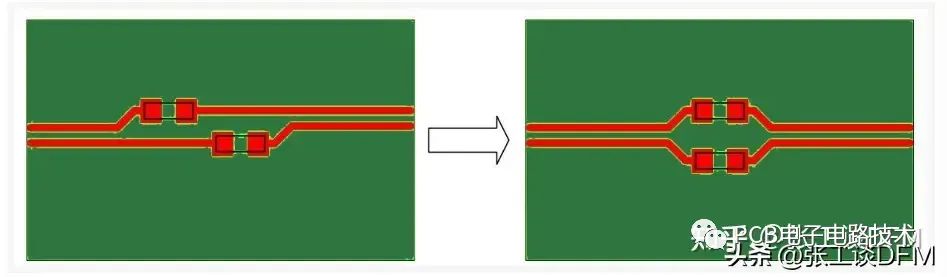

六、不要在差分对之间放置组件或者过孔

将高速差分对互相平行布线时,它们之间应该保持恒定距离。这个距离有助于实现指定的差分阻抗。因尽量减少因焊盘入口而扩大指定间距的区域,差分对应对称布线。

对称布置差分对并保持信号平行

在设计的时候不应该在差分对之间放置任何组件或过孔。即使信号如下图所示对称布线。在差分对之间放置元件和过孔可能会导致EMC问题和阻抗不连续。

不要在差分之间放置组件或者过孔

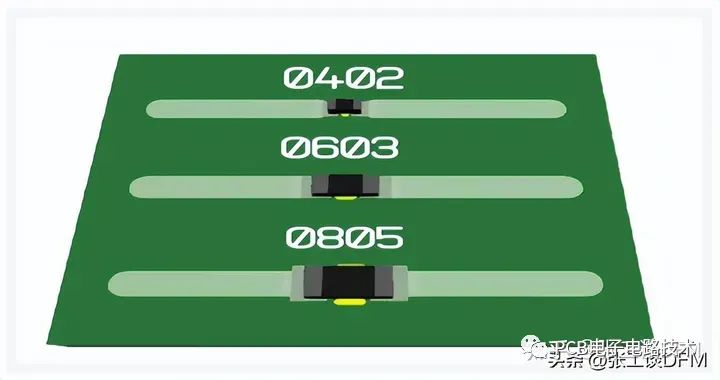

一些高速差分对需要串联耦合电容,容应对称放置。电容和焊盘产生阻抗不连续性。0402电容尺寸0603。必须避免使用0805或C型等封装较大的封装。

对称放置耦合电容

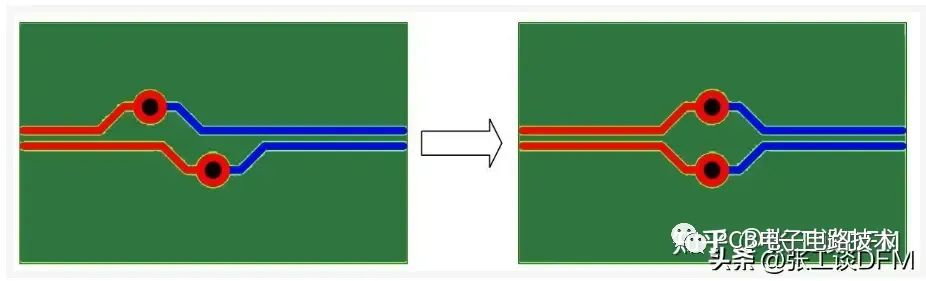

由于过孔在阻抗中引入了巨大的不连续性,因此必须减少过孔的数量并且应该对称放置。

对称放置过孔

布线差分对时,2条走线布线应该在同一层,以满足阻抗要求。如下图所示,此外,走线中应包含相同数量的过来。

在同一层布线对并放置相同数量的过孔

七、结合长度匹配以实现正信号和负信号之间的紧密延迟偏差

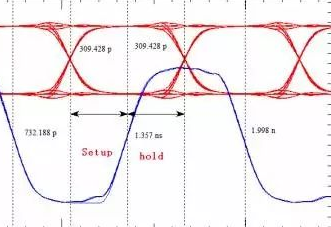

高速接口对到达目的地的时间有额外的要求,称为不同走线和信号对之间的时钟偏差。例如,在高速并行总线中,所有数据信号都需要在一个时间段内达到,以满足接收器的建立和保持时间要求。

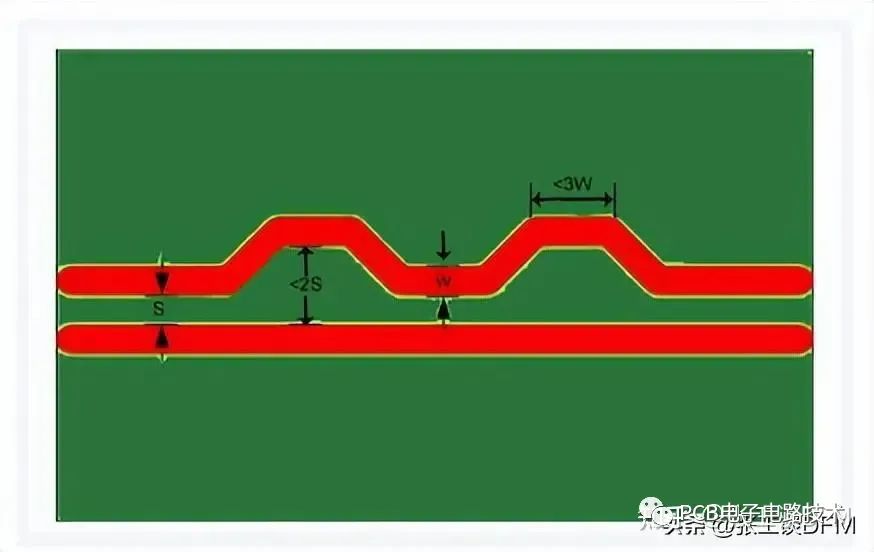

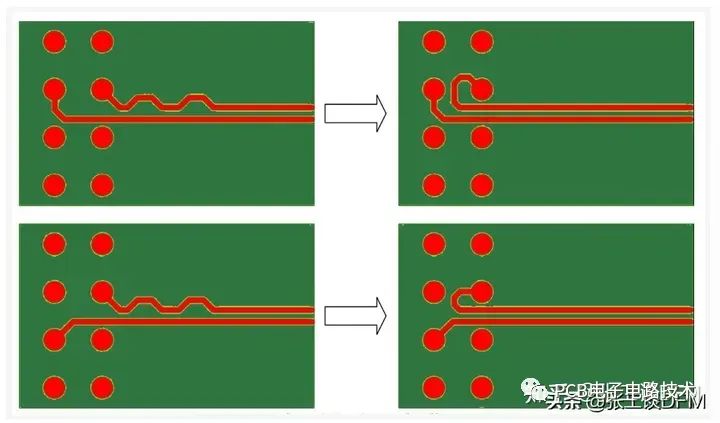

差分对信号要求正负信号走线之间的延迟偏差非常小。因此,使用蛇纹石来补偿任何长度差异,必须要仔细设计蛇形走线的几何形状,如下图,减少阻抗不连续性。

使用推荐的蛇形走线几何结构

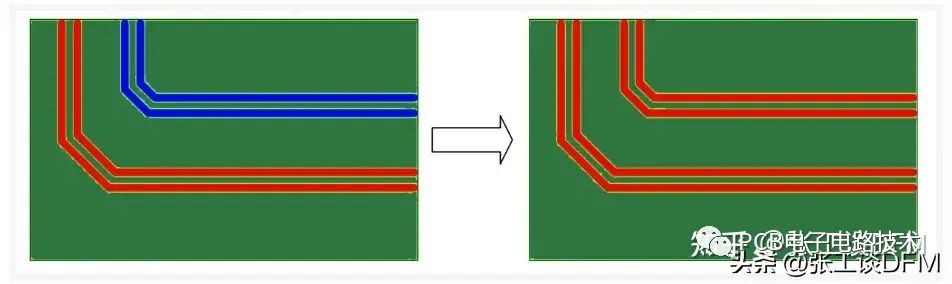

在设计的时候应该将蛇形走线放置在长度不匹配的根部。这确保正负信号分量通过连接到同步传播,如下图所示:

将长度校正添加到源的不匹配点

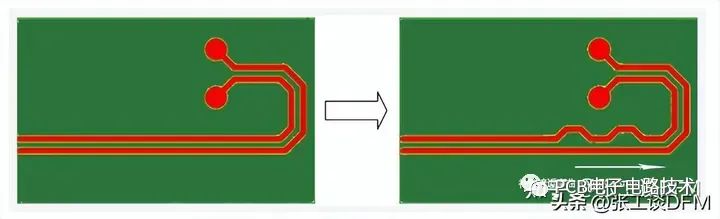

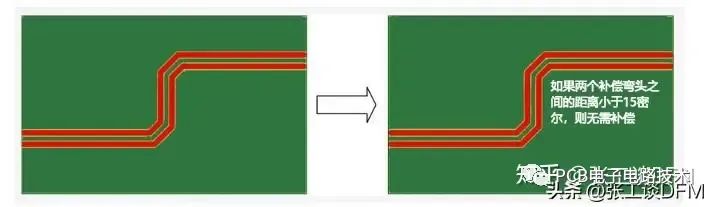

弯曲通常时长度不匹配的来源,补偿器应该非常靠近弯曲处放置,最大距离为15mm,如下图所示:

将长度补偿靠近弯曲处放置

通常2个弯曲处相互补偿,如果弯曲小于15mm,则不需要使用蛇纹石进行额外补偿。信号的异步传输距离不应超过5mm。

弯曲可以相互补偿

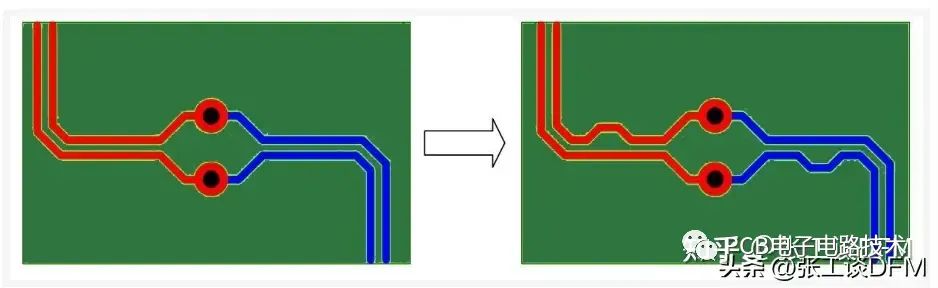

差分对连接的每个阶段中的失配应单独匹配。在下图中,过孔将差分对分成2段,此处需要单独补偿弯曲。这样确保了正信号和负信号通过过孔同步传播。

应在每个段中补偿长度差异

PCB各层的信号速度并不相同,由于很难找出差异,如果需要匹配,最好在同一层走线。

同一接口内的线对最好在同一层布线

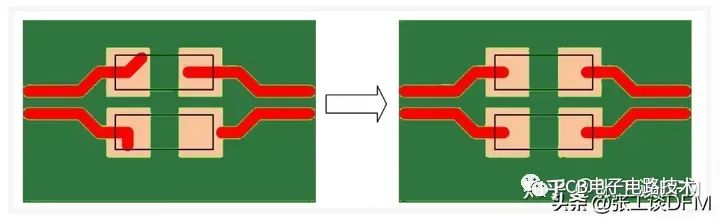

在下图中,电容焊盘内部的走线长度不等。即使信号不使用内部走线。一些CAD 工具也会将其视为长度计算的一部分,并显示正信号和负信号之间的长度差。为了尽量减少这种情况,确保2个信号的焊盘入口相等。

需要注意一些CAD工具中遇到的长度计算问题

如下图所示,首选差分对信号的非对称分流,尽可能避免蛇形走线。

差分对的对称突破

如果焊盘之间有足够的空间,则可以为较短的走线包含小环而不是蛇形走线,过孔优于蛇形走线。

差分对的首选分线

八、不要在分割平面上路由信号

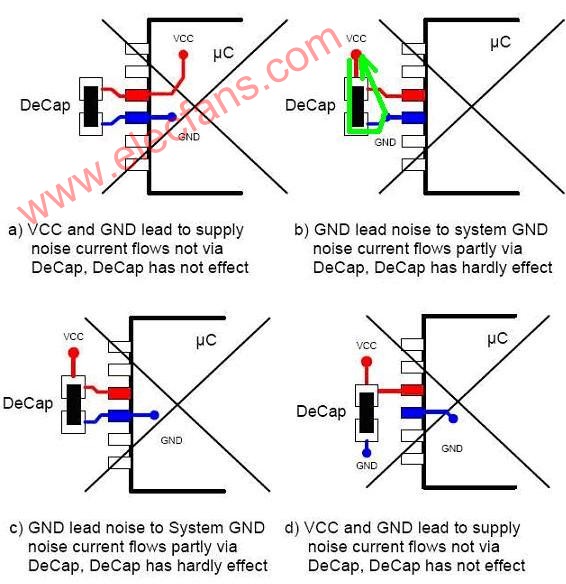

不正确的信号返回会导致噪声耦合和EMI问题。设计人员在路由信号时应始终考虑信号返回路径。电源轨和低速信号采用最短返回电流路径。

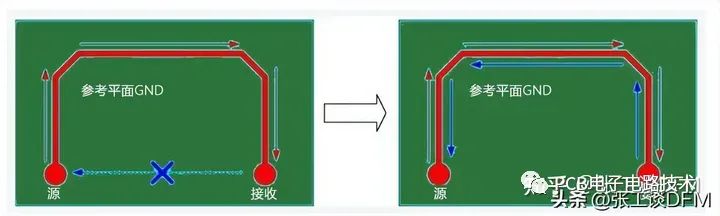

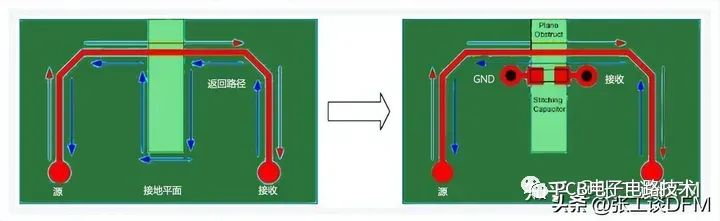

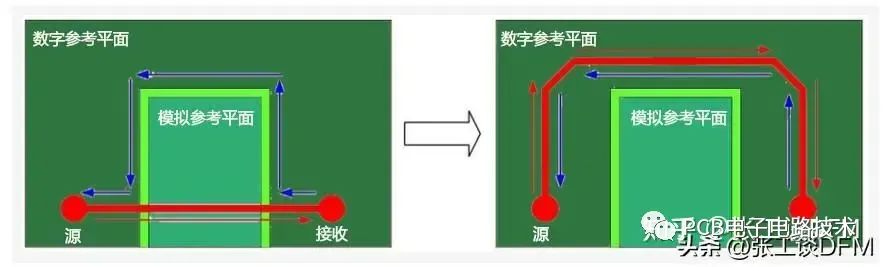

如下图所示,与此相反,高速信号的返回电流试图跟随信号路径。

在高速PCB中,返回电流试图跟随信号路径

不应在分离平面上路由信号,因为返回路径无法跟随信号走线。如下图,如果一个平面在接收器和源之间分开,就需要围绕它布线信号走线,如果信号的前向和返回路径是分开的,则它们之间的区域将充当环形天线。

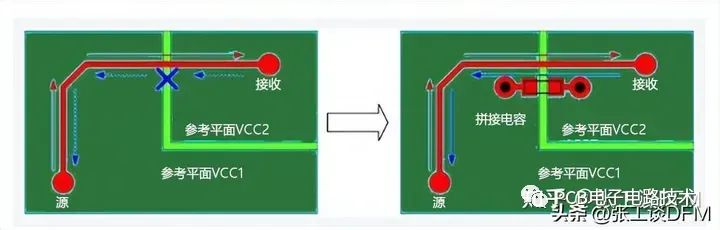

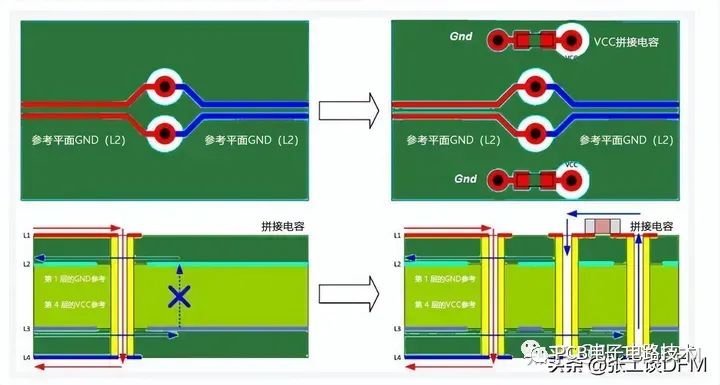

如果需要在2个不同的参考平面上路由信号,则应加入拼接电容。拼接电容使返回电流能够从一个参考平面传输到另一个参考平面。电容应该靠近信号路径放置,以便正向路径和返回i路径之间的距离较小。通常拼接电容的之在10nF和100nF之间。

在分割平面上放置拼接电容

一般情况下,必须避开平面障碍物和平面槽。如果需要绕过此类障碍物,就需要入下所示使用拼接电容。

在平面障碍物上布线时合并的拼接电容

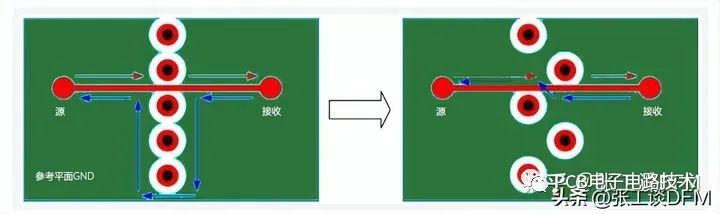

设计人员在布线高速信号时应注意参考平面中的空洞。如下图所示,当奖过孔靠近放置时,参考平面中会产生空洞。应该通过确保过孔之间有足够的间隙来避免较大的空隙区域。最好放置较少的接地和电源过孔,以减过孔间隙。

避免过孔平面空隙

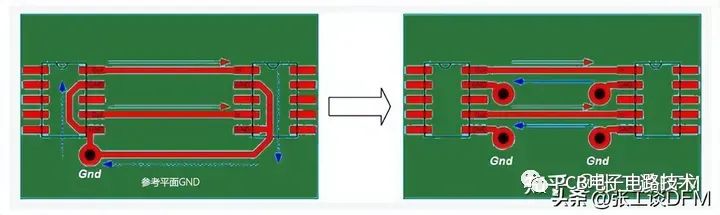

返回路径在信号的源和接收器处。在下图中,左侧的设计被认为是不好的设计。由于原籍侧只有一个接地过孔,因此返回电流无法预期返回参考接地平面。返回路径是存在于顶层的接地连接。

现在的问题是信号走线的阻抗是根据接地平面而不是顶层的接地走线计算的。因此,必须在信号的源端和汇端放置接地过孔,允许返回电流返回接地平面。如下图右侧所示。

放置接地过孔时应考虑返回路径

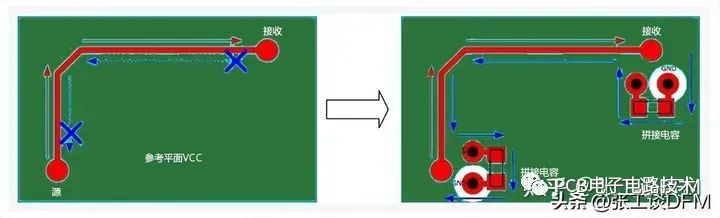

当电源平面被视为信号的参考时,信号应该通过电源平面传输回去,信号以源和汇中的地为参考。要将参考切换到电源层,应在灌电流和源电流处加入拼接电容。

如果接收器和源使用相同的电源轨供电,那么旁路电容可以用作拼接电容。如果靠近信号开始/出口点放置。如下图所示,拼接电容的理想值介于10nF和100nF之间。

使用电源平面作为参考时使用拼接电容

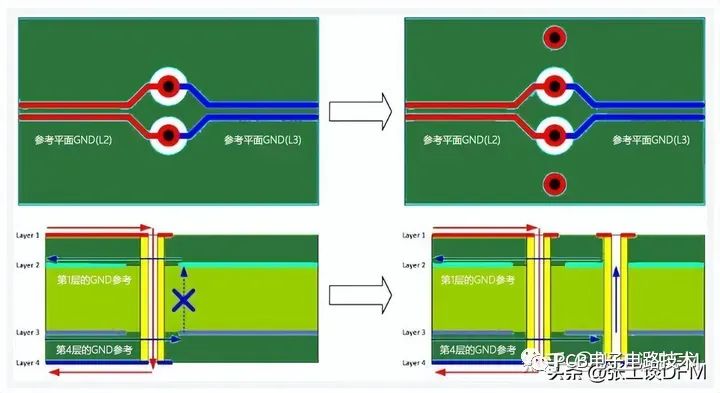

当差分信号切换一层时,参考地平面也会切换。因此,在靠近层变化过孔的位置添加拼接过孔。如下图所示,允许返回电流改变接地层,处理差分信号时,开关接地过孔对应对称放置。

当信号改变接地参考时使用拼接电容

当信号切换到具有不同参考平面的不同层时,应实施拼接电容。这允许返回电流通过拼接电容从地流向电环层,如下图所示,此外,当考虑差分对时,拼接电容的放置和布线应该是对称的。

当信号参考平面发生变化时加入拼接电容

设计的时候,不应该在参考平面的边缘或靠近PCB边界的地方布线高速信号,这回对走线阻抗产生不利影响。

九、分离模拟和数字地平面降低噪声

定义单独的模拟和数字接地部分可以在原理图中轻松确定哪些组件和引脚应连接到数字地部分,哪些组件和引脚应连接到模拟接地部分。这类型的设计可以通过放置2个不同的地平面作为参考来布线。

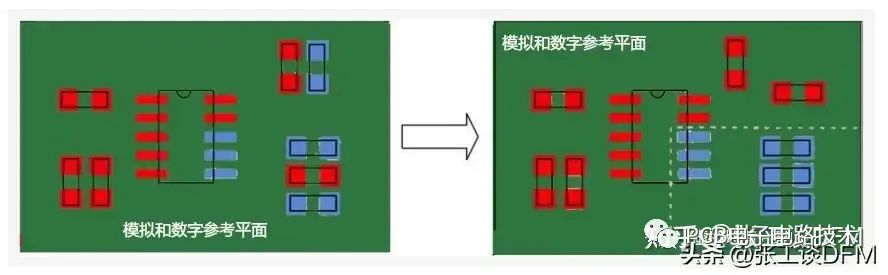

两个平面应准确放置,数字和模拟组件应放置在相应部分下方,如下图所示。

需要谨慎进行电源平面拆分

混合信号电路需要在单点连接模拟地和数字地。在原理图,还是建议在模拟和数字部分之间放置铁氧体磁珠或0Ω电阻。

数字地和模拟地的合并应靠近集成电路放置。在具有分离平面的混合信号设计中,数字信号不应该通过模拟接地平面布线,模拟信号不应该通过数字地平面布线。

数字信号不应该穿过模拟地平面

十、在模拟地和数字地之间虚拟第划分布局

在虚拟分割中中,模拟地和数字地在原理图中没有分开。此外,2个接地域在布局中也没有电气分离。在实际布局时是分开的,即在模拟地和数字地绘制了一个假想的分割线。这里应该仔细考虑虚拟分割平面的正确一侧来放置组件。

应使用虚拟平面分割仔细放置组件

在设计的时候应该牢记2个地之间的虚线。数字和模拟信号走线不允许越过虚拟分割线。虚拟分割线不应具有复杂的形状。因为没有平面障碍物来保模拟和数字返回电流分离。

十一、组件的宽度接近走线宽度,可以实现最佳高速性能

PCB设计从原理图开始,特别是元件的选择,SMD是首选,因为更小的元件和更短的导线带来更稳定的高速性能。

如果组件的宽度接近走线宽度,就可以实现最佳的高速性能。这有利于降低走线和元件焊盘之间的阻抗匹配问题。

编辑:黄飞

德赢Vwin官网

App

德赢Vwin官网

App

评论