请教各位大师:FPGA 设计的一块8层板,2层电源,2层地,4sig。 FPGA 信号有80M. 想问一下怎么叠层合适? 电源层有很多空余位置布电源好,还是布地线好?信号层的空余地方要布地线吗? 谢谢。

2015-07-18 11:07:25

的4层 PCB叠层中,我们可以将第1层的铜面积减少到最小,而不会大大降低设计的热性能。被释放的第1层铜面积因此可以用于安装其他器件、路由路径等。原作者:booksoser 汽车电子工程知识体系

2023-04-20 17:10:43

结构的对称性。常用的叠层结构:下面通过4层板的例子来说明如何优选各种层叠结构的排列组合方式。对于常用的4层板来说,有以下几种层叠方式(从顶层到底层)。(1)Siganl_1(Top),GND

2015-03-06 11:02:46

表3中可以知道,八层板相比六层板并没有增加信号的走线层,而是多了两个敷铜层,所以可以优化系统的EMC性能。十层板设计表4十层板叠层示例十层的PCB绝缘介质层很薄,信号层可以离地平面很近,这样就非常好

2016-05-17 22:04:05

的放置位置以及如何在这些层上分布不同的信号。这就是多层PCB层叠结构的选择问题。 层叠结构是影响PCB板EMC性能的一个重要因素,也是抑制电磁干扰的一个重要手段。本文介绍多层PCB板层叠结构的相关内容

2018-09-17 17:41:10

,再确定内电层的放置位置以及如何在这些层上分布不同的信号。这就是多层PCB层叠结构的选择问题。层叠结构是影响PCB板EMC性能的一个重要因素,也是抑制电磁干扰的一个重要手段。本文介绍多层PCB板层

2016-08-24 17:28:39

本帖最后由 lee_st 于 2017-10-31 08:48 编辑

PCB叠层设计及阻抗计算

2017-10-21 20:44:57

PCB叠层设计及阻抗计算

2017-09-28 15:13:07

PCB叠层设计及阻抗计算

2016-06-02 17:13:08

的放置位置以及如何在这些层上分布不同的信号。这就是多层PCB层叠结构的选择问题。层叠结构是影响PCB板EMC性能的一个重要因素,也是抑制电磁干扰的一个重要手段。本节将介绍多层PCB板层叠结构的相关内容

2018-09-18 15:12:16

对于如何选择设计用几层板和用什么方式的叠层,要根据板上信号网络的数量,器件密度,PIN密度,信号的频率,板的大小等许多因素。对于这些因素我们要综合考虑。对于信号网络的数量越多,器件密度越大,PIN

2020-01-03 08:58:20

、EMC、制造成本等要求有关。对于大多数的设计,PCB的性能要求、目标成本、制造技术和系统的复杂程度等因素存在许多相互冲突的要求,PCB的叠层设计通常是在考虑各方面的因素后折中决定的。高速数字电路和射须电路通常采用多层板设计。

2019-09-17 14:11:49

PCB防范ESD的措施

2021-03-30 07:23:45

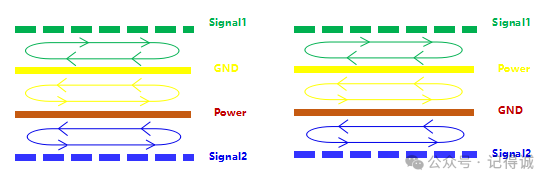

的地参考层连接起来,如下图所示。

五、ESD优化建议

1、ESD保护器件的寄生电容必须足够低,以允许高速信号传输而不会降级。

2、ESD需放置在被保护的IC之前,但尽量与连接器/触点PCB侧尽量靠近;放置

2023-08-01 18:02:03

放在一边。 如果可能,将电源PCB抄板线从卡的中央引入,并远离容易直接遭受ESD影响的区域。 在引向机箱外的连接器(容易PCB抄板直接被ESD击中)下方的所有PCB层上,要放置宽的机箱地或者多边形

2018-09-11 16:12:00

的信号线,因为长的信号线可以接收ESD脉冲能量。尽量把每个信号层紧靠着相应的电源层或地线层。如果元器件比较密集,可以使用内层线。第四,如果PCB周围画出不加组焊层的走线,可以将走线连接至外壳,但不能构成

2017-02-22 17:45:11

L1和L4信号线,L2地线层,L3电源层。如果L4层上的元器件较少,是主布线层,那么将L2改为电源,L3为地,效果可能会更好些。 6层板:L2和L5为地线层和电源层,其它为信号层。

2019-05-21 10:19:01

4.4.3 实验设计9:通用的4层PCB 通过增加两个内部信号层,实验设计6的2层叠加现在将增加到4层。与以前一样,假设这些层主要由许多较薄的信号走线组成,而不是大面积连续铺铜。 模拟的内部

2023-04-21 15:04:26

PCB线路板叠层设计要注意哪些问题呢?

2021-03-29 08:12:19

产生的电磁干扰(EMI)电磁场效应。本文将提供可以优化ESD防护的PCB 设计准则。电路环路:电流通过感应进入到电路环路,这些环路是封闭的,并具有变化的磁通量。电流的幅度与环的面积 成正比。较大的环路包含

2012-02-03 14:09:10

PCB设计中叠层算阻抗时需注意哪些事项?

2019-05-16 11:06:01

在高速PCB设计流程里,叠层设计和阻抗计算是登顶的第一梯。阻抗计算方法很成熟,不同软件的计算差别不大,相对而言比较繁琐,阻抗计算和工艺制程之间的一些"权衡的艺术",主要是为了达到

2018-01-22 14:41:32

影响的区域。 6、 在引向机箱外的连接器(容易直接被ESD击中)下方的所有PCB层上,要放置宽的机箱地或者多边形填充地,并每隔大约13mm的距离用过孔将它们连接在一起。 7、 在卡的边缘上放置安装孔,安装

2018-11-22 16:09:28

是电路板设计的一个重要指标,特别是在高频电 路的PCB设计中,必须考虑导线的特性阻抗和器件或信号所要求的特性阻抗是否一致,是否匹配。这就涉及到两个概念:阻抗控制与阻抗匹配,本文重点讨论阻抗控制和叠层设计的问题。

2019-05-30 07:18:53

辐射最小化,还能提供ESD保护。 信号清晰度 在未来,电子设计的复杂性毫无疑问会持续增加,这会给PCB设计师带来一系列亟待解决的挑战。确保电路板叠层、阻抗、电流回路的正确配置,是设计稳定性的基础。

2018-09-19 15:41:05

优化ESD防护的PCB设计准则 PCB布线是ESD防护的一个关键要素,合理的PCB设计可以减少故障检查及返工所带来的不必要成本。在PCB设计中,由于采用了瞬态电压抑止器(TVS

2009-12-02 09:11:51

全球出现的能源短缺问题使各国***都开始大力推行节能新政。电子产品的能耗标准越来越严格,对于电源设计工程师,如何设计更高效率、更高性能的电源是一个永恒的挑战。本文从电源PCB的布局出发,介绍了优化

2018-09-14 16:22:45

完美的叠层图,板框图

2019-03-19 09:54:23

本帖最后由 yfsjdianzi 于 2014-5-11 14:23 编辑

叠层电感也就是非绕线式电感,是电感分类的其中一类。外形尺寸小,闭合电路,无交互干扰,适合于高密度安装,无方

2014-05-10 20:04:18

叠层电感在现实中应用也十分广泛,目前叠层电感类产品被广泛用于笔记本电脑数位电视,数位录放影机,列表机,硬式磁碟机,个人电脑和其安一般消费性及电脑主品上输入、输出线路之杂讯消除。

2019-10-17 09:00:27

叠层电池的升压电路

2019-11-07 03:31:57

在8层通孔板叠层设计中,顶层信号 L1 的参考平面为 L2,底层信号 L8 的参考平面为 L7。

建议层叠为TOP-Gnd-Signal-Power-Gnd-Signal-Gnd-Bottom,基铜

2023-12-25 13:46:25

在8层通孔板叠层设计中,顶层信号 L1 的参考平面为 L2,底层信号 L8 的参考平面为 L7。

建议层叠为TOP-Gnd-Signal-Power-Gnd-Signal-Gnd-Bottom,基铜

2023-12-25 13:48:49

的仿真结果果然有了明显的优化,从仿真验证上,已经能把信号质量变成PASS了!

Chris看看雷豹优化后的PCB文件,发现走线的拓扑长度都没有变化,只是从叠层上做了下文章,这也和Chris预想的方案

2023-06-02 15:32:02

)传输到 PCB 设计。在 PCB 布局或布线开始前,I/O 优化可使用 PADS 项目数据进行叠层规划以及优化初始分配。用户可将结果导出到 Layout,并在项目级别或企业库级别管理 FPGA 元件

2018-09-20 11:11:16

IEEE_802.11PHY与MAC层性能优化论文

2014-03-21 15:17:40

FR-4 材料以全数据速率接收清晰的数据眼图。特性使用低成本 PCB 材料实现高性能 JESD204B 串行链路了解有损通道的局限性并通过均衡技术突破限制使用基于公式的方法来优化 ADC16DX370 的均衡特性此参考设计已经过测试,并包含 EVM、配置软件和用户指南`

2015-05-11 10:40:44

allegro16.5多层PCB板的叠层设计时,内电层设计为正片或负片的选项不知道怎样处理,我原来用的是allegro15.7,allegro15.7设置内电层时,它有个选项,可选为正片或负片,但allegro16.5没看到这个选项,求教知道的人指导一下

2015-09-20 18:45:24

层的地参考层连接起来,如下图所示。

05

ESD优化建议

1、ESD保护器件的寄生电容必须足够低,以允许高速信号传输而不会降级。

2、ESD需放置在被保护的IC之前,但尽量与连接器/触点PCB侧尽量

2023-08-03 18:18:07

在设计多层PCB时,叠层是必须得考虑的问题,层分布好坏直接影响产品的性能。下面推荐几个使用最稳定的叠层结构:

2020-06-10 20:15:31

您还在为阻抗设计头疼吗?这里有齐全的阻抗参数及叠层结构。有它您无需再去仿真,我们已将其一一列出,如 90ohm线宽线距为7/6mil 或 5/4mil ,结合布线空间选择对应的线宽线距。

2020-06-10 20:54:11

基于优化多层印制板,改进信号完整性的设计,主要通过调整叠层设计中的各层导线宽度、基板厚度、填充层厚度和绝缘材料厚度,4个维度参数,从而改变信号传输路径特性阻抗的方法,有具体应用实例。

2021-04-06 11:15:43

多层板叠层设计规则,单层、双层PCB板的叠层,推荐设计方式,设计方案讲解。

2021-03-29 11:58:10

`完整的参考平面可以用来保证回路的连续性,宽的线宽可以降低信号的导体损耗,背钻工艺可以减小过孔的Stub,提高信号的完整性,但是这样往往会导致成本的增加。本文章将介绍两种六层板叠层结构。`

2021-03-30 10:42:55

常见的PCB叠层结构,四层板、六层板、八层板十层板叠层设计及注意事项。

2021-03-29 11:49:35

多层PCB通常用于高速、高性能的系统,其中一些层用于电源或地参考平面,这些平面通常是没有分割的实体平面。无论这些层做什么用途,电压为多少,它们将作为与之相邻的信号走线的电流返回路径。构造一个好的低

2021-08-04 10:18:25

在电路板设计上创建PCB叠层也会遇到类似情况:我们可能不了解最适宜的PCB材料,也不知道如何有效地构建叠层。在作出决定之前,清楚了解我们的需求才能对设计最为有利。优化设计意味着梳理可供考虑和选择

2021-08-04 10:13:17

手机PCB Layout层数选择与叠层设计方案剖析。回复帖子查看资料下载链接:[hide][/hide]

2021-08-04 10:10:24

本文主要介绍多层PCB设计叠层的基础知识,包括叠层结构的排布一般原则,常用的叠层结构,叠层结构的改善案例分析。回复帖子查看资料下载链接:[hide][/hide]

2021-08-04 10:06:58

抗ESD的PCB布局与布线设计和一般的PCB布局有所不同,有许多技巧,大家在日常的设计中也有所领悟,在这里我也为大家总结了一些抗ESD的PCB布局与布线设计技巧,希望能对大家有所帮助。 要确保

2016-10-02 12:47:01

就几乎不依赖于顶层的铜面积,比没有散热过孔的4层叠层低了大约5℃。 4.3.7 总结:影响单个器件热性能的因素 •对于安装在1层PCB上的器件,器件Tj在很大程度上依赖于铜的面积。 然而,“边际递减

2023-04-21 14:51:37

本帖最后由 张飞电子学院吕布 于 2021-4-12 16:36 编辑

一到八层电路板的叠层设计方式 电路板的叠层安排是对 PCB 的整个系统设计的基础。叠层设计如有缺陷,将最终影响到整机

2021-04-12 16:35:28

请问一下为什么我的叠层管理器打不开。。

2019-09-02 01:15:06

PCB设计中层叠结构的设计建议:1、PCB叠层方式推荐为Foil叠法2、尽可能减少PP片和CORE型号及种类在同一层叠中的使用(每层介质不超过3张PP叠层)3、两层之间PP介质厚度不要超过21MIL

2017-01-16 11:40:35

多层PCB如何定义叠层呢?

2023-04-11 14:53:59

在PCB设计 中,可以通过分层、恰当的布局布线和安装实现PCB的抗ESD设计。在设计过程中,通过预测可以将绝大多数设计修改仅限于增减元器件。通过调整PCB布局布线,能够很好地防范ESD。 来自人体

2017-04-14 10:50:10

影响的区域。 在引向机箱外的连接器(容易直接被ESD击中)下方的所有PCB层上,要放置宽的机箱地或者多边形填充地,并每隔大约13mm的距离用过孔将它们连接在一起。 在卡的边缘上放置安装孔,安装孔周围用无阻

2017-04-29 16:14:23

直接被ESD击中)下方的所有PCB层上,要放置宽的机箱地或者多边形填充地,并每隔大约13mm的距离用过孔将它们连接在一起。 在卡的边缘上放置安装孔,安装孔周围用无阻焊剂的顶层和底层焊盘连接到机箱地上

2018-11-27 10:10:19

,以便该环形地可以充当ESD的放电棒,在环形地(所有层)上的某个位置处至少放置一个0.5mm宽的间隙,这样可以避免形成一个大的环路。信号布线离环形地的距离不能小于0.5mm。?欢迎大家一起分享,信盈达专业嵌入式、单片机、PCB技术实训,学一技之长,成就美好人生。技术热线***,扣扣754634522

2013-09-01 11:56:25

的中央引入,并远离容易直接遭受ESD影响的区域。 在引向机箱外的连接器(容易直接被ESD击中)下方的所有PCB层上,要放置宽的机箱地或者多边形填充地,并每隔大约13mm的距离用过孔将它们连接

2014-12-22 11:16:56

搞定叠层,你的PCB设计也可以很高级

2020-12-28 06:44:43

射频板设计PCB叠层时,推荐使用四层板结构,层设置架构如下【Top layer】射频IC和元件、射频传输线、天线、去耦电容和其他信号线,【Layer 2】地平面【Layer 3】电源平面

2022-11-07 20:48:45

,走线距离参考层7mil,板材为FR4.图三PCB差分走线间距与叠层从上述设计我们可以看出,在扇出区域差分对间间距和差分对内的线间距相当,会使差分 对间的串扰增大。图四是上述设计的差分模式的近端串扰

2018-09-11 11:50:13

普通铁氧体电感、叠层扼流电感及叠层功率电感有何区别?

2011-10-16 20:20:01

本文从电源PCB的布局出发,介绍了优化SIMPLE SWITCHER电源模块性能的最佳PCB布局方法、实例及技术。

2021-04-25 06:38:31

贴片电感从制造工艺上可分为:绕线型、叠层型、编织型和薄膜片式电感器,常用的为绕线型电感和叠层型电感,绕线型电感是传统绕线电感器小型化的产物,而叠层型电感采用多层印刷技术和叠层生产工艺制作,体积比绕线

2020-06-02 09:33:23

在片式电容器里用得最多的就是片式叠层陶瓷介质电容器。片式叠层陶瓷电容器(MLCC),简称片式叠层电容器(或进一步简称为片式电容器),是由印好电极(内电极)的陶瓷介质膜片以错位的方式叠合起来,经过

2018-08-06 17:33:24

`叠层电感也就是非绕线式电感,叠层电感是电感按结构不同对电感进行分类的其中一类。特 性: 1.外形尺寸小。 2.闭合电路,无交互干扰,适合于高密度安装。 3.无方向性,规范化的自动贴片安装外形

2013-08-29 17:41:52

电路板的叠层设计是对PCB的整个系统设计的基础,叠层设计若有缺陷,将最终影响到整机的EMC性能。叠层设计是一个复杂的,严谨过程,当然,设计开发,没必要从零开始经过一系列的复杂计算和仿真,来确定设计方案是否合适,仅需要总结前人的经验,选择合适系统的叠层方案。

2021-11-12 07:59:58

画ddr的八层板子这样叠层可以吗?这两个哪个比较好?@chenzhouyu @郑振宇_Kivy @cesc

2019-05-29 03:20:49

过程中产生问题(当然,我们是PCB的第一个过孔付出成本)。因此,本实验设计的目的是研究不同的模式对设计的热性能的影响。 本节的实验设计将使用边长15mm的第1层铜面积,并将考虑使用表1中列出的特征的模式

2023-04-20 17:19:37

层间未设计参考地层),客户端未充分考虑相邻层走线存在的干扰,导致调试不通问题。 与客户沟通对叠层进行优化,将L45、L56、L67层结构进行了调整,介质层厚度分别由20.87mil、6mil

2019-05-29 08:11:41

设计PCB时如何很好的防范抗ESD?

2021-04-25 08:26:16

可能,将电源线从卡的中央引入,并远离容易直接遭受ESD影响的区域。 6、在引向机箱外的连接器(容易直接被ESD击中)下方的所有PCB层上,要放置宽的机箱地或者多边形填充地,并每隔大约13mm的距离用过

2012-12-19 17:02:52

RT,现有一个项目,需要布置八层板,两层信号,因整块板的平均功率达50W,需要布置两层电源,其它层全铺地,最佳的叠层顺序是怎么样较好。

2019-09-24 05:07:43

八层板常用的叠层方式有哪几种?

2021-04-25 07:16:59

贴片叠层电感和贴片功率电感的作用和应用有什么不同呢?

2015-09-15 16:27:53

的放置位置以及如何在这些层上分布不同的信号。这就是多层PCB层叠结构的选择问题。 层叠结构是影响PCB板EMC性能的一个重要因素,也是抑制电磁干扰的一个重要手段。本文介绍多层PCB板层叠结构的相关内容

2016-08-23 10:02:30

这个叠层图是什么意思呢

2015-06-11 09:23:35

在《PCB的筋骨皮》一文中,我们提出了当板厚在1.6mm及以上时,怎样避免使用假八层的叠层,而导致PCB成本增加的问题。感觉大家的回答很踊跃哈,看来这个问题还是比较典型的。本来想截取一些回答放在

2019-05-30 07:20:55

在《PCB的筋骨皮》一文中,我们提出了当板厚在1.6mm及以上时,怎样避免使用假八层的叠层,而导致PCB成本增加的问题。感觉大家的回答很踊跃哈,看来这个问题还是比较典型的。本来想截取一些回答放在

2022-03-07 16:04:23

在《PCB的筋骨皮》一文中,我们提出了当板厚在1.6mm及以上时,怎样避免使用假八层的叠层,而导致PCB成本增加的问题。感觉大家的回答很踊跃哈,看来这个问题还是比较典型的。本来想截取一些回答放在

2019-05-29 07:26:53

多层PCB通常用于高速、高性能的系统,其中一些层用于电源或地参考平面,这些平面通常是没有分割的实体平面。无论这些层做什么用途,电压为多少,它们将作为与之相邻的信号走线的电流返回路径。构造一个好

2018-11-27 15:14:59

高速PCB设计的叠层问题

2009-05-16 20:51:30

的相对位置。特性阻抗要求的差分对间的线宽/线距则取决于选择的PCB叠层结构。

由于最小线宽和最小线距是取决于PCB类型以及成本要求,受此限制,选择的PCB叠层结构必须能实现板上的所有阻抗需求,包括内层

2023-05-26 11:30:36

PCB布线是ESD防护的一个关键要素,合理的PCB设计可以减少故障检查及返工所带来的不必要成本。在PCB设计中,由于采用了瞬态电压抑止器(TVS)二极管来抑止因ESD放电产生的直接电荷注入,因此PCB设计中更重要的是克服放电电流产生的电磁干扰(EMI)电磁场效应。

2019-04-16 15:32:04 1249

1249 PCB设计中更重要的是克服放电电流产生的电磁干扰(EMI)电磁场效应。本文将提供可以优化ESD防护的PCB设计准则。

2020-12-07 10:17:40 2155

2155

德赢Vwin官网

App

德赢Vwin官网

App

评论