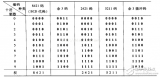

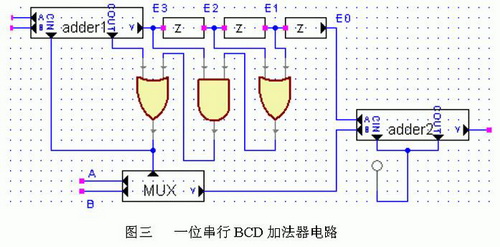

用四位全加器构成二一十进制加法器

德赢Vwin官网

App

德赢Vwin官网

App

硬声App

硬声App

完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

德赢Vwin官网 网>电子技术应用>电子技术>电路图>信号处理电子电路图>用四位全加器构成二一十进制加法器

相关推荐

431

431

1320

1320

1542

1542

2245

2245 1

1 20

20 4558

4558

29303

29303

27

27 1

1 3877

3877 23685

23685

6914

6914 4

4 18610

18610

79946

79946

30686

30686

134108

134108

27671

27671

10327

10327

16643

16643

157219

157219

143816

143816

22064

22064

54133

54133

33

33 37

37 47

47 17

17 62

62 12142

12142 10796

10796 2486

2486

26072

26072

3233

3233

评论