电子封装是芯片成为器件的重要步骤,涉及的材料种类繁多,大量材料呈现显著的温度相关、率相关的非线性力学行为。 相关工艺过程中外界载荷与器件的相互作用呈现典型的多尺度、多物理场特点,对电子封装的建模仿真方法也提出了相应的要求。 在可靠性验证方面,封装的失效主要包括热-力致耦合失效、电-热-力致耦合失效等。 随着新型封装材料、技术的涌现,电子封装可靠性的试验方法、基于建模仿真的协同设计方法均亟待新的突破与发展。

0 前言

电子封装是电子制造产业链中将芯片转换为能够可靠工作的器件的过程。 由于裸芯片无法长期耐受工作环境的载荷、缺乏必要的电信号连接,无法直接用于电子设备。 因此,虽然不同类型产品有所差别,但是电子封装的主要功能比较接近,主要包括四大功能:①机械支撑,将芯片及内部其他部件固定在指定位置; ②环境保护,保护芯片免受外界的水汽、腐蚀、灰尘、冲击等载荷影响; ③电信号互连,为内部组件提供电通路及供电; ④散热,将芯片工作时产生的热量及时导出。 按照工艺阶段的不同,电子封装通常可分为零级封装(芯片级互连)、一级封装(芯片级封装)、二级封装(模块级封装)和三级组装。

由于芯片及封装涉及大量不同类型材料,部分材料特性相差甚远,在封装工艺过程中,如果内部缺陷、残余应力、变形等问题控制不当,极易在封装过程中或者产品服役中引发可靠性问题。 随着封装密度不断提升、功能多样化,如 3D 封装、异质集成技术等,电子封装中多场多尺度耦合的可靠性问题更加明显。

1 电子封装可靠性研究共性技术

1.1 典型封装材料

目前制约微电子器件封装快速发展的一大因素就是缺乏相应的封装材料及完整的材料数据。 封装材料关系着电子微器件的强度和可靠性,材料的力学响应对于封装材料的选取和电子微器件的强度与可靠性设计非常关键。 因此急需针对典型封装材料的优缺点进行评价、开发加速评估方法,展望适合未来封装技术发展的先进封装材料。

封装材料一般包括:互连材料、基板材料和密封材料等。 其中互连材料与芯片直接接触,对芯片散热和可靠性最为关键,其需要耐受的温度和应力也更高。 本文以封装互连材料为例,介绍其研究进展与挑战。

由于 RoHS 和 WEEE 指令的限制,Sn-Pb 焊料无法继续应用于电子器件。 目前,无铅焊料主要以锡为基础,通过添加 Cu、Ag、Zn、Bi 等合金元素组成,主要包括 Sn-Cu 合金、Sn-Ag 合金、Sn-Ag-Cu合金、Sn-Zn 合金以及Sn-Bi合金等。

Sn-Cu 二元合金的共晶成分是 Sn-0.7Cu,共晶温度为 227℃,Sn-Cu 合金由于其优异的力学性能和低廉的价格,被认为是含铅焊料最有潜力的替代焊料。 Sn-Ag 二元合金的共晶成分是 Sn-3.5Ag,共晶温度是 221℃。 Sn-Ag 合金具有优异的力学性能和较好的可靠性,其缺点是润湿性比较差且表面张力比较高。 为克服这一缺点,人们在 Sn-Ag 合金中加入Cu 形成了具有优异润湿性和力学性能的 Sn-Ag-Cu 合金,它已成为近年来使用最广泛的焊料合金。

有研究通过添加一些稀土元素来进一步改善焊料的综合性能。 Sn 和 Zn 元素可以以固溶体的形式存在,Sn-Zn 系合金的研究也有明显的进展,但其润湿性、抗氧化性、力学性能和热学性能往往不相匹配。 Sn-Bi 系合金也是典型的低熔点合金,但硬度高、延伸率低,其导电性和导热性略低于前几种合金焊料。

当前,随着半导体技术的发展,以 SiC 为代表的宽禁带半导体材料由于其导热系数高、介电常数低、带隙高,可以实现器件在 200℃ 以上结温下稳定工作,是功率半导体器件的必然发展趋势。 当环境温度高于 200℃ 时,绝大多数焊点合金的抗疲劳性能和抗蠕变性能均无法满足宽禁带器件互连的可靠性要求。 虽然个别焊料合金可以勉强满足高温封装要求,但它们价格昂贵(如 Au/Sn,Au/Ge,Au/Si)或者加工性差(如 Bi/Ag,Zn/Al)。 因此,急需发展新型的耐高温连接材料和技术。

近年来,研究人员在耐高温互连材料方面做了大量努力。 提出了多种满足宽禁带电子器件高温封装要求的互连技术。 其中以瞬时液相扩散连接(Transient liquid phase, TLP)和低温烧结金属连接(Low temperature joining technique, LTJT)广受关注。

TLP 是将低熔点的中间层材料置于高熔点的母材中间,在适当的压力下加热到高于中间层材料熔点温度,熔化中间层材料并与母材反应生成高熔点的金属间化合物而实现低温固态连接。 TLP 连接的中间层材料必须具有较低的熔点,常用的低熔点元素有Sn和In,二者的熔点分别为 231℃和 156℃,能与这两种元素形成高熔点金属间化合物的元素有Ag、Au、Ni。 Cu 与 Sn 之间也可形成 Cu-Sn 高熔点化合物。

综上,TLP 连接可以实现低温连接和高温应用,是宽禁带半导体器件互连的可行技术。 但是这种方法也有明显缺点,如需要事先在连接件表面镀覆金属,增加了成本和工序; 连接时保温时间较长,而且连接完成后往往还需要进行退火处理。 虽然耐温能力比传统焊料合金有明显提高,但是脆性的金属间化合物高温可靠性仍存在隐患; 工艺控制方法略微复杂,需要避免反应不充分或者过反应。

因此,低温烧结金属连接技术受到更为广泛的关注,尤其是低温烧结纳米银连接技术,由于其高导热、低压/无压力烧结、低温烧结致密和低弹性模量等特性,已成为目前宽禁带半导体器件封装的首选互连材料。

近年来,针对纳米银焊膏的烧结工艺及其烧结银接头的性能及机械可靠性已经有了大量的研究成果。 例如,YANG 等发现,在相同的电流密度下,使用纳米银膏封装的发光二极管(Light emitting diode, LED)比用焊料和导电银胶封装的LED 光输出量大,表明其热导率优于焊料和导电银胶。 BAI 等利用低温烧结纳米银对单芯片封装和多芯片封装进行了深入研究。 结果表明,低温烧结连接法封装的功率半导体模块比传统焊料封装的功率半导体模块具有更好的电学、热学和力学性能。

虽然在大多数电子器件应用场合,烧结银的性能已被证明具有显著优势。 但是以往低温烧结需要辅助较高压力,工艺复杂,设备要求高。 因此不少学者通过改进材料制备方法和工艺,简化了互连工艺复杂度,降低低温烧结工艺和设备成本。 例如,YASUDA 等在 250℃-400℃ 和辅助压力小于 5MPa 的条件下,使用粒径为 5-20nm 的银作为连接材料,实现了芯片与基板的互连且剪切强度达到 20MPa 以上。 FU 等利用粒径为 2 µm 以下的银颗粒,在 250℃ 下首次无压烧结实现了大尺寸芯片(≥100 mm ^2^ )与基板的连接,其剪切强度达到 40 MPa,孔隙率为 25.6%,热导率为 263 W/m·K。

鉴于无压烧结银的致密度略低于大压力烧结银,低温无压烧结纳米银的性能和可靠性需要进一步验证。 这是因为在相同的烧结工艺下,连接面积越大,相应的孔隙率越高,连接强度越低; 提高升温速率可以促进焊膏的致密化过程,有利于晶粒的均匀化,但容易造成连接层产生缺陷,致使芯片受到热冲击,如果烧结温度太高或保温时间太长不利于银颗粒烧结致密化过程,反而会使晶粒粗化。

为解决上述问题,LU 等率先利用电流辅助烧结技术可以在 1 s 内实现电子器件与铜基板的快速致密化互连,烧结银层的导电率高达 3.7×10****^7 ^****S/m,比传统热压烧结银层高近两个数量级,接头剪切强度可达 40 MPa。 WANG 等将进一步发现在低温环境下包覆在纳米银焊膏表面有机物的热分解可以促使纳米银颗粒在 180℃ 下完成烧结。 随后,ALLEN 等利用该电流辅助烧结方法在电子印刷领域开展了应用研究。 该工艺过程可在 2 µs 内使热压烧结接头具有更高的抗机械疲劳性能。 CAO 等也发现在相同的加载水平下,电流辅助烧结银接头具有更好的循环剪切变形能力。

1.2 典型建模仿真方法

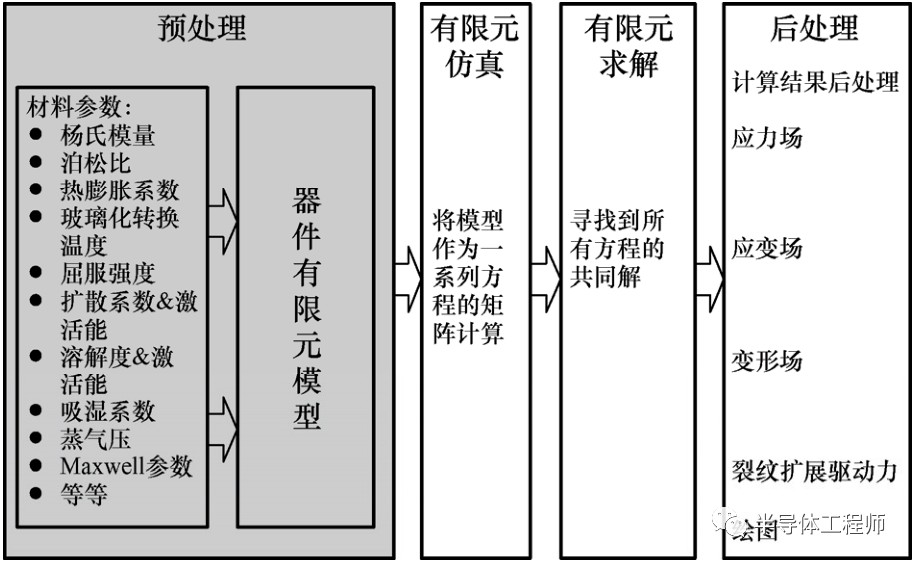

图 1 为在电子封装中有限元求解过程的基本流程图,通常包括预处理、建模、求解和后处理等步骤,其中材料参数和模型对于仿真结果的准确性有重要影响。

图 1 半导体封装有限元建模流程图

1.2.1 多尺度建模

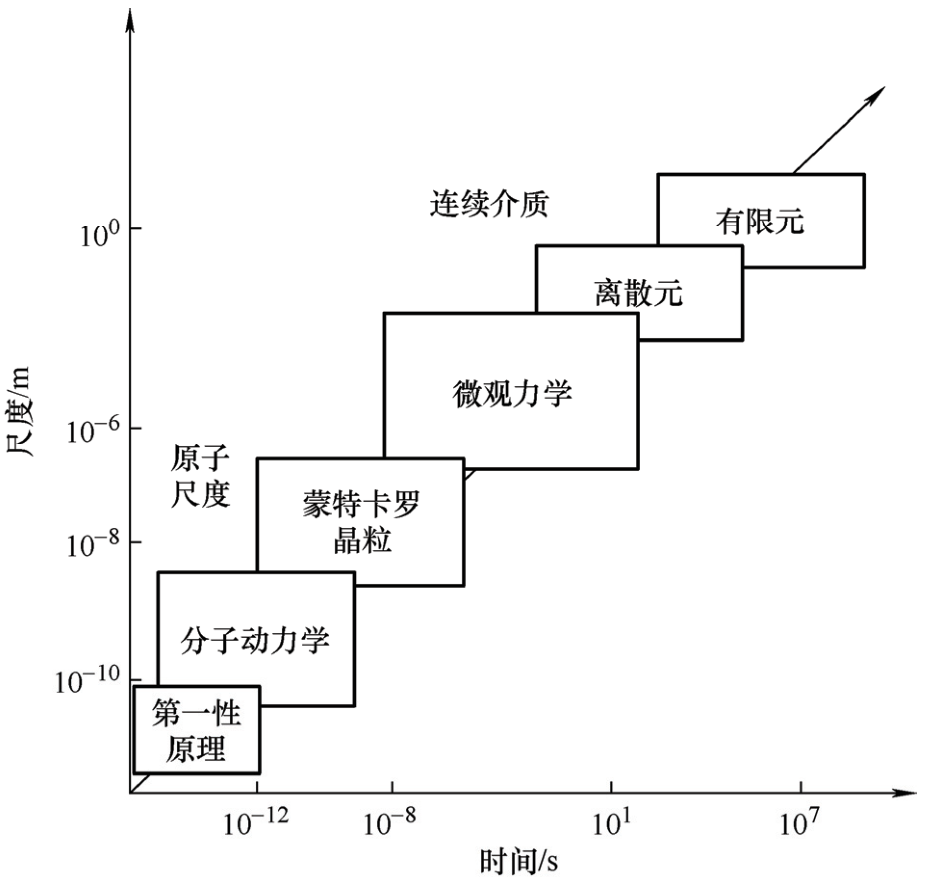

随着封装技术的不断发展,封装材料和结构研究的尺度和时间跨度可能超过 12 个数量级,并且每个级别都涉及不同的领域,如图 2 所示。 多尺度建模的最终目标是从第一性原理开始预测材料行为,将信息传递到分子尺度,最终传递到宏观尺度。 从“自下而上”的角度来看,多尺度方法应该考虑材料的内在属性。 目前的大部分工作都集中于纳米结构材料。

图 2 vwin 方法的尺度和时间跨度

对结构分析来说,基于连续介质的方法被用以描述或预测宏观材料的行为,例如传统力学和有限元方法。 分子动力学仿真主要关注具有热力学平衡的结构,这显然不像是数学连续体,而是一种离散的晶格结构。 因此,除非采取措施确保分析的等效性,否则对分子模型进行连续力学概念的直接应用是不恰当的。

1.2.2 多物理场的耦合分析

在电子封装流程中,多物理场效应广泛存在。 微机电系统(Microelectromechanical systems, MEMS)具有微米尺寸的组件,广泛应用于商业和工业系统中,如集成硅压力传感器、加速度计和运动检测器等已经在汽车和工业应用中使用了多年。 这些微小型系统(有些甚至比人类头发更细)从应力、温度、静电、压电和电磁效应中催生出它们的功能。 有两种数值技术可用于模拟涉及的多物理场:直接耦合和顺序耦合。

(1) 直接耦合分析。 直接耦合分析将所有物理场组合为一个矩阵中的有限元方程,并将矩阵作为一个整体求解。 直接耦合的一个示例是热效应和电效应的组合,以此研究电阻或介电材料的电磁能所产生的焦耳热大小。 在某些换能器中,电学和力学的直接耦合可以确定施加电压引起的变形量,反之亦然。 在这些类型的分析案例中,我们就可以在单个解决方案中考虑所有物理场。

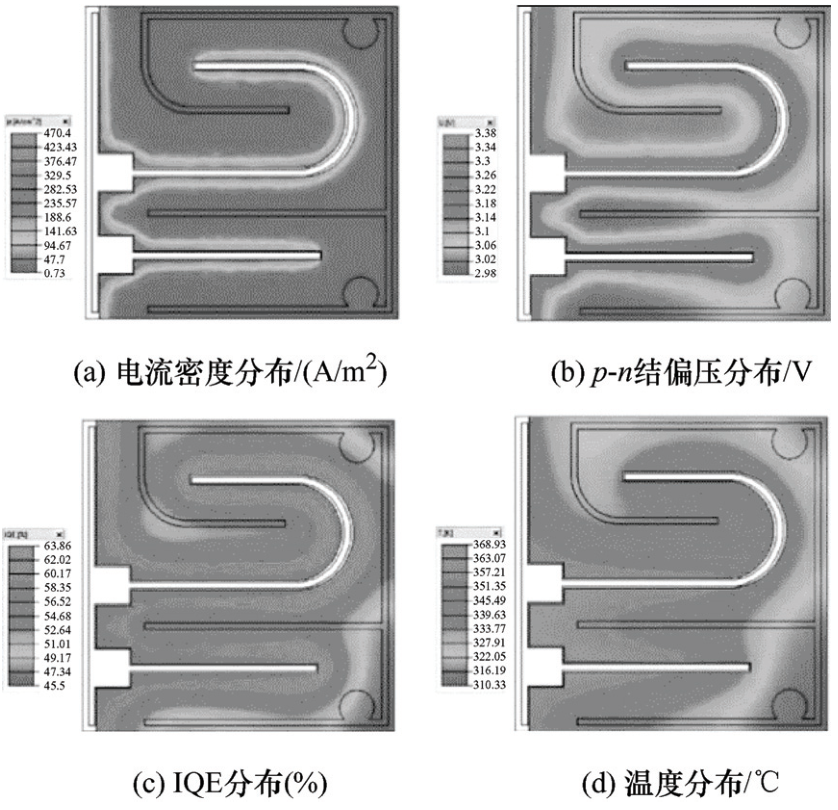

以 LED 的仿真为例。 LED 异质结构被认为是一组平面半导体层和电极。 一维模型可用于模拟 LED 能带图,它可以视作异质结构内的偏置电压、电子和空穴传输的函数,还可以模拟提供光发射的载流子复合过程。 因此,我们可以获得内部量子效率(Internal Quantum Efficiency, IQE)、电流密度和发射光谱与 p-n 结偏压和温度之间的关系,如图 3 所示。

图 3 LED 芯片的仿真结果,所有结果都显示在有源层上

(2) 顺序耦合。 在顺序耦合中,一个场的方程被部分求解,并且结果作为载荷(一个物理场与另一个物理场相互作用的结果)传递到下一个物理场以驱动该场的求解。 然后分析软件将此迭代传递到下一个物理场,依此类推,直到最后一个场。 在这之后顺序迭代过程从头开始直到找到最终解。

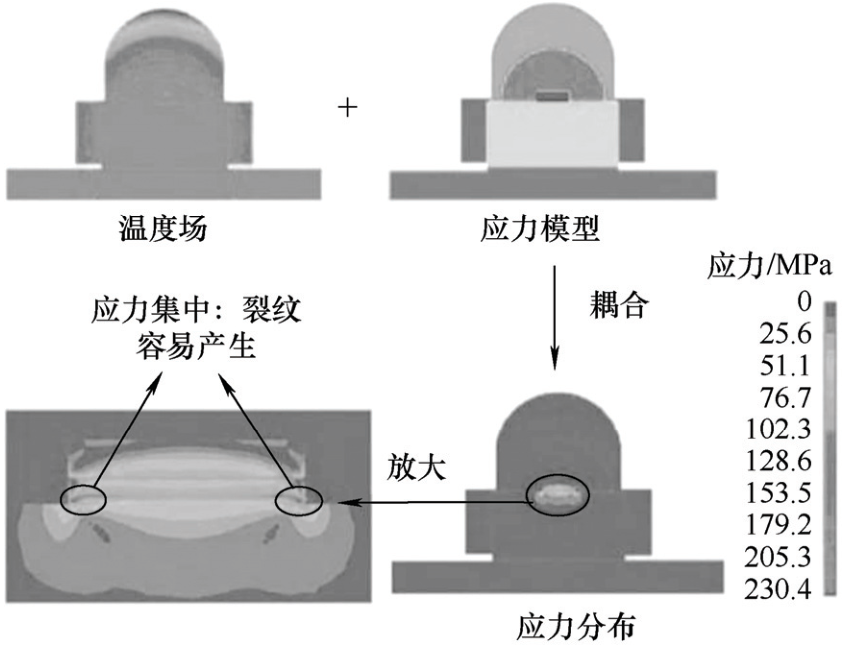

例如,在各种制造工艺、加速测试、不当的处理和应用过程中,LED器件和模块中经常产生空隙、裂缝和分层等缺陷。 缺陷主要在制造早期形成,但是在后续的温度、湿度、应力等不均匀载荷下逐步扩展最终失效。 如图 4 所示,通过非线性有限元法(Finite element method,FEM)对各种情况下的缺陷进行建模,以研究界面、界面初始缺陷和热接触电阻、非线性应力及光学界面之间的联系,从而分析它们对 LED 热学及光学性能的影响。 在顺序耦合场分析中,我们先计算初始温度场,再将其传递给结构分析。

图 4 大功率 LED 的热应力分析

通常,对于多物理场分析,物理场之间的数据交换需要仔细协调,并且必须将各种场、载荷以及边界条件的不同网格要求相关联。 为了使所有这些功能正常运行,需要在各个场之间进行复杂的反馈循环,以便耦合分析能收敛到准确解。 一些研究表明,在产品生命周期的不同阶段,解决这类问题的时间和成本相差近 10 倍。 考虑更多的物理效应可以产生更准确的分析、更少的物理原型、更短的产品开发周期、更低的开发成本以及更快的上市时间。

有些分析可能具有单向耦合。 在热应力问题中,温度场在结构场中产生热应变,但结构应变一般不影响温度分布。 因此,不需要在两个场的解中迭代。 更多复杂情况涉及双向耦合。 例如,在 MEMS 的压电分析中,处理结构场和电场之间的相互作用。 在流体-结构相互作用问题中流体压力导致结构变形,反过来结构导致流体解发生变化。 这些问题需要两个物理领域之间的迭代才能收敛。 场之间的耦合可以通过直接或间接实现耦合。 跨场的耦合可能很复杂,因为不同场在求解器中可能涉及不同类型的分析。

电子制造中常用其他建模技术包括如下。

(1)子模型技术。 利用子建模技术,基于从一个初始的、相对粗糙的、全局的模型,研究模型中具有精细网格的局部部分。 当需要获得一个准确的局部解,并且细化的局部区域建模对整体解的影响可以忽略不计时,子模型技术是十分有用的,可以结合使用线性和非线性过程。 子模型作为与全局分析独立的分析运行。

(2)自适应网格技术。 自适应网格划分是一种工具,它可以在整个分析时保持高质量的网格划分,即使出现大变形或材料损耗,自适应网格不会改变拓扑(元素和连接)。 自适应网格重构通常用于精度控制,然而它也可用于某些情况下的扭曲控制。

(3)单元移除和重新激活。 在一般分析步骤中,从模型中删除指定的元素。 在移走之前,要移除的区域上的力/变量被存储作用于该区域边界的节点上。 在移除步中,这些力被降至零; 因此,移除部分对于剩余部分是完全没有影响的。 这些力被逐渐降低,以确保去除元素对模型平滑的影响。

1.3 失效类型及机理分析

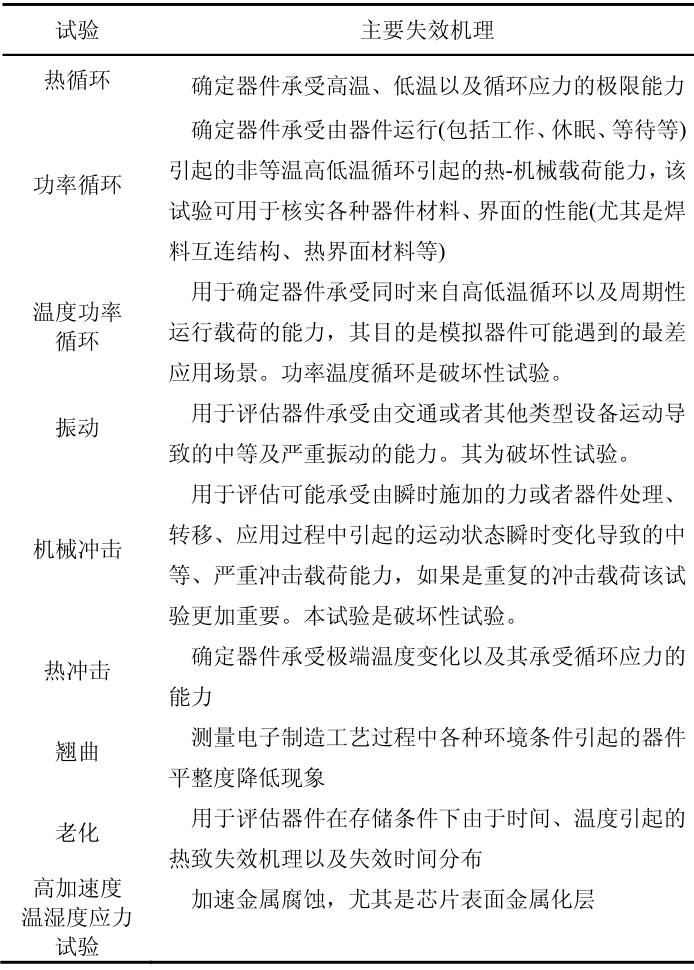

经过封装后的电子产品需要经过严格的可靠性试验,才能最终筛选出合格产品供应给产业链下游。 相关的可靠性试验标准较多,通常来说,可供参考的主要标准有国军标(GJB 548、GJB 150)、国标(GB/T 2423)、美军标(MIL-STD-202、MIL-STD-750、MIL-STD-883)、JEDEC 标准(Joint Electron Device Engineering Council,电子器件工程联合会)中的 JESD22 系列等。 常见的可靠性试验见表 1。

表 1 常见的可靠性试验

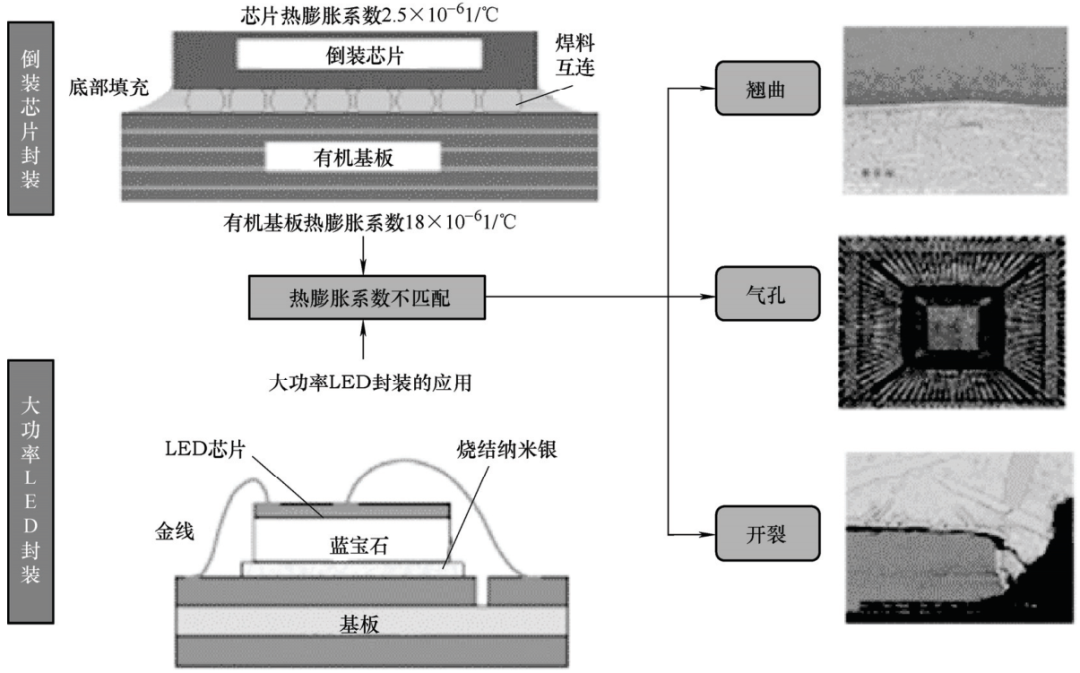

总体来说,在可靠性试验和实际应用中,封装互连材料的失效主要为电-热-力致耦合失效。 其中电对互连可靠性的影响主要表现为两方面:电流密度超过阈值导致电迁移和电致发热引起的温度变化(即功率循环)。 电迁移的主要原因是电流超过一定阈值后,电子风引起互连材料内部的原子定向迁移,从而导致局部电流进一步集中,从而形成正反馈,并最终导致互连结构的孔洞和断路。 另一方面,随着电子制造技术的进步,芯片互连材料越来越广泛地应用于动态服役环境(即应力和应变的分布随着时间而变化的环境)中。 而功率耗散和环境温度的周期性变化使得电子封装及其组件在封装工艺或者服役过程中不断经历温度循环的作用。 由于芯片、基板以及互连材料的热膨胀系数(Coefficient of thermal expansion, CTE)不匹配,使得在互连界面处应力不为零,会导致焊层产生塑性应变的积累,使得互连焊层中的损伤不断累积,发生翘曲、气孔、裂纹,导致最终失效,如图 5 所示,我们称之为低周棘轮疲劳失效。

图 5 器件失效机理

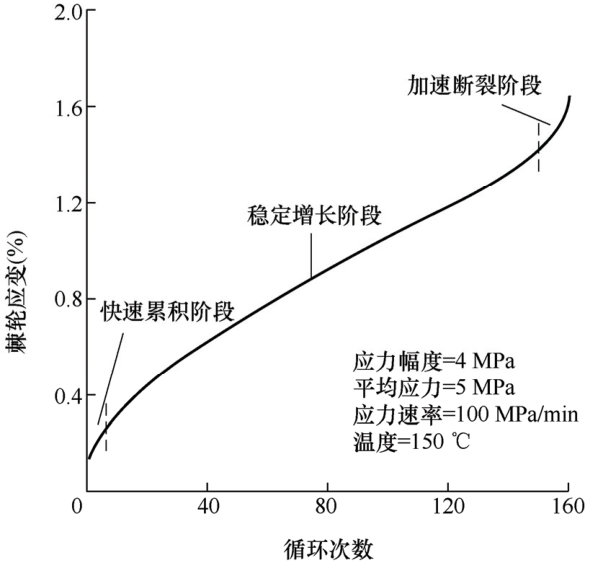

WANG 等对低温烧结纳米银焊膏薄膜试样的单轴棘轮失效行为进行研究。 从图 6 可以看出,材料的低周棘轮疲劳塑性应变演化可分为三个阶段:初始快速累积、稳态增长和加速断裂。 第一阶段较为短暂,在此阶段棘轮应变迅速累积。 第二阶段占试件循环寿命的大部分,此阶段棘轮应变以一个几乎恒定的速率累积,棘轮应变稳定增长; 进入加速断裂阶段后,棘轮应变率和棘轮应变均表现出加速增长的趋势,试样在很少的循环次数内就因过大的棘轮应变而导致最终破坏,此阶段往往很短暂。 由于第二阶段占试件循环寿命的大部分,因此应重点关注棘轮失效行为的第二阶段。 第二阶段的棘轮应变率也是区分棘轮失效行为和疲劳失效行为的一个重要参数。

图 6 典型的低温烧结纳米银焊膏膜的棘轮演化曲线

对于传统的锡铅焊料,刘胜率领的课题组在 20 世纪 90 年代前后做了大量的系统性的研究工作。 CHEN 等对 63Sn37Pb 也进行了相关研究,在室温下对 63Sn37Pb 进行了系列棘轮变形试验,得到63Sn37Pb 在不同保持时间、平均应力、应力幅值和加载历史下的棘轮和疲劳变形行为,还采用 Anand 模型预测 63Sn37Pb 的棘轮和疲劳变形行为。 随后对用于替代锡铅焊料的无铅焊料和导电胶也不可避免的需要研究其棘轮和疲劳行为。 例如,AMALU等[55]研究了倒装芯片封装中无铅焊料连接半导体器件时,其高温可靠性及黏塑性行为。

针对有机胶复合黏连材料,MA 等采用动态热力分析仪 (Dynamic thermomechanical analysis, DMA)研究了高温下各向异性导电胶(Anisotropic conductive film, ACF)在应力控制下的单轴棘轮行为,讨论了平均应力、应力幅值、环境温度和加载历史对其单轴棘轮行为的影响, 发现其杨氏模量随温度升高而降低,棘轮应变随平均应力、应力幅值和温度的升高而增大,并且加载历史也对棘轮过程有重要的影响; TAN 等研究了采用 ACF 封装连接器件在受温度和湿度影响时的复杂力学行为,如剪切和循环疲劳。 研究发现器件互连在断裂前的最大剪切力达到 465.0 N,循环疲劳极限强度为 143.5 N。

虽然纳米银焊膏作为一种性能优异的新型无铅互连材料,已受到广泛关注。 在被广泛应用半导体器件封装之前,研究其棘轮失效行为和疲劳失效行为是不可或缺的。 这对指导低温烧结银作为芯片互连材料在高温应用中意义重大。

目前,针对电子器件的高温封装应用,芯片互连材料除物理性能,如 CTE、杨氏模量等之外、疲劳、蠕变特性及其与温度的关系则是更关键因素。 因此,部分学者率先研究了纳米银焊膏材料的机械可靠性。 例如,CHEN 等研究了纳米银焊膏烧结银膜在温度区间为−60℃到 300℃的拉伸和棘轮特性,并且讨论了在 150℃下加载速率、应力幅值和平均应力对烧结银膜的棘轮特性的影响。 WANG 等讨论了棘轮—疲劳的交互影响。

部分学者还针对低温烧结纳米银材料作为封装互连时的可靠性进行了研究。 例如,WANG 等研究了 1.1×1.1 mm****^2^**** 芯片连接的低温烧结纳米银焊膏的可靠性。 他们通过对低温烧结银封装互连器件开展−40~150℃的温度循环试验,发现在经历 900 周期温度循环老化后,烧结纳米银互连的微观结构未出现明显变化,但其芯片连接强度会出现小幅下降。 李欣设计了纳米银焊膏搭接剪切试样,并对接头在室温和高温下的力学性能进行了全面的试验和理论研究。 采用了应力或应变控制方式,对搭接接头进行了等温循环剪切试验,考察了平均应力、应力幅值以及环境温度对接头可靠性的影响。 齐昆等则结合 LED 应用需求,研究了烧结纳米银互连 1.1×1.1 mm****^2^**** LED 芯片的循环剪切疲劳行为,获得了其疲劳寿命曲线族。

随着应用场景的不断拓展,烧结纳米银被逐渐用于封装更大面积电子芯片,因此,研究人员探索了连接面积对封装连接可靠性的影响,发现无压烧结过程中,相同烧结工艺下连接面积越大,相应的烧结孔隙率越高,连接强度也随之降低,无压烧结工艺应被局限于连接面积小于 10 ×10 mm****^2^**** 的应用。 为克服无压烧结纳米银工艺方法的这一局限性,随后曹云娇等提出了烧结时间短、效率高的电流辅助烧结工艺,实现了纳米银焊膏的快速烧结,并且研究了相应的电流烧结纳米银互连焊层的力学可靠性。 通过循环剪切试验发现,平均应力和应力幅值对电流烧结纳米银互连焊层的棘轮行为影响明显,电流烧结纳米银互连焊层的棘轮变形水平随平均应力和应力幅值的增加而提高,寿命相应降低。 为了更好地预测电流烧结纳米银的优异抗疲劳可靠性,CHEN 等基于 Ohno-Wang 和 Armstrong-Fedrick (OW-AF) 非线性运动硬化准则的粘塑性模型和 Anand 模型嵌入 ABAQUS 商用有限元软件中来预测电流烧结纳米银互连焊层的棘轮行为,证明了 OW-AF 模型的预测结果的准确性优于Anand 模型。 该预测方法可用于更好的指导电子封装针对电-热-机械可靠性设计与增强。

2 典型电子封装领域可靠性研究

2.1 LED 封装可靠性研究

LED 封装可靠性是典型的光、热、力耦合问题,因此其评价标准围绕光学性能、热学性能和力学性能等方向。 在 LED 性能及可靠性中涉及各种封装材料和工艺主要包括:光转换材料、封装胶、固晶材料、封装基板。

(1) 光转换材料。 在大功率 LED 封装中,荧光粉材料是最常用的光转换材料。 其按材料分可分为稀土石榴石系、硅酸盐系、含氮化合物系和硫化物系四大系列。 其中铅酸盐的钇铝石榴石(Y3Al5O12)是目前使用最广泛的荧光粉,俗称 YAG 荧光粉。 该荧光粉的颗粒直径通常在 5~35 μm,具有亮度高、发射峰宽、成本低的优点,但激发波段窄,光谱中缺乏红光的成分,显色指数不高。 国外研究学者研究了荧光粉颗粒直径对 LED 出光的影响,通过试验证实,当粒径大约为 20 μm 时,LED 的光通量最大。

通常荧光粉和封装胶混合后涂覆,封装胶导热性能较差,荧光粉光转换过程中产热无法有效散出,导致硅胶在高温时性能变化,甚至“碳化”。 荧光粉温度过高将导致光学和热学性能的变差,也会使 LED 可靠性变差,甚至高温时会不发光,产生“热淬灭”现象。 LED 封装中主要应用的涂覆方法有:点胶涂覆、保形涂覆和远离涂覆。 点胶自由涂覆由于工艺简单、成本低,是 LED 封装中最常用的荧光粉涂覆方法,被广泛使用。 其直接将荧光粉胶涂覆在芯片表面,通过其自由流动成型而得到荧光粉层。 这种方法得到的荧光粉层高度远小于宽度,从而引起封装 LED 中间区域色温偏高而侧边区域偏黄,即产生“黄圈”,空间颜色均匀性差。

在芯片周围均匀涂覆荧光粉薄层即为保形涂覆,具有优良的空间颜色均匀性和光效。 目前保形涂覆工艺研究很多,如电泳法、溶液蒸发法、晶圆级旋涂法、沉降法和粉浆法、喷涂法等。 但保形涂覆工艺复杂、成本高,荧光粉层的后向散射严重,芯片和支架对光能吸收严重,降低了封装效率,同时芯片工作过程发热会引起的荧光粉温度升高,荧光粉效率随着温度的升高呈指数下降的趋势并且过高的荧光粉层温度引起明显的光学性能下降。

远离涂覆是将荧光粉层与芯片相隔离,芯片与荧光粉层并不直接接触。 然而,远离涂覆往往需要采用特殊结构的 LED 封装支架,降低后续光学设计自由度。 美国研究学者研究发现,采用远离涂覆,显著减小了后向散射,可将光效提高 7%。 华中科技大学罗小兵课题组设计了基于点涂法的半球薄层荧光粉远离涂覆方法,实现 LED 封装高空间颜色均匀性。

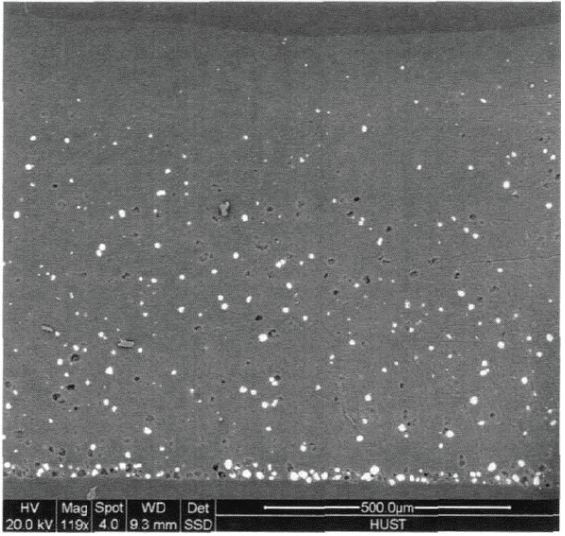

另外,在荧光粉胶中,荧光粉的密度远远大于硅胶密度,导致荧光粉在硅胶中会向下沉淀,分布不均匀,进而产生色温升高、一致性变差等问题。 美国专家对其色温漂移问题进行研究,证明荧光粉沉降会导致荧光粉层上下浓度变化,影响色温和光通量等光学性能。 在沉降过程中,上部的浓度变化要明显大于中间部。 芯片结构不同,荧光粉沉淀对光学性能的影响也不同。 华中科技大学罗小兵课题组通过试验观察证实了荧光粉沉淀,如图 7 所示,硅胶固化后大颗粒基本停留在底层。

图 7 荧光粉颗粒沉淀实物截面图

近十几年,量子点(Quantumdot,QD)材料,一种纳米尺寸半导体材料,受到越来越多的企业和科研院所重视,得到了广泛研究。 量子点是一种半导体纳米颗粒,具有很强的量子限阈效果,使得连续的能带变为分立能级,进而具有荧光效果。 相比于荧光粉,量子点的发光波长是可以随着粒径改变的,量子效率比较高。 因为是纳米颗粒,所以光散射极低,发光半峰宽很窄,色彩饱和度很高。

由于量子点是纳米级尺寸,纳米颗粒较高的表面能和颗粒之间的库仑力或范德华力使得量子点容易发生团聚。 此外,量子点表面配体常常与硅胶或环氧树脂中基团不兼容,会导致非辐射能量转移增大,引起量子点发光效率降低,光转换效率下降和封装剂难固化等不良问题。 在国内外的研究中,针对量子点团聚和与硅胶/环氧树脂的不兼容问题,多数采用的是将量子点和与其兼容的聚合物混合制成薄膜,并通过远离封装的形式制备,量子点发光二极管(Quantum dot light emitting diode,QLED)。

另外,量子点在光吸收和光转换方面具有一定阈值,当照射光强度或 LED 工作电流较大时,量子点发光性能往往呈现出“饱和效应”,具体表现为光转换效率阵低,光通量下降,色温升高和色坐标发生变化等。 随着封装密度的増加,工作功率的增加,饱和效应将更大的影响量子点在 LED 封装的发展和应用。

(2) 封装胶。 在 LED 封装过程中,通常采用环氧树脂或硅胶作为封装胶。 但由于环氧树脂容易出现老化变黄,严重影响出光效率,而硅胶具有更好的光-热稳定性,透光率也很高,所以在封装过程中常用硅胶作为封装胶体。 硅胶对不同颜色的光透光率通常能达到 97%以上。 提高 LED 封装胶折射率可有效减少芯片和封装材料界面上的全反射,因此高折射率、高透光率的封装材料对于提高取光效率也很重要。 目前主要产品来自美国道康宁公司,其推出的高折射率硅胶比传统的环氧树脂材料具有更好的光-热稳定性,透光率也很高,因而能显著改善 LED 的光学性能。

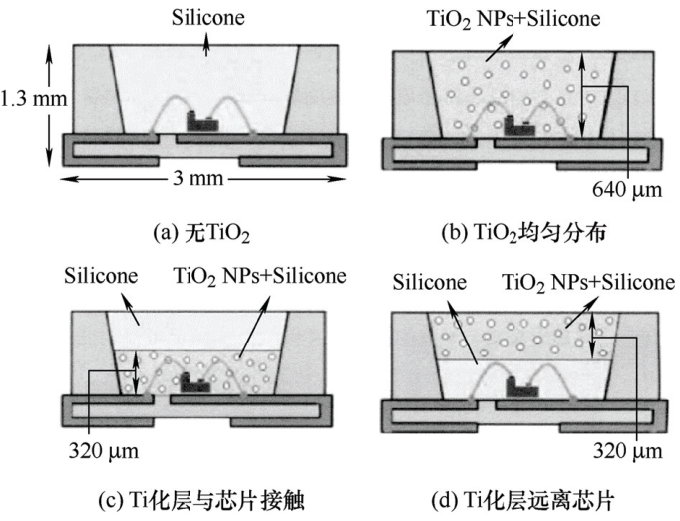

国内外学者通过开发或者改良工艺,也实现了硅胶质量的提升。 在封装胶中掺杂高折射率的散射粒子,可以提升封装胶的折射率,减少界面全反射,从而提升取光效率。 掺杂的粒子包括纳米TiO2粒子、ZnO粒子。 WANG 等将二氧化钛纳米颗粒掺杂入硅胶中,如图 8 所示。 结果表明将蓝光 LED 芯片上硅胶分为两层,接触芯片的一层掺杂二氧化钛颗粒,上层为纯硅胶,在 20 mA 和 80 mA 工作电流时,可以将光通量分别提升 3%和 5%,在老化试验中,发现光通量衰减情况得到一定程度抑制。

图 8 纳米 Ti 化掺杂硅胶的封装结构

(3) 固晶材料。 良好的散热对于大功率 LED 封装至关重要,是保障 LED 能够维持高光学性能的前提条件,是实现 LED 封装高可靠性的重要内容。 解决 LED 封装散热的最主要的方法是利用高导热的界面材料和基板材料降低芯片到外部环境的热阻,将芯片的热量快速传导到外部的散热器中。 LED 芯片产生的绝大部分热量是通过固晶层向下传导,因此固晶层不仅起到固定 LED 芯片的作用,而且是热量传递的必经路径,是散热关键,因而需要降低固晶层热阻。 目前采用的主流方法为采用高导热率的固晶材料。

由于成本较低、工艺温度较低,绝缘胶为早期应用产品; 随着功率的增大,由于绝缘胶热导率低,己经很少使用。 目前主流的固晶材料是导电银胶和共晶焊料。 导电银胶主要成份为银粉和树脂,具有一定的导电性,热导率大于 2 W/m·K,但含有一定的有毒物质,比如铅。 LED 封装功率越来越大,固晶材料需要更高的热导率,因此人们制造了金锡、锡银铜等共晶焊料,将热导率提升到 60 W/m·K 以上,而且共晶焊料已经成为目前市场上大功率 LED 主流固晶材料。 为了使得 LED 寿命延长,应用更加广泛,大量学者将研究热点集中于提升材料热导率,主要为掺杂高热导率材料,如掺杂金剛石、碳纳米管、纳米银等。 国外学者将银胶、锡银铜焊料及加入碳纳米管的焊料分别进行研究试验,结果证实具有碳纳米管的焊料热导率更高,更能减小固晶层界面热阻。 陈明祥老师课题组通过研究发现,当固晶材料热导率提升时,固晶层界面热阻降低,使得封装总热阻降低,可以增加 LED 的光输出。

(4) 封装基板。 芯片产生的热量主要有三个导热路径,一是通过封装胶向环境散热,二是通过引线和引脚传热,三是通过固晶层和封装基板向下传热。 其中绝大部分热量通过固晶层和封装基板传导。 封装基板的主要性能围绕可靠性和散热性,就需要考虑热力学性能,因此要有高热导率和适当的热膨胀系数。

金属芯印刷电路板(Metal core PCB, MCPCB)于20 世纪 60 年代在美国研发制造,其中金属基板具有很好的散热性能,但往往热膨胀系数不满足匹配性要求。 普通的 MCPCB 由于中间的绝缘层的热导率很低,只有 2~10 W/m·K,因此,尽管基板中金属的热导率很高,但整体热阻仍高达 50 K/W。 中国台湾钻石科技则采用类钻碳涂层取代 MCPCB 中的有机绝缘层,大幅提高了热导率和耐热性。 韩国研究学者将铝基板进行氧化试验,使得一面产生了氧化铝(Al2或3),从而使基板热阻得到了有效降低。 陶瓷材料由于具有良好的绝缘性和热导率,在制造封装基板方面已经有了广泛应用,其热膨胀系数匹配性能也较好。 主要有低温共烧陶瓷(Low temperature co-fired ceramic,LTCC)、覆铜陶瓷基板(Direct bonding copper, DBC)、直接镀铜基板(Direct plate copper, DPC)等种类。 韩国学者通过在基板上制备银过孔,增强了基板热导率,同时有效减小了热阻。 LTCC 基板在 21 世纪初由美国专家制造应用,由于结构简单,热界面少,大大提高了散热性能。 美国 LORD 公司开发的 Anotherm 阳极氧化铝基板己成功应用于大功率LED 封装。

铝基板与 Al2或3 陶瓷基板、AlN 陶瓷基板最大区别在于铝基板中有一层热导率低的绝缘层,严重影响了铝基板的整体导热性能。S.H.Shin 金属铝基板有选择性地进行氧化,并在基板上面封装微米级的功率型单片微波集成电路芯片(Monolithic microwave integrated circuit, MMIC),不仅具有良好的导热性能,而且还降低了封装成本,简化了基板制造工艺。金属基复合材料 (Metal matrix composite, MMC)基板具有更好的热膨胀系数匹配性能。国外学者通过试验制造了在 LED 封装中可实用的 Al-SiC 复合基板,热导率得到提升的同时,热膨胀系数也可以调节。Al-SiC 热膨胀系数与芯片相近,强度和硬度都超过了铜和铝,但离大规模的产业化应用仍有一段距离。

硅材料热导率更高,力学性能更好,中国台湾的 LED 产品中己经将 DPC 工艺技术应用到了硅基板制备中。香港科技大学的研究学者通过刻蚀出硅通孔,提升了硅基板的散热性能,同时与荧光粉涂覆工艺相结合,使得 LED 热性能得到提升。

2.2 功率电子封装可靠性研究

功率模块用于电力控制,对高效的能量转换起着关键作用。近年来,利用宽带隙半导体(如 SiC 和 GaN)的功率电子模块得到了关注与发展,其工作温度预计在 200℃以上,功率模块封装在 200℃以上的高温热—机械疲劳老化挑战极其严峻。因此,研究高可靠性、长寿命的功率模块非常必要。

对功率器件的研究从 20 世纪 90 年代就开始了,功率模块结构完整性研究主要集中在功率器件的状态监测和剩余寿命估计。目前基于计算机辅助工程 (Computer aided engineering, CAE)的应力分析、断裂力学和材料强度分析已被广泛应用于确保功率电子器件封装结构完整性。

例如,以往功率器件封装的结构完整性的关键是芯片和键合线之间的连接(线键合位置)以及芯片和铜基板之间通过封装互连材料实现连接。在功率模块工作时,这些封装互连受到周期性的温度变化作用,由于功率模块的封装材料间 CTE 不匹配,从而导致其承受显著的循环热应力,极易导致热-机械疲劳现象。热-机械疲劳可能导致模块封装引线断裂和封装互连的裂纹产生与扩展。亟须发展功率电子模块中键合引线和连接层的热-机械疲劳寿命的估算方法,实现功率电子器件的封装结构完整性设计。这就要求我们掌握失效原因,并开发准确的寿命预测方法。

近些年来,研究人员提出了一些基于温度范围的引线寿命预测模型。它们包含引线脱落寿命公式和连接层开裂寿命预测模型。但是该模型为了拟合试验数据,需要确定与物理量有关的常数,而鉴于功率模块复杂的工况,使得这种方法的模型使用仅限于某一功率模块,不同的模块和工况需要进行新的参数拟合和修正。随后有学者就提出了基于非弹性应变范围Δεin 的引线脱落和连接层裂纹的寿命预测模型,以及非线性断裂力学参数 J 型积分范围 ΔJ 和非线性断裂力学参数 T型积分范围 ΔT 的寿命预测模型。由于它们均是直接影响热疲劳的物理参量,因此均比基于温度范围 ΔT 的寿命预测模型更简单。

除寿命预测理论模型外,针对功率器件的封装寿命预测还需要注意:①由于引线键合的焊点尺寸非常小,针对引线键合的寿命预测中,其裂纹扩展寿命常常忽略不计,但对于功率模块的连接层十分必要考虑裂纹扩展的寿命。可以考虑采用基于 Paris 定律给出的疲劳裂纹扩展速率来准确预测连接层的开裂行为;②以 ANSYS 等为代表的商用有限元软件目前不提供标准的基于连续损伤力学和共聚力模型的寿命预测方法函数调用,因此,急切需要在商业有限元软件中增添这些方法函数或开发新的专用有限元软件;③机械载荷试验应更多的用于获得 Coffin-Manson 定律型的疲劳特性以及 Paris 定律型的疲劳裂纹扩展特性,而不是耗时且不精确的热循环试验和功率循环试验。这是因为在功率循环试验中,由于从 VCE 获得的温度是半导体芯片的平均温度,而不是失效位置的局部温度,因此使用基于通过集电极-发射极电压 VCE 评估的温度范围 ΔT 的故障模型不适合评估局部故障的寿命,而其局部温度才是影响功率电子模块中键合引线脱落失效的关键因素。

2.3 微电子芯片封装可靠性研究

微电子封装产品在生产制造、应用使用和存贮运输过程中所承受的外在环境因素(如湿气、温度、振动、粉尘等)都会对影响到封装产品的可靠性,使其遭受各种物理或化学的失效形式,主要失效机理包括:翘曲变形、剥离分层、疲劳断裂、磨损腐蚀等。其中封装中的湿气问题一直是困扰电子封装行业的难题之一,刘胜团队最早开始针对封装中的界面问题开展研究,LIU 等在 1995 年即开始界面湿气问题的测试和建模。

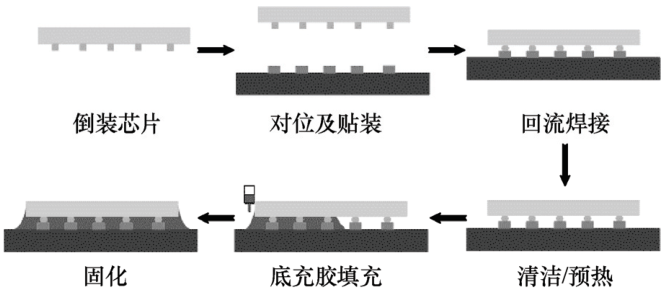

(1) 倒装芯片封装可靠性。 倒装芯片(Flip-chip, FC)封装技术最早是由 IBM 公司引入,具体的工艺步骤如图 9 所示。当时,主要的设计目是为了克服手工引线键合成本高、可靠性差和生产效率低的缺点。目前,在计算机、通信等领域,倒装芯片封装技术已经获得了相当程度的应用,并且呈高速增长的趋势。

图 9 倒装芯片封装工艺步骤

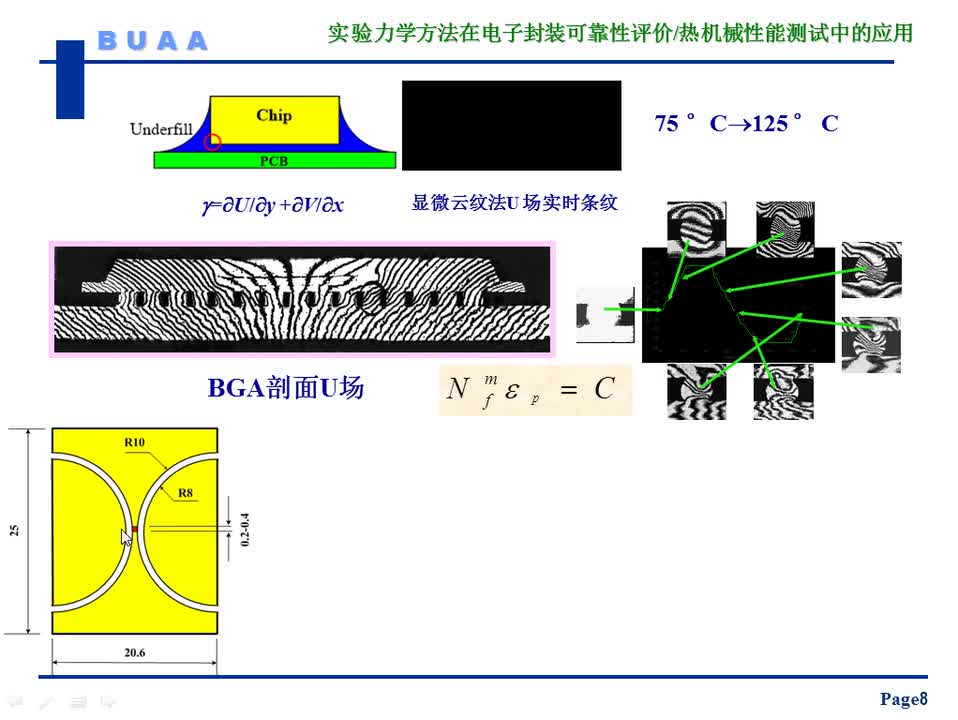

尽管倒装芯片封装有很多优点(如互连引线短、封装密度高),但倒装芯片封装还有很多可靠性方面的问题待解决,如多种材料和多界面的存在使其更脆弱(界面分层、裂纹扩展等)、无铅焊料的使用使其回流焊所需温度更高而更易导致应力/应变集中以及无铅焊料本构模型的选择和寿命评估等。导致倒装芯片封装结构出现可靠性问题的其中一个主要原因就是:芯片与基板的 CTE 的失配(芯片:2.5~3 ppm/K,Al2O3 陶瓷基板:5~6 ppm/K,FR4 电路板:16~20 ppm/K )。1987 年,Nakano 提出,将环氧树脂中掺入 SiO2 颗粒制成的底充胶,填充在芯片与基板之间的空隙,能够使芯片与基板间的热失配得到一定程度的缓解,而且可以大幅度提高焊点的热疲劳寿命(能提高 10~100 倍)。TSUKADA 等使用有机材料印刷电路板作为基板,然后用环氧树脂填充芯片与基板间的间隙,结果显示其性能可以与昂贵的陶瓷基板相媲美。有分析计算指出,焊点间隙充胶后,焊点主要应力比没有充胶时要减小 75% 到 90%。

底部填充胶的使用对倒装芯片封装可靠性的提高是显而易见的,但是底部填充胶引入的同时又出现了另一个可靠性问题。在很多倒装芯片封装热循环测试过程中,芯片和底部填充胶界面间往往会发生分层,这对倒装芯片封装的可靠性有着巨大的影响。而且有文献已经指出,底部填充胶与芯片间的界面分层成为倒装芯片封装主要失效模式之一。所以,随着倒装焊技术的快速广泛应用,对不同界面分层的萌生及其扩展行为进行深入的研究是有必要的。

多层结构和多个界面是倒装芯片封装乃至高密度封装中普遍存在的现象。界面分层失效得到越来越多的重视并逐渐成为整个产品性能和可靠性方面关心的重要问题之一。刘胜课题组通过三点弯曲试验,测定了倒装芯片封装中底部填充胶和芯片界面间的断裂韧度和相对应的相角,并将高温摩尔纹测试和有限单元法相结合,找到了一种评估电子封装界面分层长度的新方法。1998 年,TSUKADA 等利用光学传感器试验测得热循环加载条件下胶/金属片界面间的热疲劳分层扩展速率。2000 年,LAU 等利用有限元模拟仿真技术,进一步研究了倒装芯片封装中的典型界面分层裂纹的传播方式。芯片与底部填充胶界面间分层扩展机理仍值得做进一步研究。

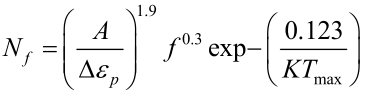

有文献表明,在电子封装所有可能的失效式中,焊点失效是其中的一个主要原因,所以焊点的可靠性在整个电子封装可靠性中都占有重要地位。目前,焊点寿命预测模型多种多样,按照焊点变形机制和失效模式的不同,大致可分为四类:基于塑性应变的模型、基于蠕变的模型、基于能量的模型以及基于断裂参量的模型。由于便捷性、易操作性和合理性,以基于塑性变形的 Coffin-Manson 公式为代表的寿命预测模型被广泛使用;之后,Norris 和 Landzberg 用热循环加载频率因子 f 和最大温度因子Tmax 对传统的 Coffin-Manson 方程进行了修正,得到了焊点寿命预测的经验模型

对于这四种寿命预测模型,到底哪一种模型能更准确地对焊点寿命予以预测,目前为止业内还没有达成一致。因此,针对倒装芯片封装,找到一种能够相对准确预测焊点寿命的模型并揭示电子器件正常工作时焊点的变形机制是十分有意义的。

对于倒装芯片封装,在底部填充胶填充工艺中,难免会引入杂质或者在芯片与焊点连接的角点处难免出现未填满(空洞)的现象,这会对焊点寿命产生巨大影响,如刘胜的文章指出,空洞的产生会使锡铅焊点的疲劳寿命降低 20%左右。同时,失稳扩展至焊点的芯片/底部填充胶界面分层裂纹对无铅焊点疲劳寿命的影响,以及界面分层和空洞对无铅焊点寿命的影响大小比较都还有待做进一步研究。

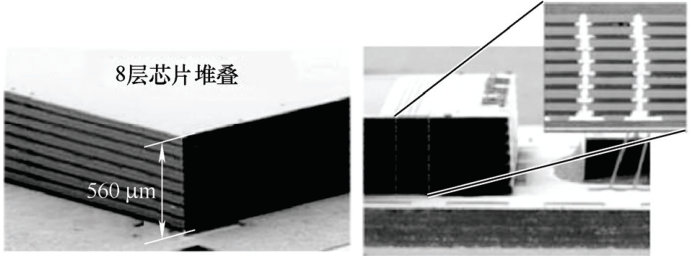

(2) 硅通孔可靠性。 随着电子封装更高密度、更大集成度的要求的出现,系统级集成封装便应运而生,三维异质集成可以将电子、流体、光学等器件集成在一个模块里,以满足其多功能性。但集成封装技术仍带来一些信号延迟、噪声等问题。利用硅通孔(Through silicon via, TSV)技术实现芯片的三维堆叠,可以避免由于引线键合带来的一系列问题。同时,通过芯片与基板之间的中介层,可以实现三维系统级封装。硅通孔三维封装技术通过在芯片之间制作垂直通孔,实现不同芯片的信号传递,大大改善了芯片的转化速度;减小信号传输过程中的寄生损失,能够实现更低功耗和更短的互连长度,满足电子器件的多功能和小型化要求。如图 10 为所示为 8 层三维闪存芯片堆叠封装结构。

图 10 基于硅通孔技术的芯片三维堆叠封装

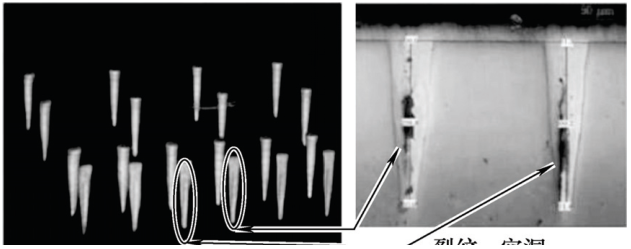

由于硅通孔需要特殊的制造工艺和结构,随之而来也有一系列可靠性问题。比如硅片的减薄技术也尚未完全成熟。在对硅片进行刻蚀通孔之后填充金属,孔的深宽比直接影响着电镀效果,高深宽比会带来一些制造缺陷,如果深孔电镀的工艺参数选择不当,就会导致电镀后的铜柱中存在缺陷。如图 11 所示,硅通孔电镀铜柱的 X 射线图和截面光学图中显示铜柱存在一些裂纹,也有部分空洞散落其中。这些缺陷会对硅通孔的长期可靠性产生直接影响,最终导致硅通孔的性能不能满足工作要求。也有一些工艺过程中导致界面剥离缺陷等,将影响硅通孔结构以及三维封装整体的可靠性。

图 11 TSV 深孔电镀的工艺缺陷

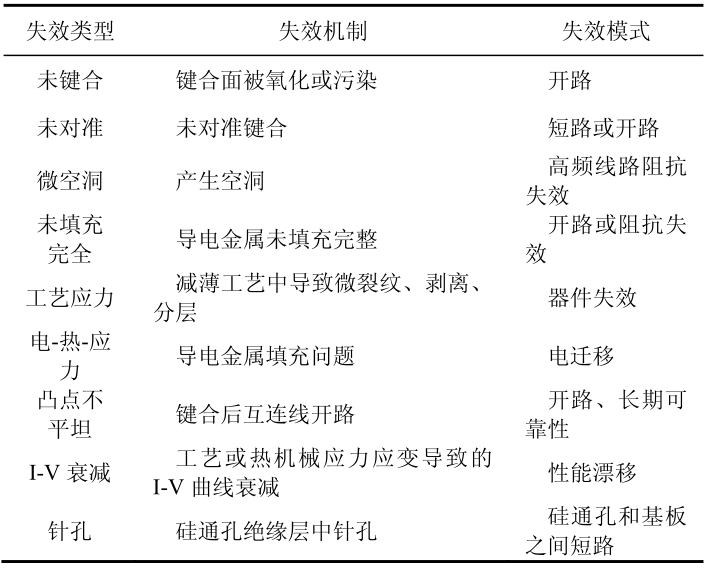

不仅制作工艺过程中会有一些不利因素,当半导体器件暴露在一定的高温环境下,材料的热失配现象出现,引起热应力分布不均,也影响器件工作的稳定性。在器件工作阶段中,过高的温度差也会引发严重的封装器件可靠性问题。目前,基于三维封装分析以及可靠性试验等仍处于不断摸索的研究阶段,相关的可靠性加速试验方法和可靠性标准尚未完全建立起来。常见的失效模式和失效机制如表 2 所示。而失效机制和模式与硅通孔的制作工艺过程也密切相关。在制作 TSV 工艺过程中,如果出现操作不当,则会导致填充金属铜中出现空洞,且在热膨胀系数失配引起的热应力作用下,分层现象很容易出现,甚至会在不同材料的界面上出现裂纹等缺陷,而这些缺陷会影响封装的长期可靠性。

表 2 硅通孔可能出现的失效模式和失效机制

**3 **展望

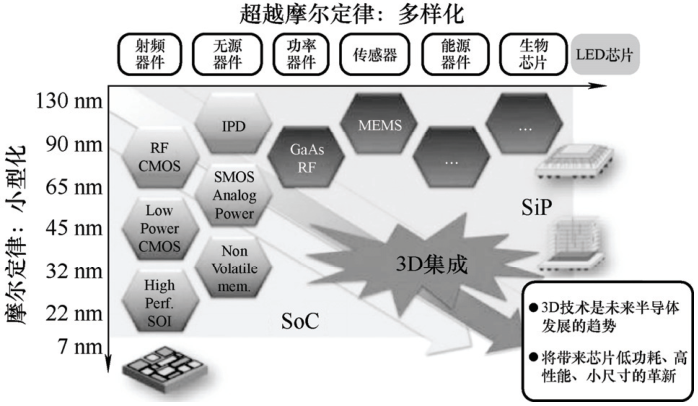

随着市场对电子器件更强功能和更小尺寸的不断追求,未来电子制造技术将主要朝着两个方向发展,如图 12 所示。

图 12 电子封装技术未来发展趋势(修改自 ITRS 路线图)

(1) 深度摩尔定律(More Moore)。 在这一技术路线上,电子制造技术将延续 CMOS 器件小型化的发展方向,通过器件结构、沟道材料、互连引线、高介质金属栅、光刻工艺等各方面持续发展,以延续摩尔定律继续发展。但是,随着特征尺寸的不断下降,栅极氧化层的厚度逼近原子尺度,器件级的量子效应也愈发明显,漏电更加严重,导致晶体管的特性更加难以控制。因此,业界普遍认为摩尔定律正在接近物理极限,制造工艺进步的代价也越来越高。

(2) 超越摩尔定律(More than Moore)。 超越摩尔定律则更加强调功能的多样化,是由应用需求驱动的。深度摩尔定律(More Moore)主要满足了用户对于计算和存储的需求。而超越摩尔定律则更加注重功能的多样化和集成化,如射频电路、MEMS 传感器、电源管理等功能。因此,超越摩尔定律主要有以下内涵:①随着时代的发展,芯片价值的提升除了传统的更高性能以外,新的功能更加重要。用户除了传统的计算和存储需求,还有传输、参数感知、智能化等,以满足对物联网、生物医疗电子等多方面的需求;②芯片集成度的提高也可以通过封装技术来实现,而不一定需要通过同一种先进制程把更多的模块集成到统一芯片上。如模拟/射频/混合信号等模块并不需要最先进的芯片制程工艺,可通过更加成熟的工艺实现最佳性能。而数字模块则可以应用先进工艺。

不同工艺路线制造的模块通过封装技术集成到一起,同样可以实现强大的综合性能和优异的集成度,这种集成方式即异质集成。异质集成技术目前已逐渐成为工业界和学术界的重点发展方向之一。同时其潜在的失效机理和模式也更加复杂,呈现出多尺度、多积累复合失效的特征。为应对这一问题,发展电子器件、模块、系统的在线监测技术显得更加重要。同时,在器件可靠性设计优化过程中,跨阶段协作的、复合场可靠性预测及试验分析也是电子器件未来发展的重要方向。

来源: 半导体在线

作者: 陈志文、梅云辉、刘胜等

审核编辑:汤梓红

德赢Vwin官网

App

德赢Vwin官网

App

评论