引言

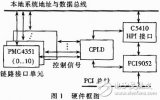

如果把PC机作为控制系统的操作平台,PCI总线作为一种先进的高性能32/64位局部总线正迅速取代原来的ISA总线的主导地位,以用于高速外设,并成为微型计算机系统的主流系统,因而也成为工程开发人员用于工业控制的首选。为了缩短开发周期,一般都采用专用的接口器件。本文就是采用PLX公司的PCI9052来把PCI总线上的操作转换为对局部总线的操作,同时通过双口RAM实现和下位机的存储转接。针对一般PCI总线开发时由于软硬件分离使开发的软硬件不能很好结合的现象,本文结合实例介绍了应用程序并给出了如何通过DriverStudio开发的PCI设备驱动程序来访问PCI设备卡硬件资源的具体程序。

1、 PCI的配置空间及其配置

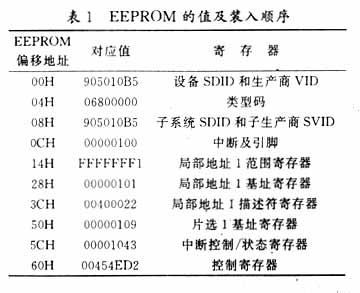

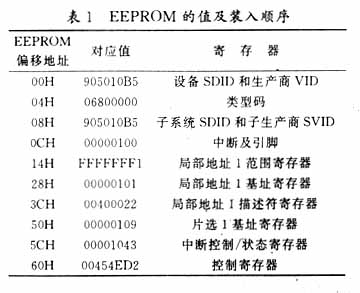

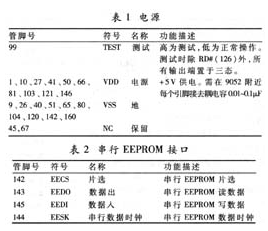

PCI总线支持存储器地址空间、I/O地址空间和配置空间等三个物理空间。其中,配置空间是PCI总线所特有的一个空间,PCI总线能实现即插即用的功能,正是通过它特有的配置空间来实现的。PCI配置空间的大小为256字节,分为头标区和设备有关区。直接影响设备特性的配置寄存器在头标区,其他部分则因设备而异。PCI总线的配置空间通常与PCI接口芯片相关。该配置空间包括一系列的PCI配置寄存器。本文采用的PCI9052芯片的配置寄存器分为PCI配置寄存器和局部配置寄存器,二者都可以由PCI总线和串行EEPROM访问。

在PCI配置寄存器中的设备ID、制造商ID、版本号、首区类代码、类别代码、指令寄存器和状态寄存器等寄存器在所有的PCI设备中都必须实现,通常情况下,操作系统可使用这些寄存器的内容来决定该PCI设备的加载其驱动程序。

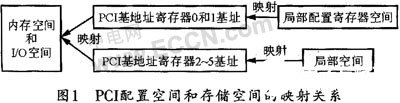

PCI总线最重要的功能之一是通过基地址寄存器和局部配置寄存器在地址空间重定位PCI设备。系统上电时,通过上层应用软件能判断系统中存在那些设备,并建立协调的地址映射。所以,基地址寄存器和局部配置寄存器是实现驱动程序的关键。

PCI配置寄存器提供有6个基地址寄存器(BASE0~BASE5)这些基地址都是系统中的物理地址,其中BASE0和BASE1是用来访问局部配置寄存器的基地址,BASE0是映射到内存的基地址,BASE1是映射到I/O的基地址,可用于通过内存和I/O来访问局部配置寄存器。这两个基地址可固定用于PCI9052芯片的寄存器操作。

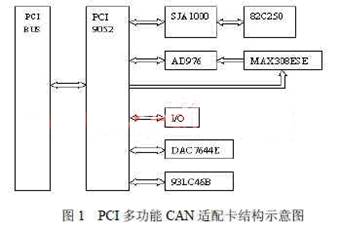

通过BASE2~BASE5四个空间最多可以访问局部端所接的4个芯片,实现4个局部地址空间(局部空间0~3)的PCI总线访问。PCI总线对局部端所接芯片的局部地址映射是通过4个寄存器组(PCI基地址寄存器,局部范围寄存器,局部基地址寄存器,局部总线区域描述符)来实现的。这个组定义了每个空间以及相应局部空间的特性。它们将局部端的芯片通过局部端地址(在局部配置寄存器中设置)翻译成PCI总线地址,也就是将本地的芯片映射到系统的内存或I/O口。而片选信号寄存器则是用来选定这些局部端所接的芯片的。这样,用程序操作这一段内存(或I/O)实际上就是对本地芯片的操作。其映射关系如图1所示。这些寄存器的内容必须在芯片复位时通过串行E2PROM进行加载,而正确配置E2PROM的内容则是使用PCI9052的关键。

本设计选取LAS0(Local Address Space 0)来访问局部端的双口RAM芯片中的2 KB寻址空间,与其有关的寄存器有四个:LAS0范围寄存器、LAS0局部基址寄存器、LAS0局部总线区域描述符和片选0基址寄存器。LAS0范围寄存器规定了地址空间的大小。由于需要2 KB的内存空间,而计算机预留了32 KB空间(即8000H),所以其寄存器值为0xFFFF8000H,而类型则是不可预取的;LAS0局部基地址寄存器定义了设备卡资源上所占用的基地址,它的最终目的是将这个基地址重新映射到PCI地址空间。由于基地址必须是32KB的整数倍,因此,为方便起见,可以将基地址定为00000000H,又由于位0为空间使能位,所以,寄存器的值为00000001H;LAS0局部总线区域描述符用来定义地址空间0的具体工作特性。

该总线采用16位总线宽度,工作方式定义为不使能突发和不预取,因此,该寄存器的数值初步确定为4043A1C0H,最终的值则需要不断测试才能确定;片选0基址寄存器使用PCI9052的CS0#作为双口RAM的片选信号,CS0#片选信号的起始地址和地址范围由片选0基址寄存器设置,局部总线的容量是2 KB,第11位为1,基地址是该范围的16倍,一般将倍数放置在范围位之后,所以寄存器值设置为0xO008401。当从局部空间0基址开始的2 KB空间范围落在CS0基地址寄存器所设置的范围内,CS0端有效,这种方式可减少地址译码得到的片选逻辑。

用PLX9052可将PCI总线上的操作转换为对局部总线的操作,即通过LAD0~LAD7、RD、WR、CS等对局部端芯片访问。如果系统分配给本卡的存储空间为FFFF0000H~FFFF7FFFFH。那么,当系统通过PCI总线访问这个区域时,PLX9052就会应答,并将其转换为局部地址0x0000H~0x07FFH,另外,PLX9052自身也有一些内部寄存器,它们被自动映射到另一片内存区域,可通过PCI总线直接访问。

PCI9052提供了两种类型的中断源(硬件中断和软件中断)。中断可通过PCI9052中断控制/状态寄存器来(INTCSR)允许和禁止。PCI9052通过2个局部中断引脚来实现硬件中断,它们支持边缘和电平触发中断,可以通过对INTCSR寄存器的编程来实现局部中断,然后产生PCI中断(INTA),并生成PCI中断INTA#方式。PCI9052可以软件方式产生中断,设计时只需要将INTCSR寄存器的软件中断位设置为1即可。

2、 驱动程序的开发

在开发PCI板卡功能驱动程序之前,首先要明白所需的PCI硬件资源,并针对设备卡的硬件资源来处理PCI设备的内存、端口的读写,以及中断处理,从而实现PCI设备功能。

2.1 驱动程序在操作系统体系结构中的位置

操作系统结构可分为五层模型:

(1)用户应用程序;

(2)IO管理层;

(3)驱动程序;

(4)HAL(硬件抽象层);

(5)硬件。

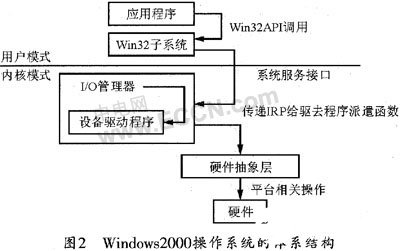

图2给出了Windows2000操作系统驱动程序开发者所关心的特征,一般情况下,软件要么在用户模式中执行,要么在内核模式下执行。从驱动开发的角度上看,WDM模型为存在于Win-dows2000系统中的驱动程序提供了一个参考框架。作为Windows2000系统结构开发人员,由于操作系统为应用程序,而在驱动程序和硬件之间提供有系统服务接口和平台相关操作,因此,设计时只需要关注应用程序和设备驱动程序的开发。

2.2 设备资源

PCI设备的硬件资源分配与管理是驱动程序很重要的部分,设备的硬件资源包括内存空间、I/O空间和中断。由于PCI总线为PnP总线,PCI设备的硬件资源是由PCI配置机构动态分配给PCI配置寄存器的,因此,驱动程序首先需要取得这些资源才能操作硬件。当PnP管理器检测到PCI设备时,系统就会发送IRP_MN_START_DEVICE的IRP给驱动程序,驱动程序调用OnStartDevice以启动例程处理,并在启动例程里获取该IRP栈,同时把它包含的系统分配给该设备的资源信息。

用DriverStudio开发驱动程序时,应在Wizard中设置好PCI设备的资源。对于实际的PCI9052设备卡,其基地址寄存器0和1分别固定用于PCI9052局部寄存器的内存映射地址和I/O映射地址,基地址寄存器2则用于设备卡的内存映射地址,并使用局部中断引脚来产生PCI中断,以分别生成对应的KIoRange类、KMemoryRange类和KInterrupt类。这些配置信息由配置管理器发送到OnStartDevice中重载该成员函数,而开发者则不必再处理。在一般情况下,驱动程序无需再访问PCI设备的配置空间,如果需要访问,则可通过类KPciConfiguration,该类包含了通过向PCI总线发送渎写配置空间的IRP操作。也可定义类KRe-sourceAssignment来获取PCI的端口地址和中断号以及内存地址和大小,并把得到的资源放在用户自己定义的变量中。

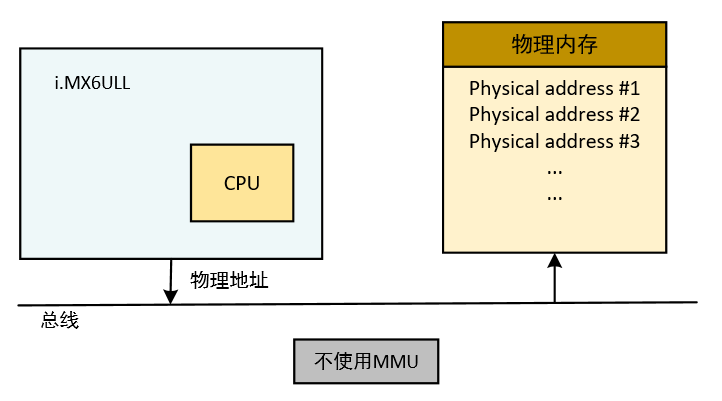

2.3 WDM驱动程序对硬件资源的访问

获取设备的硬件资源以后,就可以对硬件资源进行访问了。对硬件的访问一般包括I/O端口访问和内存访问,它们分别对应PCI配置空间的I/O空间和内存空间。从图2可以看出,当应用程序需要访问设备时,它就会调用Win32API函数(如ReadFile)。Win32子系统模块通过调用平台相关的系统服务接口实现该API,而平台相关的系统服务则调用内核模式来支持例程。即在调用ReadFile函数时,首先到达系统的人口点,然后调用系统服务接口,最后由系统调用内核模式的服务例程。执行时首先检查传递给它们的参数,然后创建一个“I/O请求包(IRP)”的数据结构,并把这个数据结构送到某个驱动程序的入口点执行IRP设备驱动程序,最后再访问硬件。对于PIO方式的设备,一个IRP_MJ_READ操作将直接读取设备的端口或设备的内存寄存器。一般会使用硬件抽象层(HAL)来访问硬件。IRP贯穿于驱动程序之间,它在应用程序、驱动程序和设备之间起着桥梁作用,可称之为内核态的“消息”。驱动程序完成一个I/O操作后,可通过调用一个特殊内核模式服务例程来完成该IRP,完成操作时再处理IRP的最后工作,以它使等待的应用程序恢复运行。

用DriverStudio开发驱动程序时,可根据配置声明KIoRange类、KMemoryRange类和KInterrupt类来实现对内存空间、I/O空间、中断的操作。在本例中,基地址寄存器0和1固定用于PCI9052芯片的操作寄存器内存映射地址和I/O映射地址,基地址寄存器2则用于双口RAM的内存映射。通过一个外部引脚即可产生中断。标识两个KMem-oryRange类实例、一个KIoRange类实例和一个KInterrupt类实例的具体实现细节如下:

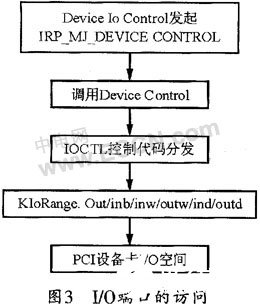

(1) I/O端口的访问

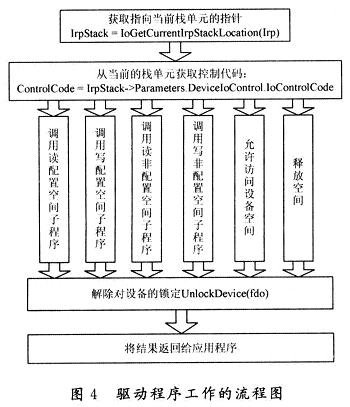

I/O端口的访问流程如图3所示,应用程序通过API函数DeviceIoControl的调用,并调用驱动程序的分发例程DeviceControl,同时通过KIoRange类来实现对I/O映射空间的访问。需要注意的是,当DeviceloControl异步调用的时候,必须在驱动程序中添加取消例程,并在DeviceControl例程中阻止一个应用程序对其的多次调用。KIoRange类的成员函数outb、inb、outw、inw、ind、outd可分别用于从端口读或写一个字节、字和双字数据。在WDM中,对于I/O端口,系统可将其看成寄存器,一般用于数字传输量比较小的地方。在对PCI设备的访问中,I/O端口的访问通常比较频繁。

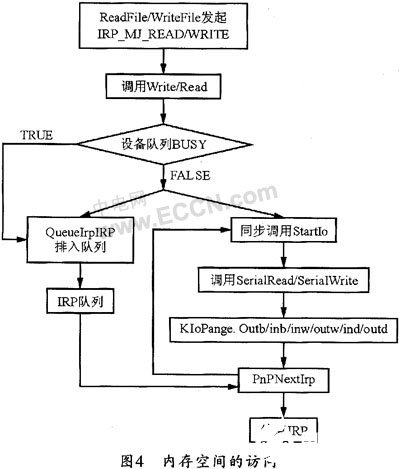

(2) 内存的访问

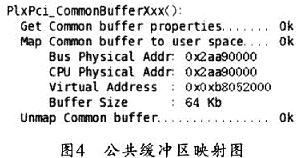

在基于DriverStudio开发的驱动程序中,向存储器空间读写大量数据一般选用Write/Read函数,但对于一个实际存在的物理设备的访问,在某一时刻只能进行一个操作,因而在访问内存对象的时候,一般都要求一个IRP排队的队列,可通过设备类的成员函数QueueIrp将IRP插入队列。DriverWorks提供有KDeviceQueue类,其成员函数StartIo用于处理设备对象的IRP队列。具体的操作是通过KMemoryRange类来实现对设备内存映射空间的访问。其访问流程见图4所示。需要注意的是,当IRP队列为空时,调用QueueIrp时,系统将同步调用StartIo函数。

(3) 中断处理

驱动程序的中断处理编程涉及到内核机制比较多的一种驱动程序,因而相对复杂。首先用中断服务程序提升系统的IRQL,但不能进行大多数有用的内核调用。另外,提升IRQL运行代码需要尽可能快地运行。所以,中断处理一般和在DIS-PATCH_LEVEL级运行的延迟调用(DPC)例程相配合可解决以上两个问题。在DriverWorks中,通常通过KInterrupt类和KDeferredCall类来实现,并通过向导来在中断服务例程和DPC中增加功能代码。KDeferredCall类封装有DPC的操作。KInter-rupt类用于实现硬件中断的处理,其成员函数包括中断初始化,以及将一个中断服务例程连接到另一个中断和解除其连接等。在中断服务例程中把IRP交给DPC例程,可在DPC处理完后结束该IRP。需要注意的是,中断服务例程不是KInter-rupt类的成员函数,它的主要作用是减少中断延迟时间。

3、 结束语

本文主要从访问设备硬件资源的角度介绍了PCI配置空间的配置和驱动程序的开发方法。利用该方法可对PCI板卡的配置空间和所需的硬件资源进行正确设置,然后通过DriverStudio的驱动程序向导生成工具在程序框架里添加适当的代码,最后借助于DriverStudio开发包提供的调试工具SoftICE和DriverMonitor以及由Wizard产生的控制台应用程序,来快速开发出基于PCI总线的设备驱动程序。

责任编辑:gt

德赢Vwin官网

App

德赢Vwin官网

App

评论