1. 背景 这篇文章主要介绍了DDR3IP核的写实现。 2. 写命令和数据总线介绍 DDR3 SDRAM控制器IP核主要预留了两组总线,一组可以直接绑定到DDR3 SDRAM芯片端口,一组是留给

2020-12-31 11:17:02 5068

5068

2、512Mb-2Gb LP DDR2,以及 LP DDR4x、LP DDR3、LP DDR、SDRAM,适用于需配备4Gb 或以下容量DRAM 的应用, 如人工智能加速器、物联网、汽车、工业用、电信、

2022-04-20 16:04:03 2554

2554

DDR SDRAM(Double Data Rate Synchronous Dynamic Random Access Memory,双数据率同步动态随机存储器)通常被我们称为DDR,其中的“同步

2023-03-07 11:29:43 3208

3208

DDR SDRAM参考设计VHDL版(有详细的文档,仿真综合文件)File/Directory Description

2012-08-11 09:33:30

引言 很多嵌入式系统,特别是应用于图像处理与高速数据采集等场合的嵌入式系统,都需要高速缓存大量的数据。DDR(Double DataRate,双数据速率)SDRAM由于其速度快、容量大,而且价格便宜

2018-12-18 10:17:15

DDR SDRAM内存发展历程

2021-01-06 06:04:22

DDR SDRAM访问特性DDR控制器效率对比

2021-02-04 07:14:23

我手上有一张DDR200T的开发板,板载了一块512M的SDRAM内存,板子烧了一个UX600的demosoc,我是要在这个板子跑RT-Thread。

要是想使用这块SDRAM应该怎么做呢?应该

2023-08-11 08:05:46

DDR4 SDRAM的寻址方式有哪些?

2021-10-27 06:50:24

DDR4,DDR3,DDR2,DDR1及SDRAM有什么不同之处?

2021-03-12 06:22:08

DDR_SDRAM控制器的VHDL代码已经测试

2016-08-24 16:49:35

使用公式分析和理论分析两种方法,以实例证明公式的局限性和两种方法的利弊。本文最后还基于这些实例分析,给出了SDRAM和DDR SDRAM等布线的一般性原则。

2021-05-19 06:52:58

SDRAM和DDR布线技巧ecos应用是与硬件平台无关的,虽然开发板没有涉及到SDRAM和DDR,不过,在某些高端平台上使用ecos可能会遇到内存布线问题,为了完整叙述,这里一并给出说明。&

2010-03-18 15:33:07

SDRAM和DDR的具体区别是什么?

2021-06-18 07:58:51

;如果上一次执行了写操作,则此次执行读操作。如果不是同时出现读写请求,则是什么请求就执行什么操作。2)采用全页模式的读写操作,该模式在读、写完成时,需要给出预充电命令才能结束。3)刷新请求始终优于读、写请求。DDR的时序与SDRAM是相似的,学好SDRAM后,理解DDR2和DDR3就非常容易了。

2017-11-23 11:02:27

本篇文章英尚微电子存储芯片供应商主要详细介绍下ARM里的ram和SDRAM有什么区别,首先介绍了ram及SDRAM做了详细阐述,最后介绍了两者的区别。

2021-04-02 06:46:51

SDRAM SLICE CARD

2023-03-30 12:05:53

XILINX 关于FPGA 对DDR SDRAM 的设计文档

2012-08-17 09:20:26

在电脑上拆到2条rdram内存条,这个和sdram内存条有什么区别,可以兼容吗

2023-10-08 09:01:45

嗨!我正在寻找Spartan-3A / 3ANFPGA入门KitBoard用户指南(UG334)。具体来说第13章:DDR2 SDRAM和我不明白如何使用DDR2 SDRAM,因为例如这个内存

2019-07-31 06:18:10

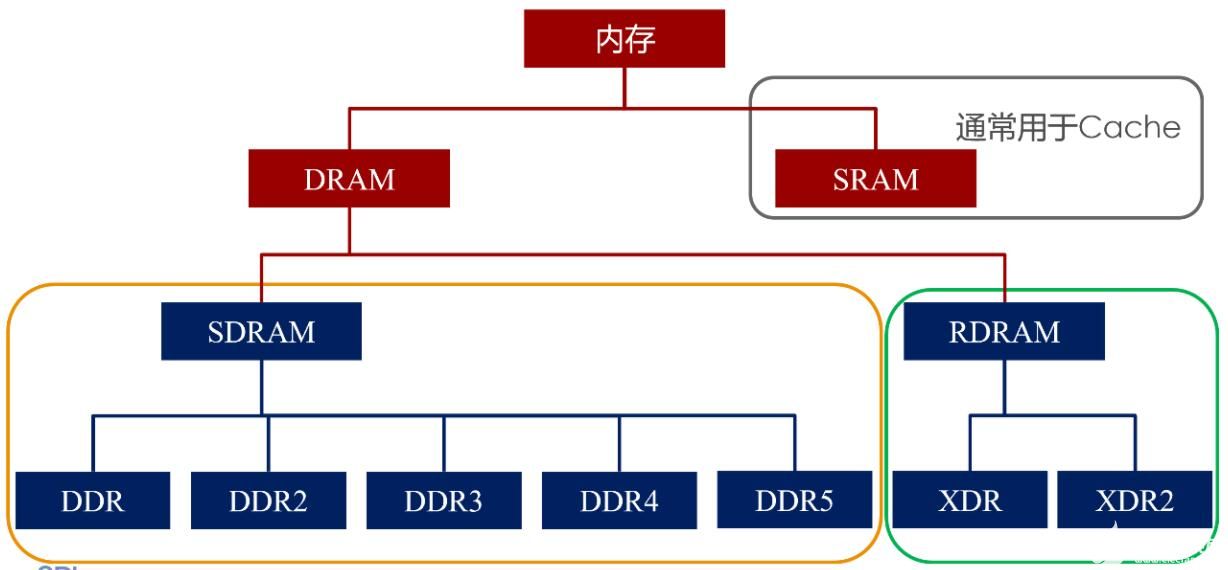

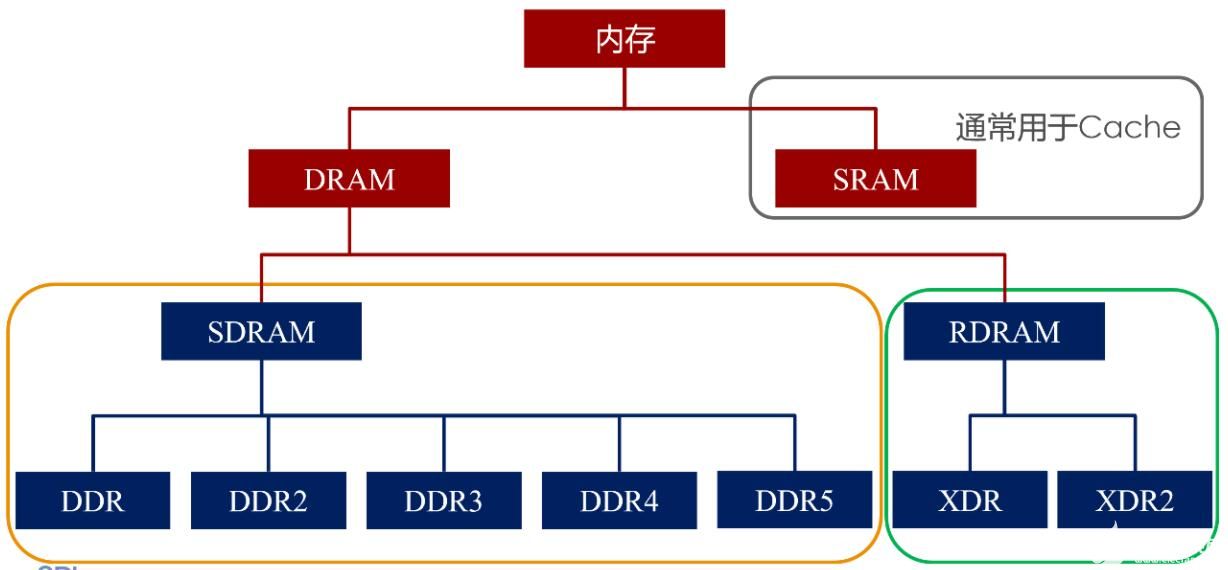

本文概括阐述了DRAM 的概念,及介绍了SDRAM、DDR SDRAM、DDR2 SDRAM、DDR3 SDRAM、DDR4 SDRAM、LPDDR、GDDR。

2021-04-20 06:30:52

/DDR/DDR2芯片的datasheet细细比对,也许用这篇文比较也无法完全说明白他们的迥异,但是至少特权同学希望通过这篇文章能够让大家对他们之间的区别有一个大概的认识,尤其一样对SDR SDRAM

2014-12-30 15:22:49

DDR SDRAM在嵌入式系统中有哪些应用?DDR SDRAM的工作方式有哪几种?怎样去设计DDR SDRAM控制器?

2021-04-30 07:04:04

,F-RAM,MRAM(非易失性存储器)256Kbit-16Mbit8.Mobile SDRAM/DDR(低功耗SDRAM/DDR)128Mbit-512Mbit9.DDR2/DDR3 SDRAM (动态随机

2013-08-30 10:31:33

DDR SDRAM is a 2n prefetch architecture with two data transfers perclock cycle. In the 2n prefetch

2009-03-28 14:43:47 56

56 files *top.v* is the source file for DDR SDRAM controller

2009-05-14 10:46:50 37

37 ref ddr sdram verilog源代码

File/Directory Description

2009-06-14 08:48:01 82

82 =============================================doc DDR SDRAM reference design documentationmodel Contains the vhdl SDRAM model

2009-06-14 08:49:23 51

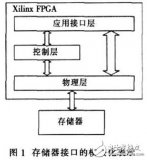

51 DDR2 SDRAM控制器的设计与实现

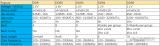

本文介绍了&&," -&,+. 的基本特征!并给出了一种&&," -&,+. 控制器的设计方法!详述了其基本结构和设计思想!并使用+JC:8B 公

2010-02-09 14:57:51 64

64 SDRAM的原理和时序

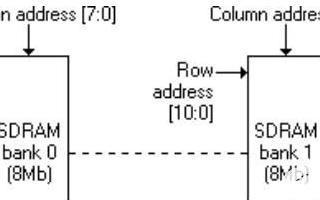

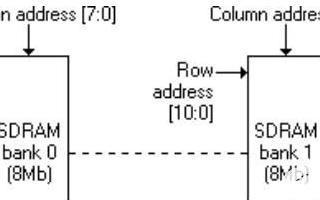

SDRAM内存模组与基本结构 我们平时看到的SDRAM都是以模组形式出现,为什么要做成这种形式呢?这首先要接触到两个概念:物理Bank与芯片位宽

2010-03-11 14:43:26 167

167 SDRAM与DDR布线指南:ecos应用是与硬件平台无关的,虽然开发板没有涉及到SDRAM和DDR,不过,在某些高端平台上使用ecos可能会遇到内存布线问题,为了完整叙述,这里一并给出说明。 很

2010-03-18 15:29:08 0

0 SDRAM设计详细说明

完成SDRAM的上层驱动设计,对SDRAM读写、管理无误,与其他模块的接口正确。

口令:MMCTEAM

SDRAM的工作原理

2010-04-22 14:02:57 0

0 嵌入式测试和测量挑战目录引言3-4DRAM发展趋势 3DRAM4-6SDRAM 6-9DDR SDRAM6DDR2 SDRAM 7DDR3 SDRAM 8DDR4 SDRAM 9GDDR 和LPDDR 9DIMMs 9-13DIMM 物理尺寸 9DIMM

2010-06-30 09:28:08 94

94 本文介绍了DDR3 SDRAM 的基本特点和主要操作时序,给出了一种基于ALTMEMPHY宏功能的DDR3 SDRAM控制器的设计方法。详述了控制器基本结构和设计思想,分析了各模块功能与设计注意事项,并

2010-07-30 17:13:55 30

30 DDR2 SDRAM 和 FB-DIMM的电气检验:

随着DDR2 SDRAM时钟频率和信号边沿速率不断提高,检查电路板结构、电气系统和信令正变得越来越重要。本应用指南介绍了电路板、电源系统、

2010-08-06 08:29:01 39

39 不只计算机存储器系统一直需要更大、更快、功率更低、物理尺寸更小的存储器,嵌入式系统应用也有类似的要求。本应用指南介绍了逻辑分析仪在检验DDR, DDR2 和DDR3 SDRAM 命令和

2010-08-06 08:29:49 79

79 本文将介绍DDR SDRAM的一些概念和难点,主要结合上一篇SDRAM的介绍加以对比。同时着重讲解主流DDRII的技术。最后结合硬件设计提出一些参考。

DDR SDRAM全称为Double Dat

2010-08-30 16:26:16 119

119 什么是DDR SDRAM内存

DDR是一种继SDRAM后产生的内存技术,DDR,英文原意为“DoubleDataRate”,顾名思义,就是双数据传输模式。之所以称其为“双”,也

2009-12-17 11:15:53 1646

1646 什么是DDR2 SDRAM

DDR2的定义:

DDR2(Double Data Rate 2) SDRAM是由JEDEC(电子设备工程联合委员会)进行开发的新生代内存技

2009-12-17 11:17:59 623

623 SDRAM内存 SDRAM是Synchronous Dynamic Random Access Memor

2009-12-17 16:15:28 636

636 DDR SDRAM内存

DDR SDRAM是Double Dat

2009-12-17 16:20:33 684

684 文中在介绍DDR2的工作原理的基础上,给出了一个用VHDL语言设计的DDR2 SDRAM控制器的方法,并且提出了一种在高速图像处理系统中DDR2 SDRAM的应用方案,同时在Virtex-5系列的FPGA上得到了实现

2011-07-23 10:03:16 5102

5102 定义了时钟单位阶跃信号C(n) 提出了一种利用带相对时钟坐标的逻辑方程表示逻辑信号的方法通过对所设计的DDR SDRAM控制器的读写时序的分析建立了控制器主要信号的时序表达式并利用

2011-09-26 15:34:12 39

39 虽然目前SDRAM内存条价格已经接底线,内存开始向DDR和Rambus内存过渡。但是由于DDR内存是在SDRAM基础上发展起来的,所以详细了解SDRAM内存的接口和主板设计方法对于设计基于DDR内存的主

2012-01-05 16:21:11 247

247 使用功能强大的FPGA来实现一种DDR2 SDRAM存储器的用户接口。该用户接口是基于XILINX公司出产的DDR2 SDRAM的存储控制器,由于该公司出产的这种存储控制器具有很高的效率,使用也很广泛,

2013-01-08 18:15:50 237

237 DDR SDRAM 全称为Double Data Rate SDRAM,中文名为双倍数据流SDRAM。DDRSDRAM 在原有的SDRAM 的基础上改进而来。也正因为如此,DDR 能够凭借着转产成本优势来打败昔日的对手RDRAM,成为当今的主流

2013-09-13 15:17:30 210

210 ddr2_sdram 操作时序,非常好的教程,可以充分了解DDR2

2015-10-28 11:07:39 19

19 DDR_SDRAM介绍和时序图,DDR_SDRAM介绍和时序图

2016-02-23 11:58:38 6

6 Xilinx FPGA工程例子源码:DDR SDRAM控制器参考设计VHDL代码

2016-06-07 11:44:14 19

19 Xilinx FPGA工程例子源码:DDR SDRAM控制器verilog代码

2016-06-07 14:13:43 38

38 一种面向多核系统的DDR2SDRAM控制单元_章裕

2017-01-03 18:00:37 5

5 作者:Steve Leibson, 赛灵思战略营销与业务规划总监 Adrian Cosoroaba和Terry Magee在本月MemCon上给出了关于DDR4 SDRAM接口的详细展示,该演示

2017-02-08 14:03:01 608

608 DDR2SDRAM控制器在机载显控系统中的应用_孙少伟

2017-03-19 11:26:54 1

1 DDR2_DDR3_SDRAM,PCB布线规则指导

2017-10-31 10:06:48 78

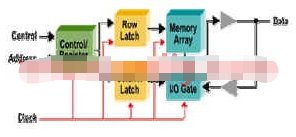

78 SRAM是靠双稳态触发器来记忆信息的;SDRAM是靠MOS电路中的栅极电容来记忆信息的。由于电容上的电荷会泄漏,需要定时给与补充,所以动态RAM需要设置刷新电路。但动态RAM比静态RAM集成度

2017-11-03 18:26:43 5231

5231 DDR3 SDRAM(Double Data Rate Three SDRAM):为双信道三次同步动态随机存取内存。

DDR4 SDRAM(Double Data Rate Fourth

2017-11-17 13:15:49 25152

25152 在高速信号处理系统中, 需要缓存高速、大量的数据, 存储器的选择与应用已成为系统实现的关键所在。DDR SDRAM是一种高速CMOS、动态随机访问存储器, 它采用双倍数据速率结构来完成高速操作

2018-07-20 18:38:00 12744

12744

DRAM (动态随机访问存储器)对设计人员特别具有吸引力,因为它提供了广泛的性能,用于各种计算机和嵌入式系统的存储系统设计中。本文概括阐述了DRAM 的概念,及介绍了SDRAM、DDR SDRAM、DDR2 SDRAM、DDR3 SDRAM、DDR4 SDRAM、LPDDR、GDDR。

2018-06-07 22:10:00 91644

91644 DDR SDRAM全称为Double Data Rate SDRAM,中文名为双倍数据流SDRAM。DDR SDRAM在原有的SDRAM的基础上改进而来。也正因为如此,DDR能够凭借着转产成本优势

2018-03-16 14:24:01 32

32 本文主要介绍的是ARM里的RAM和SDRAM有什么区别,首先介绍了RAM的类别及特点,其次对SDRAM做了详细阐述,最后介绍了RAM和SDRAM的区别是什么。

2018-04-27 16:20:52 34171

34171 实现数据的高速大容量存储是数据采集系统中的一项关键技术。本设计采用Altera 公司Cyclone系列的FPGA 完成了对DDR SDRAM 的控制,以状态机来描述对DDR SDRAM 的各种时序

2019-08-14 08:00:00 3401

3401

本文档的主要内容详细介绍的是FPGA读写SDRAM的实例和SDRAM的相关文章及一些SDRAM控制器设计论文主要包括了:FPGA读写SDRAM的实例,SDRAM控制器核心介绍,系列SDRAM数据手册

2018-12-25 08:00:00 56

56 的。 SDRAM,同步的DRAM,即数据的读写需要时钟来同步。 DRAM和SDRAM由于实现工艺问题,容量较SRAM大。但是读写速度不如SRAM,但是现在,SDRAM的速度也已经很快了,时钟好像已经有150兆的了。那么就是读写周期小于10ns了。SDRAM虽然工作频率高,但是实际吞吐率要打折扣。

2019-04-01 16:24:29 35283

35283 SDRAM从发展到现在已经经历了五代,分别是:第一代SDR SDRAM,第二代DDR SDRAM,第三代DDR2 SDRAM,第四代DDR3 SDRAM,第五代,DDR4 SDRAM。

2019-09-12 07:02:00 2009

2009

SDRAM在计算机中被广泛使用,从起初的SDRAM到之后一代的DDR(或称DDR1),然后是DDR2和DDR3进入大众市场,2015年开始DDR4进入消费市场。

2019-09-11 07:09:00 2239

2239

DDR2 设备概述:DDR2 SDRAM接口是源同步、支持双速率传输。比如DDR SDRAM ,使用SSTL 1.8V/IO电气标准,该电气标准具有较低的功耗。与TSOP比起来,DDR2 SDRAM的FBGA封装尺寸小得多。

2019-06-22 10:05:01 1793

1793

本文件定义了DDR3 SDRAM规范,包括特性、功能、交直流特性、封装和球/信号分配。本文档的目的是为符合jedec的512 MB到8 GB的x4、x8和x16 ddr3 sdram设备定义一组最低

2019-11-04 08:00:00 73

73 H57V1262GTR SDRAM模块B型

SDRAM外扩存储 8Mx16bit

型号 SDRAM Board (B)

2019-12-30 09:01:47 1197

1197

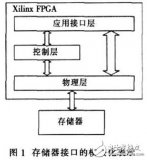

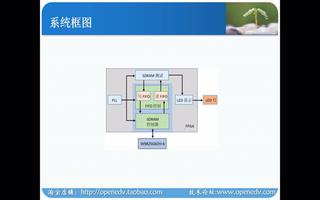

学完SDRAM控制器后,可以感受到SDRAM的控制器的书写是十分麻烦的,因此在xilinx一些FPGA芯片内已经集成了相应的IP核来控制这些SDRAM,所以熟悉此类IP核的调取和使用是非常必要的。下面我们以A7的DDR3 IP核作为例子进行IP核调取。

2019-11-10 10:28:45 4702

4702

DDR5 是第五代 DDR SDRAM 的简称,DDR SDRAM 是英文 Double Data Rate SDRAM 的缩写,中文译为双倍速率 SDRAM,而 SDRAM 又是

2020-02-03 18:30:59 5442

5442 SDRAM从发展到现在已经经历了五代,分别是:第一代SDR SDRAM,第二代DDR SDRAM,第三代DDR2 SDRAM,第四代DDR3 SDRAM,第五代DDR4 SDRAM。第一代SDRAM

2020-04-03 16:04:01 1489

1489 DDR2 SDRAM采用双数据速率结构实现高速运行。双数据速率体系结构本质上是4n预取体系结构,其接口设计为在I/O球处每个时钟周期传输两个数据字。DDR2 SDRAM的单次读写操作有效地包括在内部

2020-05-21 08:00:00 1

1 接口的异步DRAM相比,可以有一个更复杂的操作模式。下面宇芯电子介绍关于静态SDRAM和动态SDRAM的区别。 静态记忆 假设我们要将16Mb存储器连接到FPGA。 16Mb表示内存可容纳1600万位(准确地说是16777216位)。现在,很少对比特进行单独寻址,而是通常以8或16的数据包(

2020-06-24 12:01:55 733

733

DDR SDRAM是具有双倍数据传输率的SDRAM,其数据传输速度为系统时钟频率的两倍,由于速度增加,其传输性能优于传统的SDRAM。DDR SDRAM 在系统时钟的上升沿和下降沿都可以进行

2020-07-16 15:44:10 1938

1938 SDRAM从发展至今历经了五代,分别是:第一代SDR SDRAM,第二代DDR SDRAM,第三代DDR2 SDRAM,第四代DDR3 SDRAM,第五代DDR4 SDRAM,SDRAM有一个同步

2020-07-24 14:25:27 719

719 DDR SDRAM的原理及特点:DDR SDRAM不需要提高时钟频率就能加倍提高SDRAM的速度,因为它允许在时钟脉冲的上升沿和下降沿读写数据。至于地址和控制信号,还是跟传统的SDRAM一样,在时钟的上升沿进行传输。

2020-08-10 17:33:21 603

603

SDRAM从SDR到DDR再到DDR2一路走来,又都产生了什么样的变化,又都在哪些方面进行了改进,带来了速度性能的进一步提升呢?

2020-09-26 11:47:34 10668

10668 。SDRAM可称为SDRSDRAM。 DDR其实指的是DDRSDRAM,SDRAM及DDR主要差异有三点整理如下: SDRAM与DDR的主要差异

2021-02-22 15:35:48 3111

3111

本文首先分析了DDR SDRAM的基本特征,并提出了相应的解决方案详细介绍了基于J EDEC DDR SDRAM规范的DDR SDRAM控制器设计方案。该控制器采用Verilog HDL硬件描述语言实现,并集成到高性能SoC中。

2021-03-28 10:57:24 18

18 基于FPGA的DDR3SDRAM控制器设计及实现简介(arm嵌入式开发平台PB)-该文档为基于FPGA的DDR3SDRAM控制器设计及实现简介资料,讲解的还不错,感兴趣的可以下载看看…………………………

2021-07-30 09:05:51 7

7 基于FPGA的DDR3SDRAM控制器设计及实现(嵌入式开发式入门)-该文档为基于FPGA的DDR3SDRAM控制器设计及实现总结文档,是一份很不错的参考资料,具有较高参考价值,感兴趣的可以下载看看………………

2021-07-30 13:07:09 35

35 SDRAM有一个同步接口,在响应控制输入前会等待一个时钟信号,这样就能和计算机的系统总线同步。时钟被用来驱动一个有限状态机,对进入的...

2022-01-26 19:40:35 1

1 APM32E103VET6S_SDRAM模块_SDRAM与IO口冲突问题

2022-11-09 21:03:42 0

0 8Gb DDR4 SDRAM B裸片组织为128Mbit x 4 I/O x16banks或64Mbit x8 I/O x 16banks设备。此同步设备实现高达2666Mb/sec的高速双数

2022-12-05 11:54:24 11

11 DDR3 SDRAM使用双倍数据速率架构来实现高速操作。双倍数据速率结构是一种8n预取架构,其接口经过设计,可在I/O引脚上每个时钟周期传输两个数据字。DDR3 SDRAM的单个读或写操作有效地包括

2023-02-06 10:12:00 3

3 DDR SDRAM(Double Data Rate Synchronous Dynamic Random Access Memory,双数据率同步动态随机存储器)通常被我们称为DDR

2023-03-07 11:33:57 1653

1653 SDRAM有多种标准,包括DDR(Double Data Rate)、DDR2、DDR3和DDR4。每个标准都具有不同的物理规格和数据传输速率。DDR4是现代计算机中使用的最新型号,它具有更高的频率和更大的容量。

2023-08-26 11:57:42 2054

2054 德赢Vwin官网

网站提供《PIC32系列参考手册之DDR SDRAM控制器.pdf》资料免费下载

2023-09-25 11:39:59 0

0 SDRAM与DDR布线指南

2022-12-30 09:20:50 10

10 JESD79-5B DDR5 SDRAM-2022 JEDEC

2023-12-25 09:51:55 2

2

德赢Vwin官网

App

德赢Vwin官网

App

评论