为了更好地管理各类DDR3内存的特性,并提供一种简便的、带宽效率高的自动化方式来初始化和使用内存,我们需要一款高效DDR3内存控制器。

2021-02-09 10:08:00 10212

10212

2022年4月20日,中国苏州讯 —— 全球半导体存储解决方案领导厂商华邦电子今日宣布,将持续供应DDR3产品,为客户带来超高速的性能表现。 华邦的 1.35V DDR3 产品在 x8

2022-04-20 16:04:03 2554

2554

最近我在调试自制6657板子的DDR3初始化,发现一个很奇怪的现象,百思不得其解,我分别用GEL和KEYSTONE DDR3 INIT 在6657EVM开发板上做DDR3初始化,是没有问题的,我用

2019-01-08 10:19:00

进入或者离开自刷新。SDRFC中的REFRESH_RATE字段定义所接DDR3设备的刷新周期。它的计算公式为:REFRESH_RATE =DDR3CLKOUT frequency × memory

2018-01-18 22:04:33

的6678到芯片相应拐角的长度?还有就是不知道这个DQS_ECC和CK_ECC应该怎么看呢?下面是我通过表格计算出来的ddr3初始化的值。

ps:写个简单的测试程序,发现写不进去数,我知道这肯定是我配置有问题,但就是不知道该怎么进行查找,还请专家帮忙解答下,谢谢了

2018-06-21 17:25:42

嗨,我是FPGA领域的新手。现在我正在使用Genesys2。我必须控制DDR3内存。我在Digilent网站上找到了一些使用micrlaze处理器的DDR3示例。但是,在我的情况下,我不必

2019-05-05 15:29:38

在调试335x的DDR3时,用的是CCS,非操作系统调试。

按TI给的AM335x——StarterKit.gel,这个文件导入到CCS,debug的时候,DDR3可以驱动,读写正常。按

2018-06-21 10:59:20

1概述 当今计算机系统DDR3存储器技术已得到广泛应用,数据传输率一再被提升,现已高达1866Mbps.在这种高速总线条件下,要保证数据传输质量的可靠性和满足并行总线的时序要求,对设计实现提出

2014-12-15 14:17:46

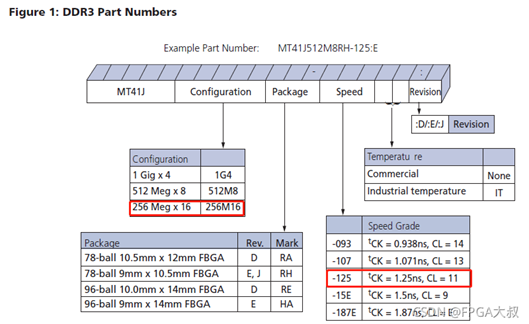

通过DDR3内存名MT41J128M16-16Meg*16*8Banks通过命名怎样算出内存的大小?

2017-06-15 21:19:11

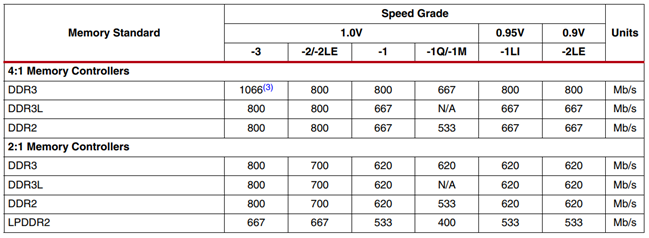

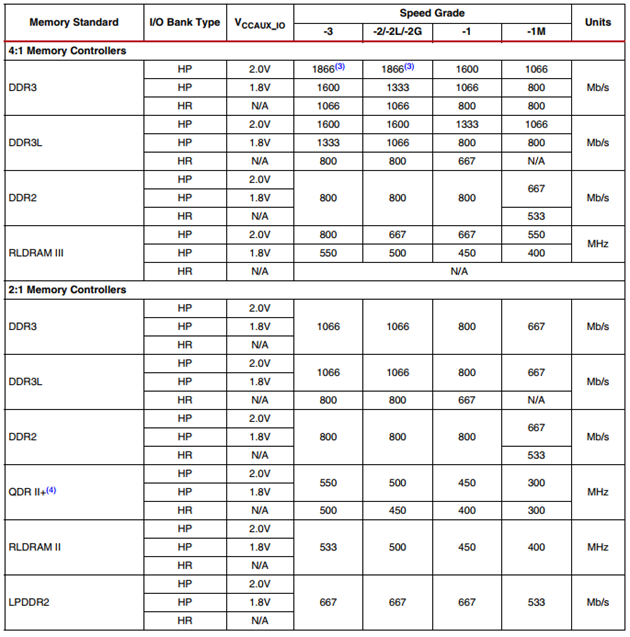

HI,我的FPGA是Kintex-7的XC7K410T-2FFG900。我的DDR3是2Gb,由128Mb * 16组成。 DDR3数据速率为1600Mbps,因此我必须在HP BANK中使用VRN

2020-07-21 14:47:06

DDR3(double-data-rate three synchronous dynamic random accessmemory)是应用在计算机及电子产品领域的一种高带宽并行数据总线。DDR3 在 DDR2

2019-05-22 08:36:26

DDR3基础详解最近在IMX6平台下做DDR3的测试接口开发,以前在学习嵌入式时,用的是官方源码,没有做过多的研究。此时需要仔细研究DDR3的引脚与时序,此篇是我在学习DDR3做的归纳与总结,其中有

2021-07-28 09:02:52

DDR3接口所需的特性。视频处理系统将对于数据带宽的要求推高到了极致:系统可以处理越多的数据,就具有越高的性价比。视频聚合器和路由器可并行处理多个视频流,因此对于匹配数据处理能力和视频带宽的需求就成为

2019-05-24 05:00:34

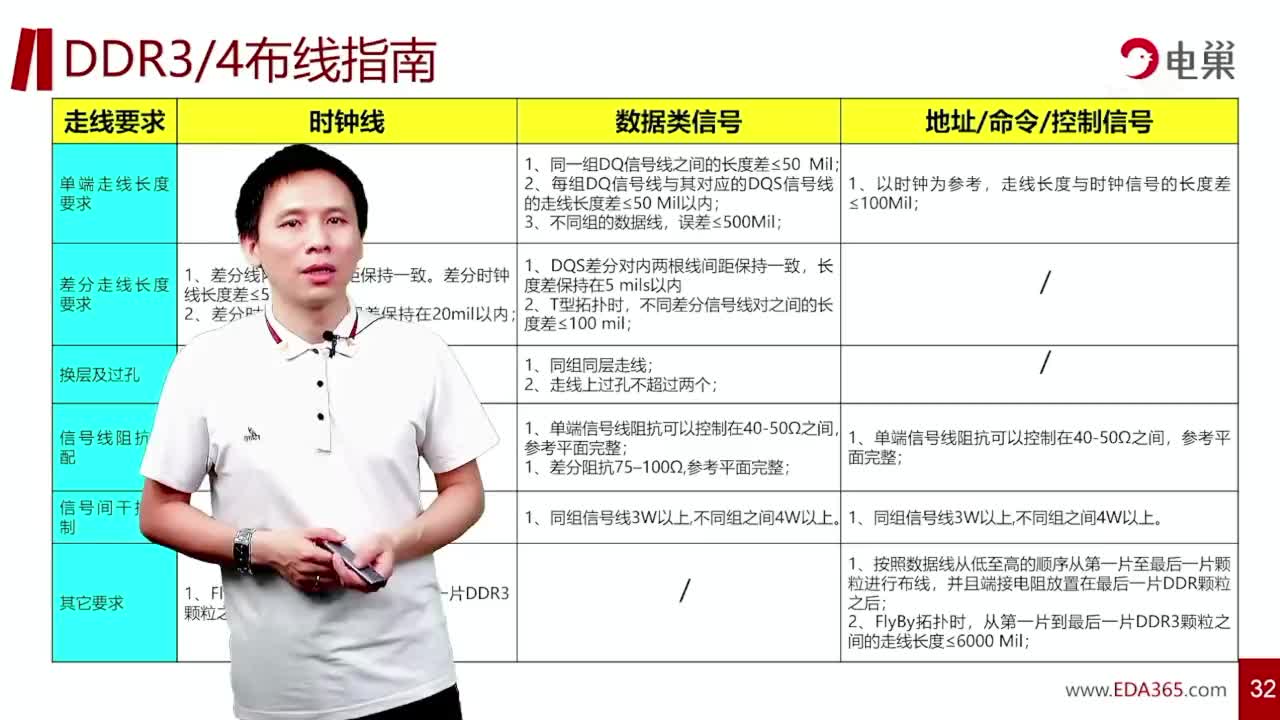

共享交流一下,DDR3布线技巧

2016-01-08 08:17:53

CPU的DDR3总线只连了一片DDR3,也没有复用总线将DDR3的CS直接拉到地的话,DDR3初始化不成功所以说DDR3的CS信号是通过沿采样的吗,电平采样不行?无法理解啊还是有其他方面原因

2016-11-25 09:41:36

本帖最后由 一只耳朵怪 于 2018-6-21 15:24 编辑

各位好!关于DDR3,之前有小结过如果进行DDR3的SW leveling和进行EMIF4寄存器的配置。但是调试时,如果进行DDR3的问题定位,现小结一下,附上相关文档。如有相关问题,可在楼下跟帖讨论。谢谢!

2018-06-21 04:01:01

专家,你好,想节省代码设计的周期,请问是否可以提供6670的DDR3的驱动例子?谢谢

2018-06-21 13:34:52

DDR4,DDR3,DDR2,DDR1及SDRAM有什么不同之处?

2021-03-12 06:22:08

BeagleBone的参考设计中,DDR3设计是DDR3 Device without VTT Termination。而其他的AM335X的参考设计都是有VTT Termination

2018-06-21 03:05:42

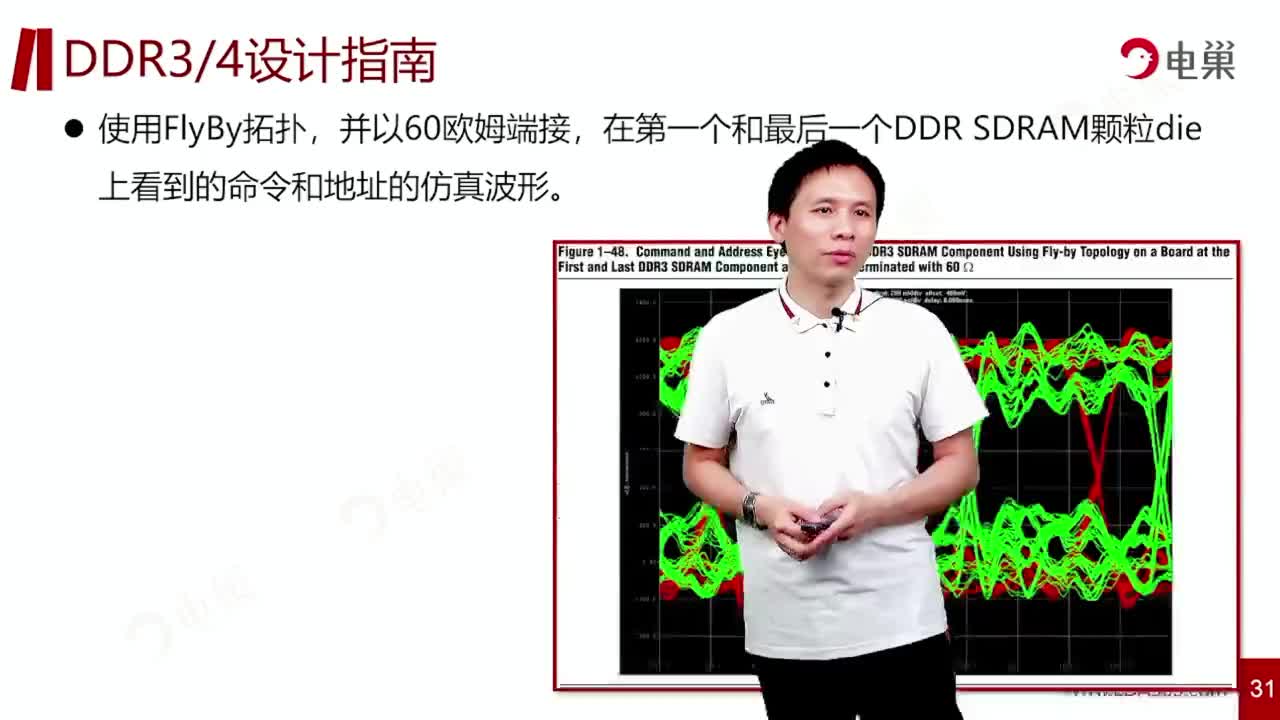

://pan.baidu.com/s/1s402 密码: 9362 播放密碼:QQ521122524以上为其中一节课程完整版视频内容:4顆DDR3拓撲講解4顆DDR3布局方法DDR3電氣規則設置等长设置DDR3信號分組等長原理DDR3等長設置DDR3电源处理DDR3布線繞線`

2014-12-17 21:16:37

视频内容:4顆DDR3拓撲講解4顆DDR3布局方法DDR3電氣規則設置等长设置DDR3信號分組等長原理DDR3等長設置DDR3电源处理DDR3布線繞線

2015-07-30 21:34:09

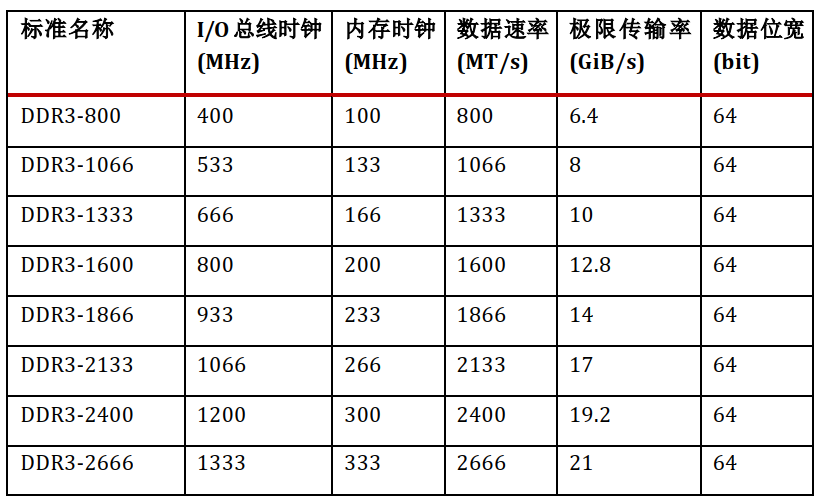

DDR3的理论带宽怎么计算?用xilinx的控制器输入时钟200M。fpga与DDR的接口如下:

2016-02-17 18:17:40

Gowin DDR3 Memory Interface IP 用户指南主要内容包括 IP 的结构与功能描述、端口说明、时序说明、配置调用、参考设计等,旨在帮助用户快速了解 Gowin DDR3 Memory Interface IP 的产品特性、特点及使用方法。

2022-10-08 08:10:13

本次发布 Gowin DDR3参考设计。Gowin DDR3 参考设计可在高云官网下载,参考设计可用于仿真,实例化加插用户设计后的总综合,总布局布线。

2022-10-08 08:00:34

请问LED灯的阻抗计算方法是什么?

2020-03-06 14:43:47

或者是通过TI官网UC3842手册上的方法学习Rstart的计算方法。

2021-10-29 07:04:40

Achieving High Performance DDR3 Data Rates in Virtex-7 and Kintex-7 FPGAs。Xilinx官方DDR3资料。

2016-05-27 16:39:58

DDR3的IP核配置完毕后,产生了好多文件,请问如何调用这些文件实现DDR3的读写呢?看了一些文章,说是要等到local_init_done为高电平后,才能进行读写操作。请问DDR3的控制命令如

2016-01-14 18:15:19

soc计算方法,BMS中的SOC的计算其实可以分为三大部分:1、电芯层级的SOC计算(软件中最真实的SOC计算,不涉及任何滤波处理);2、模组或者电池包层级的SOC计算(电芯到电池包级别的SOC映射

2021-07-27 06:13:05

看完保证你会做DDR3的仿真

2015-09-18 14:33:11

1、从工作平率上说:首先接口就全部不同 电压不同 频率的计算方法不同 SDR的频率就是外频 133=133 DDR的频率就是外频的2倍 133=266 DDR2的频率就是外频的4倍 133=533

2014-12-30 14:35:58

1、从工作平率上说:首先接口就全部不同 电压不同 频率的计算方法不同 SDR的频率就是外频 133=133 DDR的频率就是外频的2倍 133=266 DDR2的频率就是外频的4倍 133=533

2014-12-30 14:36:44

您好,

通过ddr init 文档和论坛上各种帖子, ddr3 leveling时要通过phy cal v10表格计算leveling寄存器的值。但是现在我们配置ddr

2018-06-21 17:05:46

嗨,我正在设计一个定制FPGA板&我将使用带有Kintex(XC7K160T-2FFG676C)FPGA的DDR3 RAM。我阅读了xilinx& amp; amp; amp

2020-04-17 07:54:29

仍不知道DDR3和DDR4这两种规格的区别,以至于买回来的硬件并不兼容。下面和宏旺半导体一起来看一下DDR3和DDR4到底有哪些差别。DDR3是一种计算机内存规格,它属于SDRAM家族的内存产品,提供

2019-07-25 14:08:13

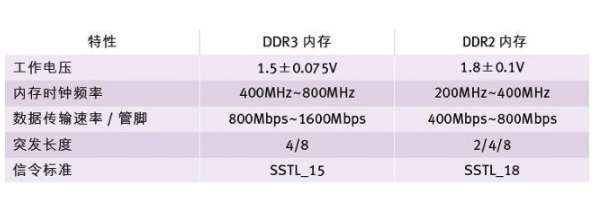

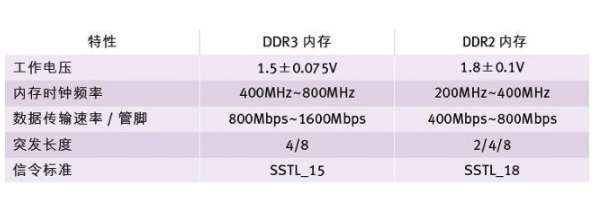

并不会注意一些数字上的差异,如DDR3和DDr2,或许大多数人都会追求时髦选择DDR3,但是你真的了解DDR2与DDR3的区别吗?作为消费者,其实我们可主宰自己的命运,用知识的武器捍卫自己的选择。下面

2011-12-13 11:29:47

1.项目的板子上要用到两颗DDR3芯片,板子打样回来可能要进行测试,对示波器的采样率可能会有比较高的要求,不知道大家在设计中用的是什么示波器,最好有具体型号2.既然说到DDR3了,有好些个问题都想

2017-10-26 09:54:13

的情况下计算出来呢,网上的资料我都看了,两个EXCEL工具也都使用了,都没有得到这个参数的计算方法,希望得到各位高手的帮助。还有一个就是PHY_WR_DATA,我在EXCEL工具中的DDR3选项中没找到

2018-05-15 05:49:26

自己画的6657的板,发现DDR3初始化有问题,初始化参数是按照芯片手册来设置的,写数据进去会出错。初步怀疑是DDR3布线问题,请问TI的大神们,6657对DDR3的布线有什么具体的要求吗?或者是

2018-06-21 05:42:03

DDR3接口所需的特性。视频处理系统将对于数据带宽的要求推高到了极致:系统可以处理越多的数据,就具有越高的性价比。视频聚合器和路由器可并行处理多个视频流,因此对于匹配数据处理能力和视频带宽的需求就成为

2019-05-27 05:00:02

进行了DDR3 SDRAM控制器的编写,分析并提出了提高带宽利用率的方法。最终将其进行类FIFO接口的封装,屏蔽掉了DDR3 IP核复杂的用户接口,为DDR3数据流缓存的实现提供便利。系统测试表明,该

2018-08-02 09:34:58

设计,完成了对单片DDR3内存条的多通道实时访问控制需求。通过ChipScope工具采样结果证明了设计的可行性,提高了并行处理的速度,极大程度地降低了期货行情数据处理中行情计算的时间开销,最高通道速率可达

2018-08-02 09:32:45

12位,扩展成16位后进行存储,DDR3内部以1067M处理速度,32位的处理带宽进行存储,写数据时从地址全0写到地址全1,读数据时也从地址全0读到全1,经对比无误,说明该控制器能够较好地进行高速读写操作。`

2018-08-30 09:59:01

本手册以 DDR3 器件为例讲解硬件设计方法,包括 FPGA I/O 分配、原理图设计、电源网络设计、PCB 走线、参考平面设计、仿真等,旨在协助用户快速完成信号完整性好、低功耗、低噪声的高速存储

2022-09-29 06:15:25

大量收购现代DDR3长期回收现代ddr3,高价收购现代DDR3.大量求购现代DDR3.深圳帝欧专业电子回收,帝欧赵生***QQ1816233102/879821252邮箱dealic@163.com

2021-10-13 19:18:05

的话总的带宽就不够。burst length太小,整体的带宽利用率就更悲催了。请问各位前辈有没有什么好的方法能够在这种应用用最大化的利用DDR3的带宽?

2015-08-27 14:47:57

大家好,我在DDR3规格中发现JEDEC79-3E定义VOH(DC)是DC输出高测量级别(用于IV曲线线性)。但是没有关于如何测量高输出直流输出的指南,特别是当信号在高电压时有环时,请参见附图。谁能

2019-04-17 13:59:13

由于系统带宽不断的增加,因此针对更高的速度和性能,设计人员对存储技术进行了优化。下一代双数据速率(DDR)SDRAM芯片是DDR3 SDRAM。 DDR3 SDRAM具有比DDR2更多的优势。这些

2019-08-09 07:42:01

自建Spartan6 DDR3仿真平台

2019-08-01 06:08:47

怎样对DDR3芯片进行读写控制呢?如何对DDR3芯片进行调试?

2021-08-12 06:26:33

电机转子运动惯量的计算方法哪些,如何避免转子惯性失配?

2021-02-02 07:25:12

、自己写了一个算法,想验证算法的计算速度,请问DDR3影响这个算法的运行速度吗?3、DDR3和外接Flash有什么区别和联系。非常期待各位专家的解答。谢谢大家!

2018-06-20 00:40:57

请问伺服电机的选型计算方法是什么?

2021-09-28 08:45:32

使用MCSDK提供的norwriter_evm6678l例程,按照论坛上提供的方法,进行程序烧写。而该例程的CCS启动用到DDR3,需要使用gel文件,对DDR3做初始化。因此自己尝试去修改gel中DDR3

2018-08-06 07:33:54

阻抗计算方法,希望有所帮助

2013-06-10 16:58:32

本文介绍了DDR3 SDRAM 的基本特点和主要操作时序,给出了一种基于ALTMEMPHY宏功能的DDR3 SDRAM控制器的设计方法。详述了控制器基本结构和设计思想,分析了各模块功能与设计注意事项,并

2010-07-30 17:13:55 30

30 不只计算机存储器系统一直需要更大、更快、功率更低、物理尺寸更小的存储器,嵌入式系统应用也有类似的要求。本应用指南介绍了逻辑分析仪在检验DDR, DDR2 和DDR3 SDRAM 命令和

2010-08-06 08:29:49 79

79 AGP、PCI-E总线带宽的计算方法

总线是一组进行互连和传输信息(指令、数据和地址)的信号线。主要参数有总线位宽、总线时钟频率和总线传输速率。

※总

2009-05-09 08:42:41 2953

2953 Quamtum-SI DDR3仿真解析

Automated DDR3 Analysis

2010-04-29 09:00:11 4257

4257

本文得出了互阻放大器的带宽计算方法,为互阻放大器提供了基本指导。在满足式(18)的条件下,互阻放大器的增益与带宽的平方乘积近似为一常数。在电路设计时,为了满足带宽的设计

2011-07-11 11:37:10 7285

7285

总结了DDR和DDR2,DDR3三者的区别,对于初学者有很大的帮助

2015-11-10 17:05:37 36

36 甲类单端的简易计算方法甲类单端的简易计算方法甲类单端的简易计算方法

2016-01-19 15:37:38 0

0 DDR3是目前DDR的主流产品,DDR3的读写分离作为DDR最基本也是最常用的部分,本文主要阐述DDR3读写分离的方法。最开始的DDR, 芯片采用的是TSOP封装,管脚露在芯片两侧的,测试起来相当方便;但是,DDRII和III就不一样了,

2017-11-06 13:44:10 8454

8454

DDR4提供比DDR3/ DDR2更低的供电电压1.2V以及更高的带宽,DDR4的传输速率目前可达2133~3200MT/s。DDR4 新增了4 个Bank Group 数据组的设计,各个Bank

2017-11-07 10:48:51 52790

52790

虽然新一代电脑/智能手机用上了DDR4内存,但以往的产品大多还是用的DDR3内存,因此DDR3依旧是主流,DDR4今后将逐渐取代DDR3,成为新的主流,下面我们再来看看DDR4和DDR3内存都有哪些区别。相比上一代DDR3,新一代DDR4内存主要有以下几项核心改变:

2017-11-08 15:42:23 30895

30895 为解决超高速采集系统中的数据缓存问题,文中基于Xilinx Kintex-7 FPGA MIG_v1.9 IP核进行了DDR3 SDRAM控制器的编写,分析并提出了提高带宽利用率的方法。最终将其进行

2017-11-16 14:36:41 19504

19504

SDRAM):DDR4提供比DDR3/ DDR2更低的供电电压1.2V以及更高的带宽,DDR4的传输速率目前可达2133~3200 MT/s。

2017-11-17 13:15:49 25152

25152 我们通过Configuration,Package,Speed...等DDR3的命名可知道DDR3的容量,封装,速度等级等信息。

2019-03-03 11:04:15 1909

1909

DDR3内存与DDR2内存相似包含控制器和存储器2个部分,都采用源同步时序,即选通信号(时钟)不是独立的时钟源发送,而是由驱动芯片发送。它比DR2有更高的数据传输率,最高可达1866Mbps;DDR3还采用8位预取技术,明显提高了存储带宽;其工作电压为1.5V,保证相同频率下功耗更低。

2019-06-25 15:49:23 1736

1736 本文档的主要内容详细介绍的是DDR和DDR2与DDR3的设计资料总结包括了:一、DDR的布线分析与设计,二、DDR电路的信号完整性,三、DDR Layout Guide,四、DDR设计建议,六、DDR design checklist,七、DDR信号完整性

2020-05-29 08:00:00 0

0 从成本的角度来看,DDR3也许的确要比DDR4低一些,所以从这个角度可以讲通。

2020-09-08 16:28:23 4062

4062 DDR4相比DDR3的相关变更点相比DDR3,DDR4存在诸多变更点,其中与硬件设计直接相关的变更点主要有: 增加Vpp电源; VREFDQ删除; CMD、ADD、CTRL命令的端接变更为

2021-11-06 20:36:00 28

28 沿和下降沿都发生数据传输。 图1. DDR3结构 二、地址的概念及容量计算 2.1地址的概念 DDR3的内部是一个存储阵列,将数据“填

2022-12-21 18:30:05 1915

1915 EMC计算方法概述2021/11/16大家好!我是ROHM的稻垣。本文是第16篇,从本文开始我们来谈一谈电磁兼容性(EMC)的计算方法和仿真。

2023-02-14 09:26:28 2228

2228 本文介绍一个FPGA开源项目:DDR3读写。该工程基于MIG控制器IP核对FPGA DDR3实现读写操作。

2023-09-01 16:23:19 745

745

DDR3带宽计算之前,先弄清楚以下内存指标。

2023-09-15 14:49:46 2508

2508

DDR3是2007年推出的,预计2022年DDR3的市场份额将降至8%或以下。但原理都是一样的,DDR3的读写分离作为DDR最基本也是最常用的部分,本文主要阐述DDR3读写分离的方法。

2023-10-18 16:03:56 518

518

DDR4和DDR3内存都有哪些区别? 随着计算机的日益发展,内存也越来越重要。DDR3和DDR4是两种用于计算机内存的标准。随着DDR4内存的逐渐普及,更多的人开始对两者有了更多的关注。 DDR3

2023-10-30 09:22:00 3905

3905 EMC计算方法和EMC仿真(1) ——计算方法简介

2023-12-05 14:56:08 384

384

德赢Vwin官网

App

德赢Vwin官网

App

评论