在日前举办的2017年Q4法说会上,台积电透露,其极紫外光光刻机(extreme ultraviolet lithography: ,简称EUV光刻机)产能已经取得了较大的进步,目前已经将其电源功率提高到160W,助力7nm和5nm制造,而250瓦EUV也已经安装到位。

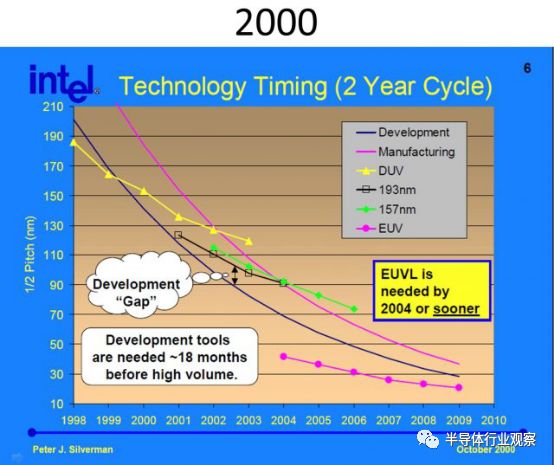

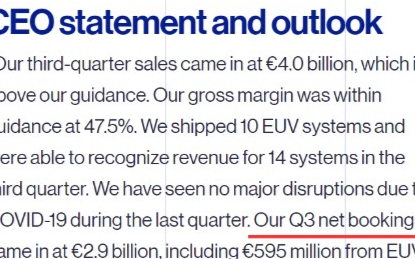

EUV光刻机的唯一供应商ASML在2017年度Semicon West半导体设备展上也表示,250瓦的EUV光源也万事俱备。公司2017年财报中也强调,其EUV光刻机满足了125WPH(每小时生产125片晶圆)的性能规格。那就意味着最初计划在2004年推出的EUV光刻机,在延误了十三年之后,终于准备好了。

EUV光刻机被誉为救世主,关键问题已解决

过去几十年,半导体产业在摩尔定律的指导下获得了高速的发展,为了满足摩尔定律“同等面积芯片集成的晶体管数每18个月翻一番”的要求,晶圆厂一直在推动工艺制程的更新。但随着节点的演进,产业界普遍认为传统的光刻将会在65nm或者45nm的时候遭受到障碍,为此他们寻找新的解决办法,EUV就是他们的主要选择。

所谓EUV,是指波长为13.5nm的光。相比于现在主流光刻机用的193nm光源,新的EUV光源能给硅片刻下更小的沟道,从而能实现在芯片上集成更多的晶体管,进而提高芯片性能,继续延续摩尔定律。不过在之前推进EUV光刻机的过程中,碰到各种各种各样的问题,EUV光刻机商用的时间也一拖再拖,业界在EUV的研发投入保守估计也超过了200亿美金,发光源功率是造成EUV光刻机迟迟不能商用的最主要原因。

在EUV光刻机工作过程中,需要电源将等离子体转换成13.5nm波长的光线,之后再经过镜子的几重反射,再打落到晶圆上。但是之前的电源并不能给EUV提供足够的功率,进而满足经济可行性。这就首先要了解对EUV光刻机的要求:

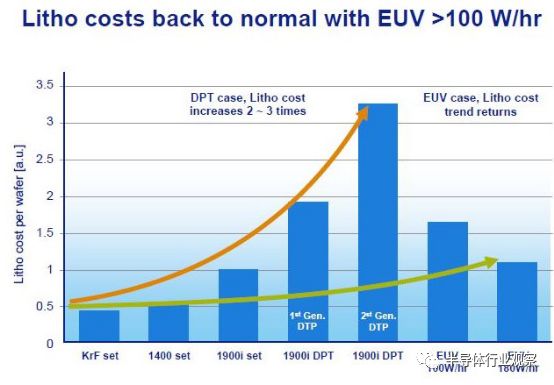

简单来说,引入EUV光刻机的工作目标,就是把原来传统光刻的双层pattering简化成一层EUV完成,进而降低光罩的层数,降低生产复杂度。而为了达到现有的传统光刻机250到270WPH的生产效率,那么来到EUV光刻机,那么至少需要125WPH的效率,才能达到COO(cost of ownership)和OEE(overall equipment efficiency),这就对光源提出250瓦的要求。但知道2012年,EUV光刻机的唯一供应商ASML只是实现了25瓦的光源。

为了加速光源的发展,他们在2012年斥资25亿美元收购了世界领先的准分子激光源提供商Cymer。从全球领先的专利查询平台智慧芽上了解到, Cymer是一家专注于激光、X射线及深紫外光源的企业。收购Cymer,让ASML直接从源头上获得了其发展中至关重要的光刻机光源技术。进而加速了EUV光刻机的发展。

据介绍,Cymer 使用了一种叫做“激光等离子体”的方法,这种方法是在一个真空腔体中,用源自金属切割技术的放大器,产生强大的二氧化碳激光,通过腔体,照射一束每秒被发射出5万滴的超纯锡液滴。当激光脉冲照射到锡液滴时,液滴会被加热成等离子体并产生EUV射线。接着,一个反射镜收集器将该过程产生的光线反射到光刻机中。

在这个方法的基础上,ASML和Cymer持续改进,并在2016年达到200瓦的功率,到2017年下半年,终于实现了250瓦的光源和125WPH的效率,那就意味着EUV光刻机的商用指日可待。

随着HPC和智能手机的发展,对芯片性能的要求越来越高,设计厂商对先进工艺的需求也随之高涨,在台积电Q4法说会,台积电表示已经有了50个7nm客户,就是最好的证明。面对这个市场,正如文章开头所说,晶圆代工厂们需要将目光投向EUV光刻机寻求帮助。2017年5月刚从三星集团独立出来的三星晶圆厂就是当中最为激进的一个。

三星方面表示,他们是业内最早宣布将会使用EUV光刻机进行7nm芯片生产的厂商。按照三星的说法,他们将会在2018年下半年提供相关服务;至于TSMC,根据供应链相关人士透露,台积电将会在二季度末开始上马7nm生产,但是第一代7nm将会使用传统光刻。台积电方面表示,要到2019年的7nm plus才会引入EUV;格芯也同样打算在2018年推出7nm工艺,但是和台积电一样,这时还是用传统光刻,他们计划到2019年才引入EUV。至于IDM巨头Intel,他们对其先进工艺和EUV的进展秘而不谈,但是据公开消息显示,他们所购买的EUV光刻机比任何其他公司都多。

EUV光刻机无疑是未来的大势所趋。

格芯首席技术官Gary Patton表示,如果在5nm的时候没有使用EUV光刻机,那么光刻的步骤将会超过100步,这会让人疯狂。所以所EUV光刻机无疑是未来5nm和3nm芯片的最重要生产工具,未来围绕EUV光刻机的争夺战将会变得异常激烈。因为这是决定这些厂商未来在先进工艺市场竞争的关键。

媒体报道,台积电在2017年初一口气订购了五台EUV光刻机;韩媒BusinessKorea在十月也表示,三星有意购买10台EUV光刻机。关于格芯和Intel光刻机的具体购买数目没有看到报道。但从S和T两家看来,他们正在大手笔囤货。但是ASML在EUV光刻机上面的产能不大,这可能会加剧了争夺。

据ASML的年报得知,2016年,他们总共才出货了四台EUV光刻机,2017年则交付了10套EUV系统。而从媒体报道中我们得知,2018年,ASML的EUV光刻机产量可以达到24台,但这些订单都已经被抢购一空。但到2019年,ASML会将其产能提高到40台,这会大大缓解EUV光刻机的供应压力。

更大的挑战扔在后头

在基本克服了250W光源这个难题之后,ASML对晶圆厂客户有了一个基本的交代,但是对于EUV光刻机系统来说,仍然有一些问题需要被解决的。

首先就是光罩问题;

据介绍,EUV所用的光罩和193nm浸没式光刻的光罩完全不同,它们由使用了数十种不同材料的纳米层组成。根据数据调查显示,过去12个月来,光罩制造商已经制作了1041个EUV光罩,光罩良率目前仅为64.3%。但同期间曝光的主流的光罩数达到46万2792个,平均良率高达94.8%。因此如何提升光罩良率和成本问题,就成为他们考虑的首要问题。

其次EUV薄膜问题也不能忽略;

虽然现在EUV设备都是处于超洁净环境中,但是在制造过程中,灰尘是无可避免地产生的。如果有一点回城掉到光罩上,则会造成很大的损失。现在主流光罩的薄膜是透明的,能够经受得起考验,但是目前的EUV薄膜是不透明的,那就需要超薄型的薄膜去制造透明的EUV薄膜,能够抵挡EUV光刻机的震荡和相关干扰对光罩造成的影响。

还有一个重要的问题是目前没有很好的方法去检测光罩的缺陷;

理想情况下,你可以用EUV光去扫描那些需要修补的点。但这个被称为actinic patterned-mask inspection的技术依然还在研究当中,所以所有的芯片制造商目前在光罩检测上也只能用权宜之计:有些厂商使用193nm光刻的那些工具。但是来到7nm,用193nm的方法无异于缘木求鱼。因为方法虽然相同,但是你总会错过一些东西。芯片制造商也使用一个叫做“print check”的技术去检查晶圆,但这个方法在时间和金钱成本都很高,并不能让人接受。

对ASML来说,未来还需要解决一个光源问题。

目前的250W光源应用在7nm甚至5nm都是没问题的,但到了3nm,对光源的功率需求将会达到500W,到了1nm的时候,光源功率要求甚至达到了1KW,这也不会是一个容易的问题。

-

放大器

+关注

关注

143文章

13583浏览量

213364 -

等离子

+关注

关注

2文章

236浏览量

29926 -

EUV

+关注

关注

8文章

605浏览量

86004

发布评论请先 登录

相关推荐

关于EUV光刻机的分析介绍

关于EUV光刻机的分析介绍

评论