大家好,又到了学习时间了,学习使人快乐。今天我们来简单的聊一聊以太网,以太网在FPGA学习中属于比较高级的内容了,有些同学肯定会感觉以太网学习起来非常不容易。其实,我可以告诉大家,前期学习的基础打扎实了,后期的学习也没那么难。总之就是说难没那么难,说容易也不是那么容易。那么,言归正传,下面让我们一起来聊一聊以太网的学习。

说起以太网,大家可能就会想到百兆以太网、千兆以太网以及万兆以太网等等。局域以太网从10M开始发展,经历几多的变迁,发展到现在的千兆以太网。千兆以太网以高效、高速、高性能为特点,已经广泛应用在金融、商业、教育、政府机关及厂矿企业等行业。吉比特以太网,或译千兆以太网是一个描述各种以吉比特每秒速率进行以太网帧传输技术的术语,由IEEE 802.3-2005标准定义。该标准允许通过集线器连接的半双工千兆连接,但是在市场上利用交换机的全双工连接所达到的速度才真正符合标准。

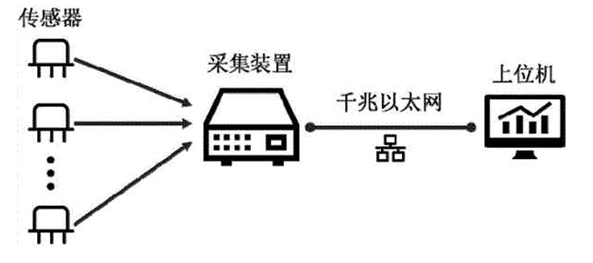

当今,随着互联网技术的迅速发展,采用以太网实现数据采集和控制方面的应用,成为了电子系统设计的热点。以太网具有价格低廉、稳定可靠、传输速度快、传输距离远等特点,以太网技术发展成熟,具有很高的性价比。采用以太网技术的设备,可以通过TCP/IP协议进行数据的传输,不需要进行传输协议转换,使用和维护设备简单。随着技术的发展和各类应用的需求,出现了各种以太网的标准,包括标准以太网(10Mbit/s)、百兆以太网(100Mbit/s)、千兆以太网(1000Mbit/s)和10G(10Gbit/s)以太网[1]。不同类型的以太网有其各自需要遵循的标准,同时其所用的传输介质以及数据吞吐量也各不相同。千兆以太网技术作为新一代的高速以太网技术,它可以提供1Gbps的通信带宽,采用和传统10M、100M以太网同样的CSMA/CD协议、帧格式和帧长、全/半双工工作方式、流控模式以及布线系统,给用户带来了提高核心网络的有效解决方案,这种解决方案的最大优点是继承了传统以太网技术价格便宜的特点。

对于学习者而言,你就是要搞清楚弄明白以太网如何去实现,在实际操作中怎么去做,从这个角度出发的话,你就会发现其实没那么复杂,这就是说起来没那么难。那真正实现起来,到具体的各个接口以及细节的调试以及调通,你会发现还是比较烧脑的。所以呢,咱们先来聊一聊以太网的各个接口,从大体框架来分析如何去学习。

咱们就以千兆以太网举例,千兆以太网,只是说以太网的速率为千兆,也就是1G。除了千兆网,还有百兆网,万兆网,当然这些都是指的以太网的速率。不同速率的以太网,在FPGA端的接口表现形式也是不一样的。下边就来介绍百兆网和千兆网的接口形式。

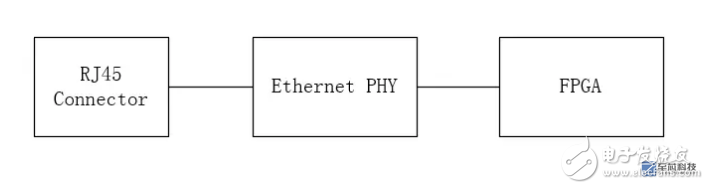

这是网口与FPGA连接的常用方案,RJ45就是咱们平常说的水晶头,Ethernet PHY是以太网的PHY芯片,之后就是Ethernet PHY与FPGA相连。

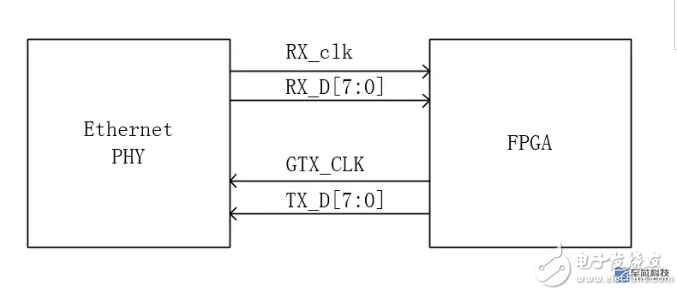

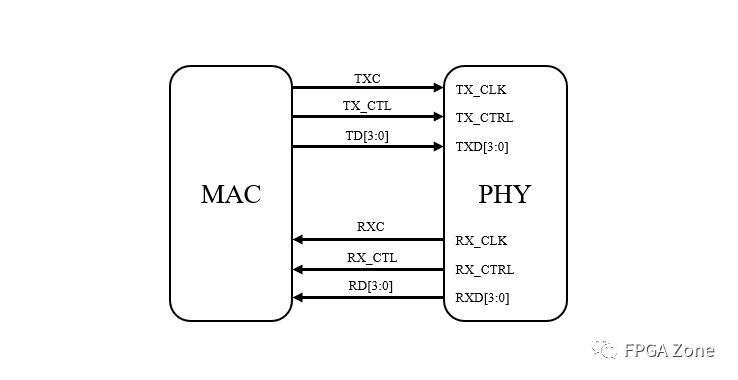

下边是以太网PHY芯片与FPGA连接的简单的架构图(不代表全部的信号输入输出端口)

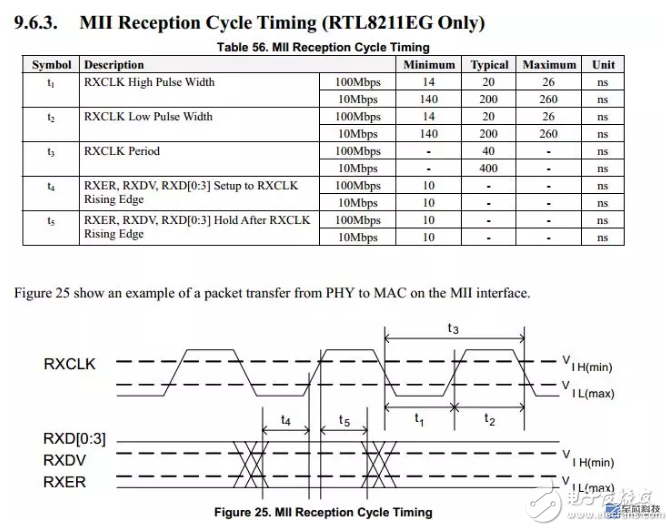

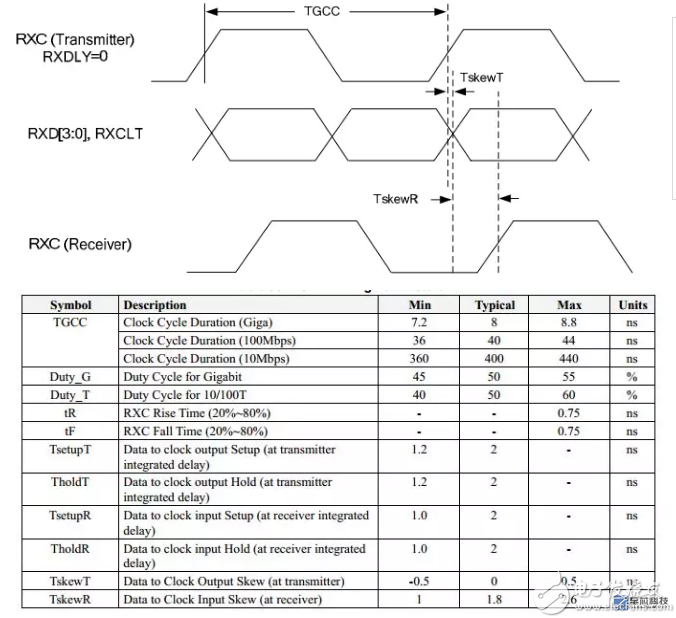

先说百兆网,百兆网的接口一般为MII(Media Independent Interface),当然10M网用的也是MII接口。下图是一块以太网PHY芯片的一些手册资料截图。

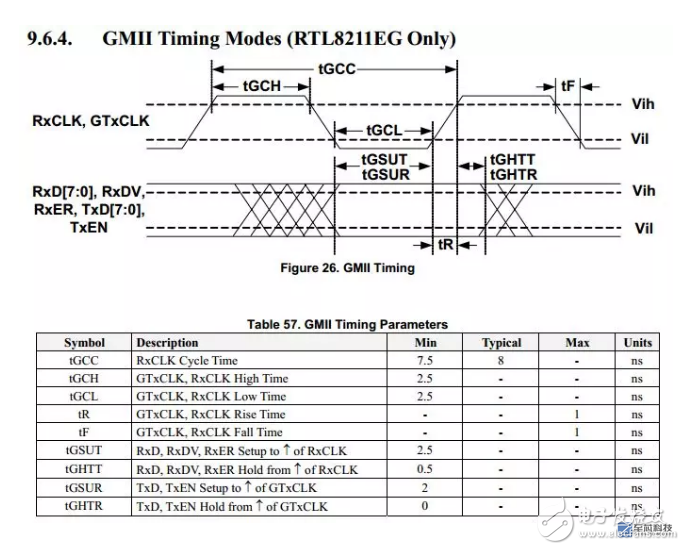

在百兆网模式下,其RXCLK的周期为40ns,也就是25M,数据端口RXD只用了4根线RXD[3:0],然后25M*4 = 100M,这样算出来,就是100M的速率了。接着再来说一下千兆网,千兆网的接口,就目前接触比较多的接口有3种,GMII,RGMII和SGMII。先说GMII,RxClk的周期为8ns,也就是125M,数据端口使用了8bit,125M*8 = 1000M,速率就是千兆网了。

还有RGMII,其时钟频率也为125M,但是它只使用了4个线,不过,RGMII使用的是双沿模式,也就是DDR模式,在时钟的上下沿都可以传送数据。这样算的话,125M*4*2 = 1000M,还是千兆网。RGMII与GMII主要的区别就是双沿采样与单沿采样。

之后还有SGMII,全称为Serial Gigabit Media Independent Interface,也就是串行的以太网接口。RGMII,GMII还是MII,都是使用并行接口,而且还需要随路时钟,而SGMII只需要2组线,一组是发送,一组是接收,当然一组线由两根差分线组成。SGMII也是需要8/10B编码。这样在PCB布线时,就可以节省一些布线的空间。当然,对于FPGA来讲,也节省了FPGA的引脚资源。SGMII一般在公司的项目会用的多一些,像GMII,RGMI在某宝上卖的开发板上一般都有。

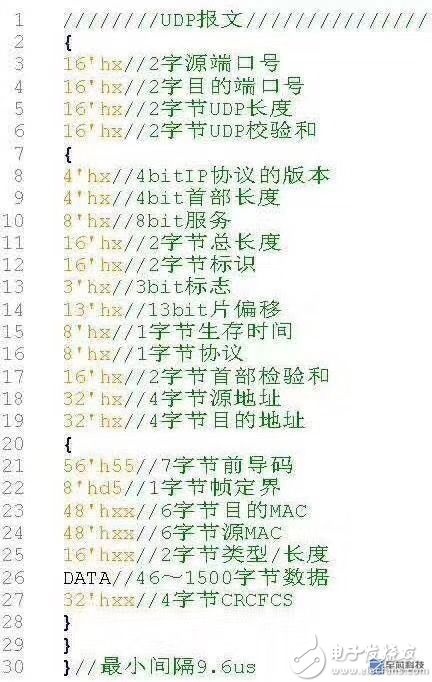

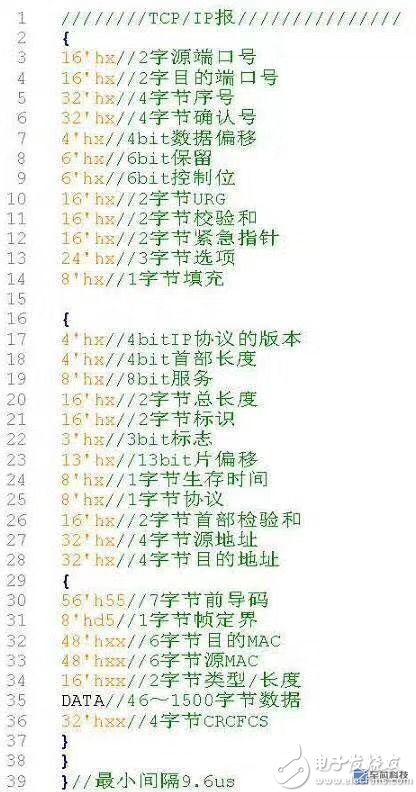

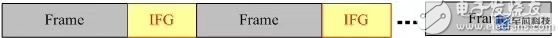

下面就简单的说说以太网数据格式,IEEE.802.3数据格式汇总,帧间隙IFG>=96bittime,10zM/100M/1000M格式一样。如下图简单的端口信号显示截图。

上面介绍了那么多接口以及以太网的相关知识,那么问题来了,如何去快速学习千兆以太网呢?个人认为掌握好总体框架以及接口细节,理解UDP协议,掌握抓包等等,慢慢琢磨学习,大家都可以慢慢掌握好的。那么下面咱们就来聊聊千兆以太网的UDP协议,并且会结合wireshark抓包软件抓取到的以太网包,带着大家看一下以太网的协议到底是怎么样的呢?当然,像我们常用的以太网协议有TCP/IP,UDPTCP/IP和UDP相比,TCP/IP是一种数据可靠的协议,而UDP是一种数据不可靠的协议。至于为什么TCP/IP是可靠的,而UDP是不可靠,留给大家自行百度。在wireshark中可以抓取到经过网口传输的很多数据包,可以说只要是经过网口的数据,在wireshark中都能抓到。大家可以去下载一个WireShark来学习一下吧,免费下载使用哦!(备注:网络协议分析器 WireShark是一款开源的网络数据帧分析软件,可以抓取网络数据封包,提供每个数据帧的详细信息,如MAC地址、数据帧类型、IP地址、UDP端口、等重要信息,方便开发者对网络数据协议的分析与相关测试。WireShark官网:https://www.wireshark.org/)

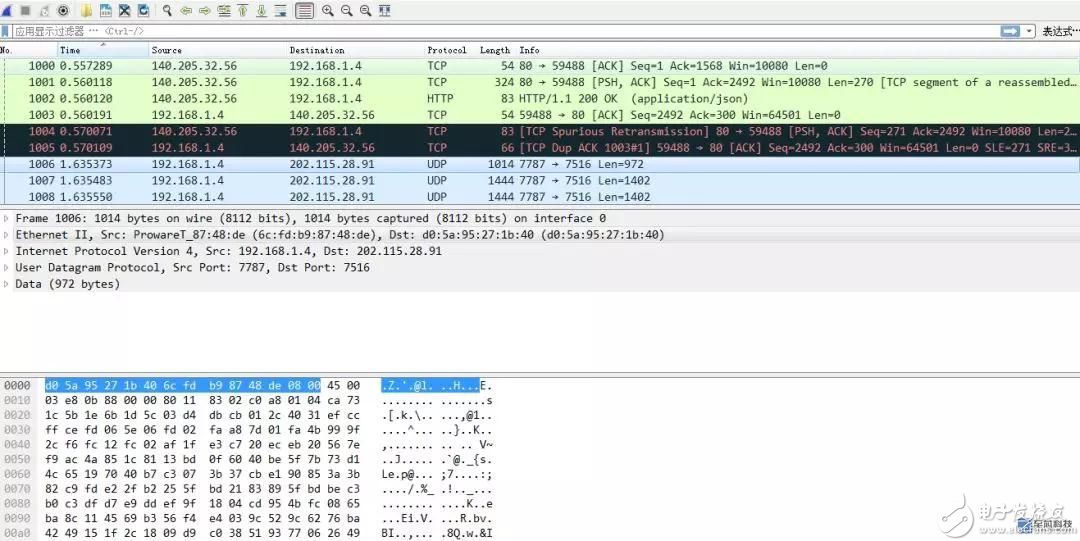

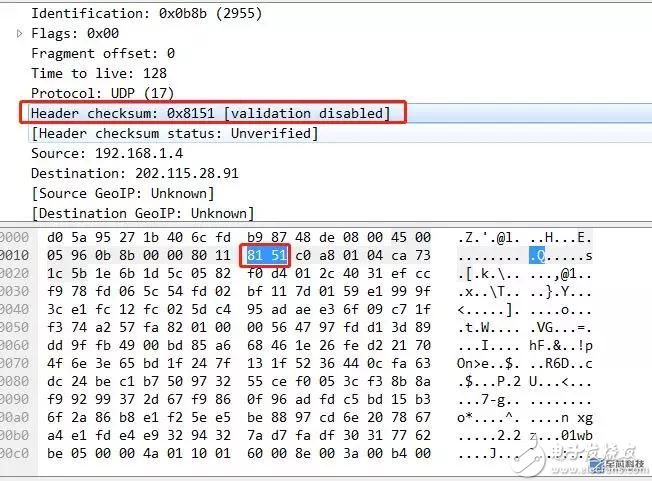

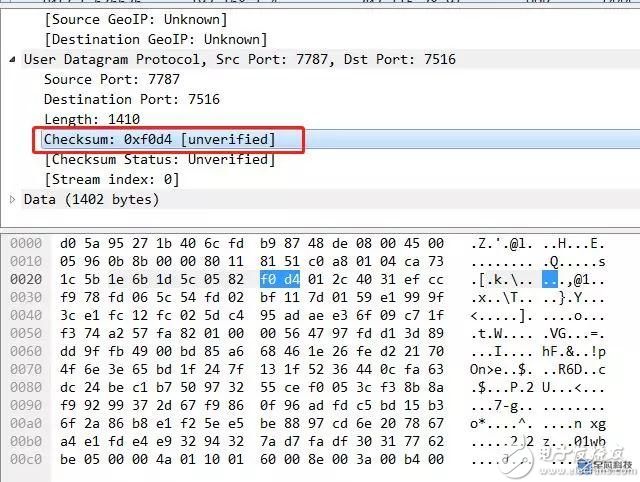

下面我们根据抓取到的一个UDP包,来给大家介绍UDP的协议

第一部分,可以粗略的知道该UDP包,其源IP和目的IP到底是什么。

第二部分,是对该UDP包的简短描述,从中可以大约的知道该数据包的数据长度,源MAC地址,目的MAC地址,等等相关信息。

第三部分,可以说是这个包的所有数据。一个完整的数据包,还会有数据包的帧头,帧尾还有CRC校验的数据。

看到第三部分,这全是十六进制的字符,这TMD的到底是什么意思呢?

关于这些内容,点开第二部分的展开图标,就可以一探究竟了。

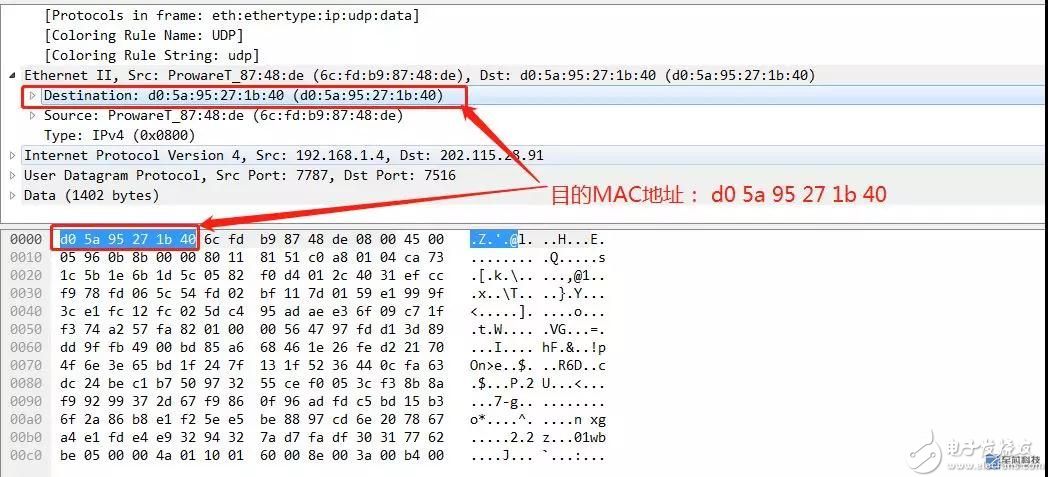

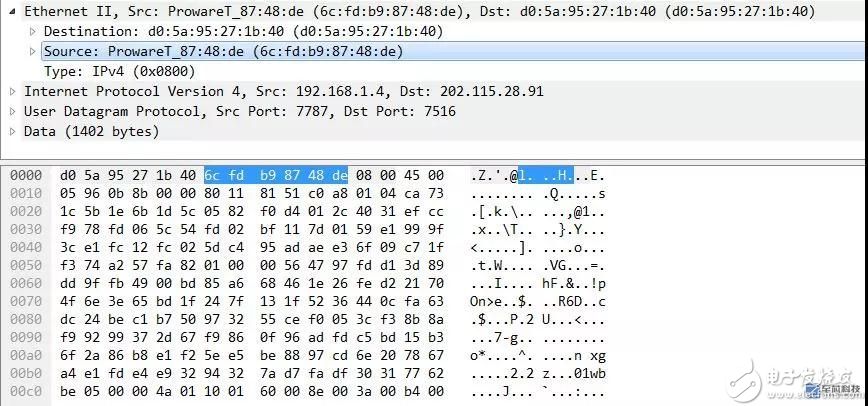

这样看,是不是就可以知道这个UDP包的前6个字节,就是目的MAC地址了呢?再来看接着的6个字节数据:6c fd b9 87 48 de

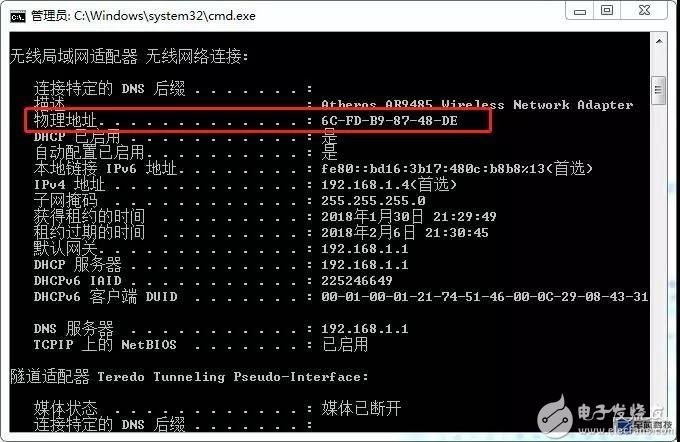

这6个字节,代表着源MAC地址。我们也可以通过查看自己电脑上的MAC地址来确认。

接着的这些数据,大家也可以自己跟着文章中的讲解,自己下载一个WireShark来学习一下。

当然,这里特别需要说明的一下是,UDP协议涉及到校验和的计算。总共有两个校验和,一个是在IP首部的校验和,另一个是在UDP首部的校验和。

-

FPGA

+关注

关注

1629文章

21729浏览量

602953

发布评论请先 登录

相关推荐

基于Xilinx FPGA的千兆以太网控制器的开发

基于FPGA的十端口千兆以太网接口的设计与实现

基于Xilinx FPGA的嵌入式串行千兆以太网设计

基于FPGA的UDP RGMII千兆以太网通信方案

简谈基于FPGA的千兆以太网

简谈基于FPGA的千兆以太网

评论