所有电子电路通常使用电感元件,如变压器,线圈或继电器,某些应用,如步进电机,也有感应负载。不幸的是,感应电路中的开关装置的故障是常见的问题并且导致系统故障。开关晶体管和MOSFET故障在电机驱动器,开关模式电源和类似电子系统中很常见。切换失败的原因可能是内在的或外在的。在内在故障中,设备本身可能有故障,可能已经发生降级,或者它可能具有初始设备测试未检测到的潜在缺陷。外部故障原因包括在系统正常运行期间误操作设备或使其超出其安全操作区域特性。在这种情况下,设备必然会因过度的压力而失效。应力可以是电气(图1)或热过应力。

最小化电感电路中的开关设备故障采用多管齐下的方法。首先,在电路中实现变压器和其他电感元件的良好设计和构造技术,以减少寄生效应,如漏电感和寄生电容。其次,在开关设备上放置保护网络或设备,以防止高压击穿。第三,使用适当的开关器件,其击穿电压额定值适合电路中的预期电压电平。您应该将数据手册指定的击穿电压额定值降低约75%。您应该为所有变压器指定可接受的漏感电平,并在进线检查期间拒绝不符合规格的变压器,以便此类有缺陷的元件不会导致现场故障。由于任何系统的可靠性取决于系统中每个组件的可靠性,因此注意变压器和开关设备的次要参数细节可以通过减少组件故障大大提高整体系统可靠性。

V CE 故障导致大多数故障

V CE 故障是导致故障的主要原因具有感性负载的电路中的半导体器件。出现这种故障存在各种原因。只要晶体管的集电极 - 发射极端子上的电压超过其额定值,器件就可能发生故障。虽然设计人员根据应用要求选择器件,但电路中预期的电压偏移可能在V CE 额定值范围内,但电路中的其他元件可能会导致V CE 电压超过器件的最大限值。

考虑一个基本的晶体管电路,其中晶体管充当开关,转动一个电机绕组开关(图2a)。在该电路中,感应电动机绕组中的电流的切换使开关装置Q受到应力。由于Ldi/dt电压产生应力,由于快速开关动作,通过电动机绕组的电流突然变化。该应力以电压的形式表现出来,电路在晶体管的集电极 - 发射极端子上施加电压。如果晶体管的集电极 - 发射极端子上的电压幅度超过其V CE 额定值,则晶体管的集电极 - 发射极结的高压击穿发生。您不能将为V CE 指定的完整额定值或任何其他参数应用于晶体管。您必须根据应用的可靠性要求和工作温度降低指定的额定值。通常,您应该将V CE 评级降低75%。因此,如果根据数据手册规范,晶体管的额定电流在其集电极和发射极端子之间的最大电压为100V,则其V CE 额定值仅为75V。在任何应用中,该晶体管的V CE 不应超过75V。在系统正常运行期间集电极 - 发射极端子之间的施加电压越低,系统的可靠性越好。

确保系统可靠性的第一种方法是选择具有足够的额定电压容差的开关器件,尤其是V CE 击穿电压,取决于应用要求。然后,对V CE 应用适当的降额,例如75%。您还可以通过在电感负载(图2a)上连接二极管来保护感性负载电路中的晶体管免受V CE 击穿,并将齐纳二极管连接到晶体管的集电极 - 发射极端子(图2b),或者通过开关器件连接缓冲网络(图2c)。

在图2a中,二极管D提供晶体管关闭时的电流路径这样衰减的电流反馈到电源,Ldi/dt尖峰不会在集电极 - 发射极端子上产生应力。这个所谓的续流二极管为开关关闭时的衰减感应电流提供了自由路径。

在图2b中,齐纳二极管的击穿电压应小于晶体管的V CE 击穿额定值使得齐纳二极管击穿并在大于正常电压之前导通会损坏晶体管。在正常工作期间,当晶体管的集电极出现大于正常电压时,齐纳二极管不导通而是击穿。这个齐纳二极管,即所谓的瞬态抑制二极管,应该具有快速响应。此外,二极管的功率处理能力应足够高,以便在二极管钳位高电压时以及瞬时功耗高时承受应力。

在图2c中,缓冲网络由一个电阻组成电容器串联连接在晶体管两端,二极管连接在电阻器两端。该网络可防止电路超出器件的反向偏置安全工作区特性。缓冲网络可减少开/关周期内晶体管的压力,并通过降低集电极的dv/dt来减少EMI问题。您应该选择缓冲器组件,以便在晶体管底部没有信号时,不会发生晶体管的V CE 击穿。

您可以使用以下指南(源自简单且熟悉的公式)来计算缓冲器组件值。参考图2c,基本电容 - 电荷方程给出了缓冲电容器存储的电荷量,其中Q是电荷,V是电容器两端的电压,C是电容器的电容:

区分时间t,给出电流或电荷变化率:

假设开关时间为50% ,通过电容器的平均电流是I/2,其中I是全电流。因此,

在整个周期内,dt代表晶体管集电极电流的下降时间。请记住,仅当晶体管关闭时,电流才会流过电容器。因此,在整个周期内对C的等式进行积分得出

因此,缓冲电容C的值如下:

在这种情况下,电容两端的电压大约低一个二极管压降与集电极电压相比,该等式包括晶体管的V CEO 等级的降额系数0.75。关闭时,晶体管会消耗电容器存储的能量。这个能量是:

换句话说,晶体管关闭时消耗的功率是:

其中f是晶体管的开关频率。

RC时间常数应小于晶体管导通时间的一半,以便缓冲器网络在晶体管关闭时准备充电。使用此规则,您可以计算缓冲电阻R

寄生效应也会导致问题

除了V CE 击穿,其他问题,通常发生在开关模式电源和其他变压器驱动电路中,是由变压器寄生效应引起的。变压器中的漏电感和寄生电容是破坏性寄生效应,会影响开关器件的可靠运行。由于寄生效应,坏的变压器会导致电源中的大功率损耗。通常,磁力线跟随磁路通过初级和次级绕组之间的磁芯。如果初级绕组和次级绕组之间的磁耦合很差,则磁通线会通过其他路径并通过绕组之间的空气完成磁路(图3a)。这种漏磁通会在初级和次级绕组中产生漏电感,这表现为初级和次级绕组中的小串联电感(图3b)。类似地,变压器的初级和次级绕组之间存在寄生电容。而且,绕组的匝之间和绕组中的层之间存在电容。与漏电感相结合,杂散电路和其他寄生电容可以形成谐振电路,这可能导致输出电路中的电压尖峰。您可以通过将次级绕组短路并在变压器的工作频率下测量初级绕组的电感来测量漏电感。漏电感取决于变压器的结构,但并不高度依赖于频率。

这些漏电感会导致大的输出尖峰,从而导致电路故障。例如,在最近的一种情况中,基于变压器的电源电路中的开关晶体管经常出现故障。在晶体管的输出端和集电极处可观察到大的电压尖峰,尖峰的幅度远高于正常的开关波形(图4)。对晶体管故障模式的分析表明,该器件由于集电极 - 发射极击穿引起的电过载而发生故障(图1)。电压尖峰的幅度超过晶体管的V CE 额定值,因此器件失效。进一步的分析追溯了由于变压器结构和绕组技术不良导致的这些电压尖峰导致变压器绕组中的高漏电感的原因。改善变压器绕组技术以减少漏感可以纠正这个问题。

合适的变压器构造技术包括散布初级和次级绕组以覆盖整个绕线管并确保绕组之间的紧密接近,并在初级绕组和次级绕组之间放置静电屏。

将绕组和确保紧密接近可减少磁通泄漏,并在绕组之间产生更好的磁耦合。降低漏感的关键是最大化初级和次级绕组之间的磁耦合。在交错式绕组技术中,将次级绕组放置在两层初级绕组之间。换句话说,您将初级绕组分成两个部分,这两个部分位于次级绕组的两侧。在初级和次级之间实现紧密磁耦合的另一种技术是在缠绕变压器之前将导线绞合在一起;这种缠绕技术称为双线缠绕。

静电屏幕通常由足以覆盖整个缠绕区域的铜箔组成;它通过绕组中心的连接接地。在屏幕末端重叠之前,您可以通过放置绝缘材料来确保箔片的两端不接触。如果端部没有绝缘,则短路的铜箔将像短路的单匝次级绕组一样,并且由于该短路箔中的过电流或“次级”,过热可能会破坏该箔。您将箔片的中心点接地,以抵消由于屏幕中的感应电流引起的感应效应,屏幕现在以相反的方向流向地面。

-

电感电路

+关注

关注

0文章

9浏览量

8023 -

PCB打样

+关注

关注

17文章

2968浏览量

21693 -

华强PCB

+关注

关注

8文章

1831浏览量

27747 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

43031

发布评论请先 登录

相关推荐

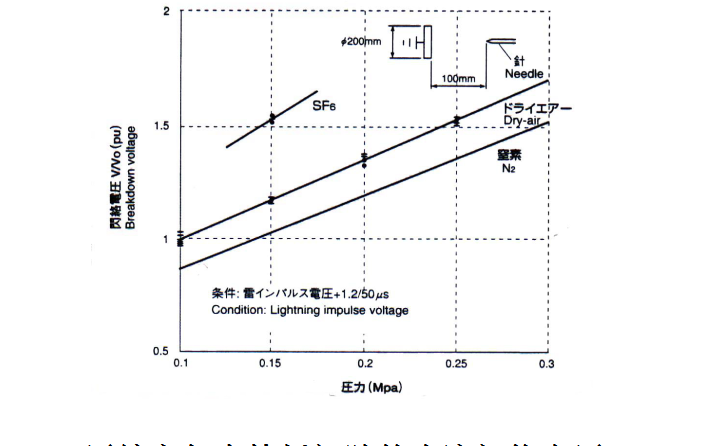

中压开关设备的出厂绝缘试验

纯电感电路中电压与电流的关系解析

高压开关设备的维护和故障排除指南

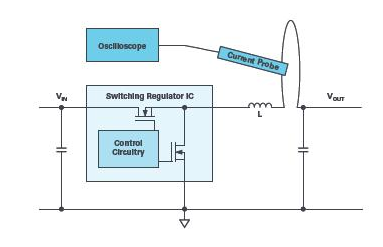

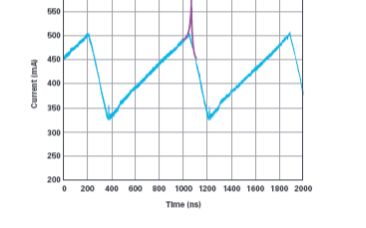

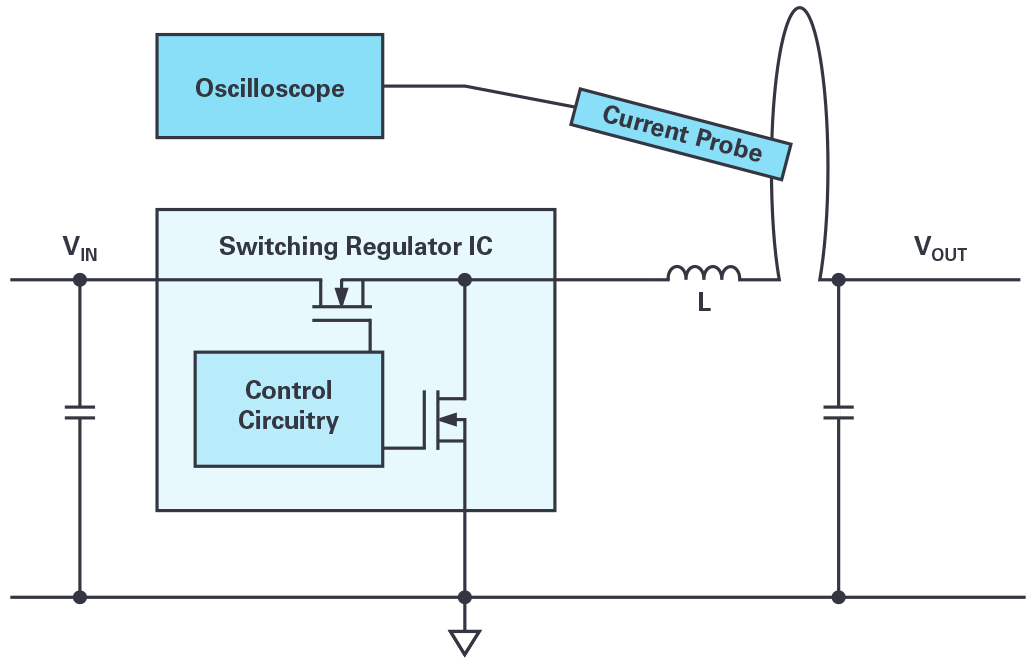

测量开关电源中的电感电流的最佳方式

高压开关设备机械特性

自感电路中出现的过电压现象与电感电路教学

中压气体绝缘金属的封闭开关设备应该如何设计?

开关电源中测量电感电流的最佳方法

电感电流 ――DC/DC 电路中电感的选择

什么技术可减少电感电路中的开关设备故障

什么技术可减少电感电路中的开关设备故障

评论