数字钟是一种用数字显示秒、分、时的计时装置,与传统的机械钟相比,它具有走时准确,显示直观、无机械传动装置等优点,因而得到了广泛的应用。小到人们日常生活中的电子手表,大到车站、码头、机场等公共场所的大型数显电子钟。在控制系统中也常用来做定时控制的时钟源。

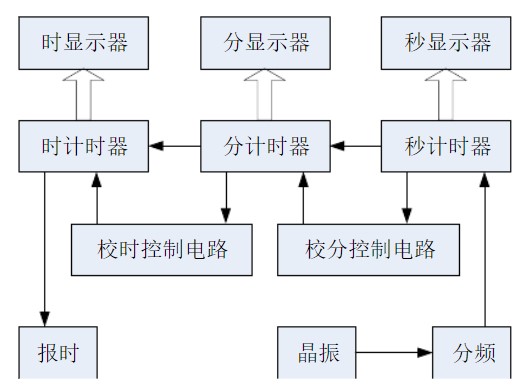

数字钟实际上属于一种数字电路装置,可以实现时,分和秒的计时。相比传统的机械时钟而言,数字钟的准确性更高,而且使用寿命更长,这也是数字钟被广泛应用的原因。数字钟的应用原理就是利用数字电路,主要包括以下电路:一是组合逻辑电路,二是时序电路。数字钟由以下几个部分组成:一是振荡器,二是分频器,三是发生器,四是校正电路,五是60进制秒计时器,六是60进制分计时器,七是24进制秒计时器,八是24进制分计时器。

多功能数字钟可以实现以下功能:一是计时功能,二是校时功能,三是整点报时功能,四是显示星期的功能,五是闹钟的功能。多功能数字钟的设计与制作是数字钟功能发挥的前提和基础,只有保证数字钟设计和制作的合理性,才能充分发挥出数字钟的功能。

数字钟由振荡器、分频器、计数器、译码显示、报时等电路组成。其中振荡器和分频器组成标准秒信号发生器,直接决定计时系统的精度。由不同进制的计数器、译码器和显示器组成计时系统。将标准秒信号送入采用60进制的“秒计数器”,每累计60sec就发出一个“分脉冲”信号,该信号将作为“分计数器”的时钟脉冲。“分计数器”也采用60进制计数器,每累计60min,发出一个“时脉冲”,该信号将被送到“时计数器”。“时计数器”采用12或24进制计数器,可实现对一天12h或24h的累计。译码显示电路将“时”、“分”、“秒”计数器的输出状态通过6位7段译码显示器显示出来,可进行整点报时,计时出现误差时,可以用校时电路校时、校分。

-

振荡器

+关注

关注

28文章

3832浏览量

139030 -

分频器

+关注

关注

43文章

447浏览量

49874 -

计数器

+关注

关注

32文章

2256浏览量

94476 -

信号发生器

+关注

关注

28文章

1472浏览量

108739

发布评论请先 登录

相关推荐

数字钟设计

数字钟的设计任务及功能要求

数字钟设计方案

基于FPGA和Quartus II的多功能数字钟设计与实现

基于Quartus II平台的多功能数字钟的设计

如何使用STC89C52单片机实现多功能数字钟的设计

数字钟的结构组成及功能实现

数字钟的结构组成及功能实现

评论