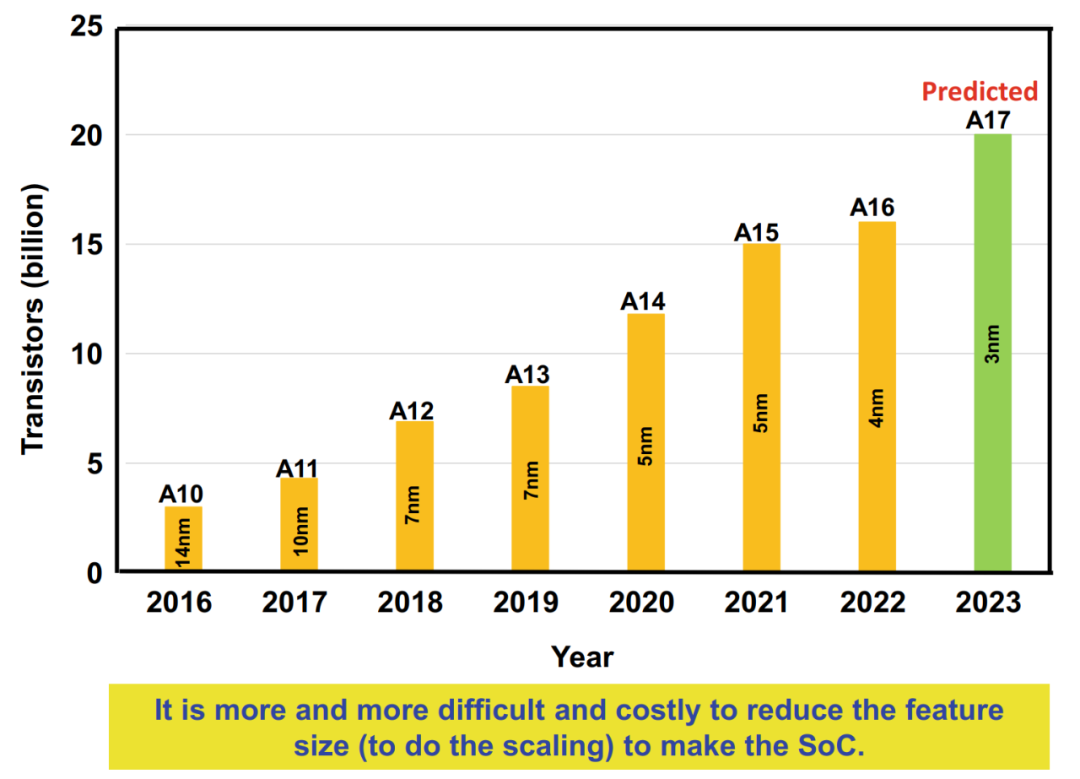

异构计算正大行其道,更多不同类型的芯片需被集成在一起,而依靠缩小线宽的办法已经无法同时满足性能、功耗、面积以及信号传输速度等多方面的要求。在此情况下,越来越多的厂商开始把注意力放在系统集成层面,通过封装技术寻求突破,3D封装已成为主流半导体晶圆制造厂商重点发展和推广的技术。

虽然台积电、三星、英特尔等大厂不遗余力推广,但3D封装的一匹“黑马”却开始一骑绝尘。

据快科技报道,在ISSCC 2020会议上,法国公司CEA-Leti发表一篇论文,介绍他们使用3D堆栈、有源中介层等技术制造的96核芯片。根据他们的论文,96核芯片有6组CPU单元组成,每组有16个核心,不过Leti没提到CPU内核使用ARM、RISC-V还是其他架构,但使用的是28nm FD-SOI工艺。

Leti的6组CPU核心使用3D堆栈技术面对面配置,通过20um微凸点连接到有源中介层上,后者又是通过65nm工艺制造的TSV(硅通孔)技术连接,实现了65nm和28nm合体。在这个96核芯片上,除了CPU及TSV、中介层之外,还集成3D插件、内存、I/O主控及物理层等。这款96核芯片集成了大量不同工艺、不同用途的核心,电压管理、I/O等外围单元也集成进来了,实现了异构芯片的一次重要突破。

通过灵活高效、可扩展的缓存一致性架构,这个芯片最终可能扩展到512核,在高性能计算等领域有望得到推广应用。

值得一提的是,在ISSCC 2020上,英特尔也介绍了10nm与22FFL混合封装的Lakefield处理器,采用的是英特尔的Foveros 3D封装技术,封装尺寸为12 X 12 X 1毫米。Lakefield作为英特尔首款采用了Foveros技术的产品,能够在指甲大小的封装中取得性能、能效的优化平衡。

-

半导体

+关注

关注

334文章

27286浏览量

218027 -

晶圆

+关注

关注

52文章

4890浏览量

127929 -

3D封装

+关注

关注

7文章

133浏览量

27118

发布评论请先 登录

相关推荐

【一文看懂】什么是异构计算?

发现基于Zen 5架构的AMD Threadripper “Shimada Peak” 96核和16核CPU

全志T113双核异构处理器的使用基于Tina Linux5.0——异构双核通信验证

全志T113双核异构处理器的使用基于Tina Linux5.0——异构双核通信的具体实现

异构集成封装类型详解

基于国产异构双核(RISC-V+FPGA)处理器,AG32开发板开发资料

浅谈国产异构双核RISC-V+FPGA处理器AG32VF407的优势和应用场景

君正X2600在3D打印机上的优势:多核异构,远程控制与实时控制

AvaotaA1全志T527开发板AMP异构计算简介

异构混训整合不同架构芯片资源,提高算力利用率

多核异构通信框架(RPMsg-Lite)

YY3568多核异构(Linux+RT-Thread)--启动流程

异构96核芯片有望得到推广

异构96核芯片有望得到推广

评论