CEVA,全球领先的智能和互联设备信号处理平台和人工智能处理器 IP 的授权许可厂商宣布推出世界上功能最强大的DSP架构Gen4 CEVA-XC。这款全新架构瞄准5G端点和无线接入网络(RAN)、企业接入点以及其他数千兆数据处理、且低延迟应用,针对这些应用所需的最复杂并行处理工作负载提供了无与伦比的性能。

第四代CEVA-XC的强大架构统一了标量和矢量运算处理,可实现两次8路VLIW和前所未有的14,000位数据级并行。它采用的先进深层流水线架构使得在7nm工艺节点下可实现1.8 GHz主频,并使用了独特的物理设计架构来实现完全可综合的设计流程,以及创新的多线程设计,允许处理器动态地配置为宽SIMD机或划分为较小的同时SIMD线程。第四代CEVA-XC架构还具有一个使用2048位内存带宽的新颖内存子系统,具有连贯一致的、紧耦合的内存,以支持高效的并发多线程和内存接入。

Linley Group高级分析师Mike Demler表示:“ 第四代CEVA-XC架构是CEVA致力以行业领先的力度进行DSP并行处理的创新。这款架构具有动态可重配置的多线程和高速设计,以及用于控制和运算处理的全面功能,为用于5G基础架构和端点的ASIC和ASSP器件的普及发展奠定了基础。”

第一个基于第四代CEVA-XC架构的处理器是多核CEVA-XC16,这是有史以来运行速度最快的DSP内核,瞄准各种形式的5G RAN体系结构的快速部署,包括开放式RAN(O-RAN)、基带单元(BBU)聚合以及Wi-Fi和5G企业接入点。CEVA-XC16还适用于与基站运作相关的海量信号处理和AI工作负载。

CEVA-XC16在设计时充分考虑了最新的3GPP规范,并且基于CEVA与领先的无线基础架构供应商合作开发其蜂窝基础架构ASIC的丰富经验。CEVA前代CEVA-XC4500和CEVA-XC12 DSP现在助力4G和5G蜂窝网络,并且一家领先的无线设备供应商已将新型CEVA-XC16用于其下一代5G ASIC设计。

CEVA-XC16提供高达每秒1600 GOPS的高并行度性能,可以重新配置为两个单独的并行线程,两者可以同时运行,共享具有高速一致性缓存的L1数据存储器,从而直接提升PHY控制处理的延迟和性能效率,而无需使用额外的CPU。相比在拥挤区域连接大量用户的单核/单线程架构,这些全新概念设计将每平方毫米的性能提高了50%。这对于定制5G基站芯片普遍采用的大型内核集群而言,可节省35%的芯片面积。

CEVA-XC16的其他主要功能包括:

最新一代双CEVA-BX标量处理器单元——支持真正的并发多线程运行

可将矢量单位资源动态分配给处理线程——最好地利用矢量单位资源,并减少复杂流程的开销

先进的标量控制架构和工具,通过使用最新的动态分支预测和循环优化,以及基于LLVM的编译器,相比前代产品,可将代码大小减少30%

用于FFT和FIR的全新指令集架构——可将性能提高两倍

增强的多用户功能,支持大带宽分配给单一用户也支持精细的用户分配

上代CEVA-XC4500和CEVA-XC12 DSP的软件可简单迁移

CEVA副总裁兼移动宽带业务部门总经理Aviv Malinovitch表示:“5G是一项具有跨越消费者、工业、电信和AI领域的多种增长矢量的技术,应对这些零散而复杂的用例需要全新的处理器思维和实践,而我们的第四代CEVA-XC架构采用了这一全新方法,通过突破性创新和设计实现了前所未有的DSP内核性能。CEVA-XC16 DSP是这项成就的例证,并且为希望从不断增长的5G 资产开支和Open RAN网络架构中获益的OEM厂商和半导体供应商大幅降低了进入门槛。”

-

dsp

+关注

关注

553文章

7987浏览量

348745 -

CEVA-XC

+关注

关注

0文章

4浏览量

7417

发布评论请先 登录

相关推荐

意法半导体第四代碳化硅功率技术问世

意法半导体发布第四代SiC MOSFET技术

SK启方半导体推出第四代0.18微米BCD工艺

富士康,布局第四代半导体

capsense第四代和第五代在感应模式上的具体区别是什么?

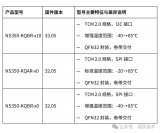

国民技术第四代可信计算芯片NS350投入量产

Vishay推出采用PowerPAK 8x8LR封装的第四代600 VE系列功率MOSFET

国民技术第四代可信计算芯片NS350正式投入量产

国民技术第四代可信计算芯片NS350正式投入量产!

新品发布!国民技术第四代可信计算芯片NS350正式投入量产

CEVA-XC架构第四代出炉 提供了无与伦比的性能

CEVA-XC架构第四代出炉 提供了无与伦比的性能

评论