根据分频器设计时都是按恒阻抗法计算的原理,采用了先用标准电阻代替扬声器对分频网络进行调试,使之符合其标准衰减斜率,然后去掉电阻,接上扬声器并加上阻抗校正网络再重新进行调试的方法获得成功,实际试听感觉不错。

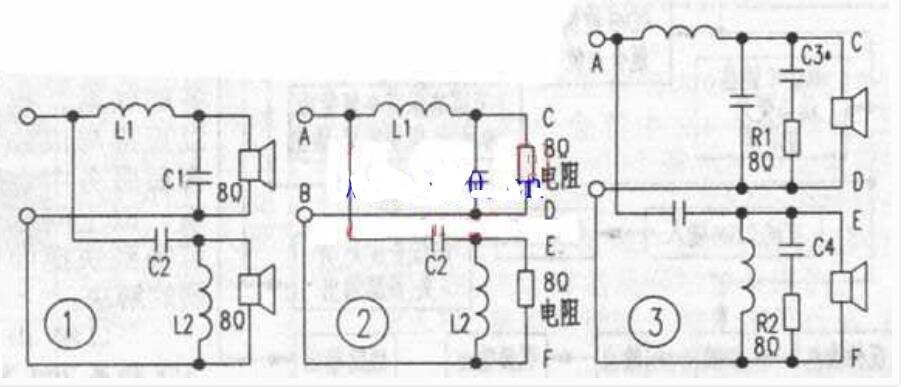

例如,我们要自制一个如图1所示的分频器,先用图表法绕好线圈L1和L2,可多绕几圈以便调节。按图2连接,从AB端输入分频点频率的功放信号电压,调节L1、C1、L2、C2,用万用表测量C、D端和E、F端电压使之符合分频点的衰减特性。然后按图3所示加入阻抗校正网络和接入扬声器进行调试,调节R1、C3及R2、C4使之符合分频点的衰减特性即可。对三分频而言也采用此方法调试,只是高频段可不加校正网络。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表德赢Vwin官网

网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

分频器

+关注

关注

43文章

447浏览量

49874

发布评论请先 登录

相关推荐

分频器的定义和作用

分频器是一种电子电路或装置,其核心功能是将输入信号分离成多个具有不同频率范围的输出信号。这些输出信号的带宽均小于原始输入信号的带宽,使得每个频段的信号都能针对性地进行处理或应用。分频器

CDCE906 PLL频率合成器/乘法器/分频器数据表

德赢Vwin官网

网站提供《CDCE906 PLL频率合成器/乘法器/分频器数据表.pdf》资料免费下载

发表于 08-22 09:30

•0次下载

LMK01000高性能时钟缓冲器、分频器和分配器数据表

德赢Vwin官网

网站提供《LMK01000高性能时钟缓冲器、分频器和分配器数据表.pdf》资料免费下载

发表于 08-21 09:53

•0次下载

CDCM6208V2G具有小数分频器的2:8时钟发生器/抖动消除器数据表

德赢Vwin官网

网站提供《CDCM6208V2G具有小数分频器的2:8时钟发生器/抖动消除器数据表.pdf》资料免费下载

发表于 08-20 09:14

•0次下载

ESP8266EX PWM时钟预分频器可以修改吗?

ESP8266EX文件表明最大PWM频率为1Khz。我需要 20Khz 到 100Khz。PWM时钟预分频器可以修改吗?

我对Delta_Sigma硬件有同样的问题。

发表于 07-19 10:53

CMOS24级分频器CD4521B TYPES数据表

德赢Vwin官网

网站提供《CMOS24级分频器CD4521B TYPES数据表.pdf》资料免费下载

发表于 05-22 09:47

•0次下载

CMOS十进计数器/分频器CD4026B CD4033B TYPES数据表

德赢Vwin官网

网站提供《CMOS十进计数器/分频器CD4026B CD4033B TYPES数据表.pdf》资料免费下载

发表于 05-21 09:16

•0次下载

CMOS计数器/分频器CD4017B CD4022B TYPES 数据表

德赢Vwin官网

网站提供《CMOS计数器/分频器CD4017B CD4022B TYPES 数据表.pdf》资料免费下载

发表于 05-20 10:20

•1次下载

分频器的作用 分频器的功率是不是越大越好

分频器是一种电子设备,用于将输入信号分成不同频率的输出信号。其主要作用是将原始输入信号分离成多个频率范围内的信号,以供不同的电路进行处理。分频器广泛应用于通信、测量和音频系统中。

锁相环整数分频和小数分频的区别是什么?

锁相环整数分频和小数分频的区别是什么? 锁相环(PLL)是一种常用的电子电路,用于将输入的时钟信号与参考信号进行同步,并生成输出信号的一种技

CAN时钟分频器在CANbus模块上不执行任何操作的原因?

我一直在使用 dsPIC33CH128MP506 进行一些 CANbus 通信。

它能够进行CAN-FD,并且有两个独立的波特率分频器,用于标称波特率和数据波特率。它们是:C1NBT

发表于 01-22 06:36

自制一个简易的音箱分频器电路

自制一个简易的音箱分频器电路

评论