在某测试系统的开发中,需要用数据总线来实现自动测试设备(Automatic Test Equipment,简称,ATE)和被测单元(Unit Under Test,简称UUT)之间的串行通信。实际设计时,采用串行通信方式,以32位双极性(±5V 归零)串行码(称之为一个代字)向UUT分时发送控制指令和状态信息,同时接收U-UT送出的代字信息。文中对该电路的设计原理和部分软件程序的实现方法做了详细地介绍。

1 、50kHz时基信号发生器

由于在此测试系统中的通信均是以串行码的形式进行的,且数据传输的速率为50kbps,因此,设计时,采用了如图1所示的550kHz时基信号发生器。

图1中,SG8002是日本EPSON公司生产的可编程晶体振荡器,其频率稳定性为±100ppm/(在-20℃-+70℃范围内)。该编程晶体振荡器产生的1.2MHz脉冲信号经54LSl07双JK触发器4分频后可得到300kHz的方波。此方波输出分两路,一路经54LSl07再次2分频后形成150kHz信号CPl50,作为测试系统的自检、外部检定以及对该测试系统的测试扩展;另一路则先经4位移位寄存器54LS95后,再进行6分频,从而得到所需的50kHz时基信号CP50。

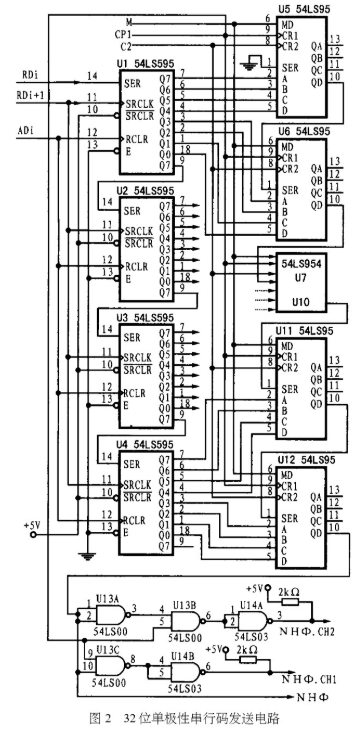

2 、32位单极性串行码发送电路

32位单极性串行码发送电路的主要作用是将PC/104总线的数据端口D0-D7送出的串行TTL电平经54LS595移位锁存至54LS95移位寄存器的Di输入口,然后在并行置入脉冲C2下降沿的作用下打入到Qi输出口,最后在32个串行右移脉冲CP1下降沿的作用下形成所需的、含有特定意义的32位单极性双通道串行码NHΦ.CHl和NHΦ.CH2。具体的电路实现原理如图2所示。

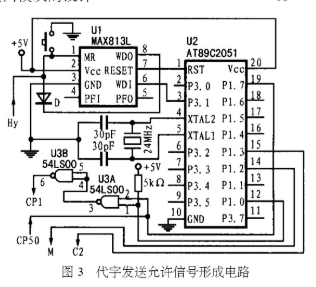

3 、代宇发送允许信号形成电路

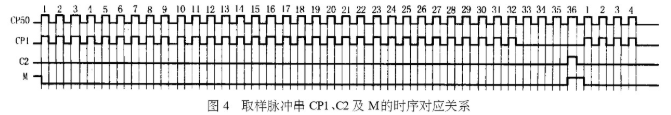

该电路以AT89C2051微处理器为控制核心将50kHz时基信号发生器产生的时基信号CP50进行隔段取样,以形成54LS95所需的串行右移脉冲CPl、并行置入脉冲C2及工作方式控制信号M。其电路原理如图3所示。

图3中,MAX813L芯片用于组成AT89C2051微处理器的复位监控电路,同时此芯片也可充当“看门狗”(WatchDog),以防止程序运行时出现“飞跑”现象。50kHz的时基信号经过AT89C2051的隔段取样例程后可形成满足图4所示时序要求的采样脉冲串CPl、C2及M。

下面是AT89C2051对50kHz时基信号的隔段取样程序:

ORG 0000H

START: SETB P1.7

CLR P1.0

CLR P1.2

CLR p1.3 CPL P3.1

MOV R0,#00H

DELAY: MOV TMOD,#01H

SETB TR0

MOV A,#32H

DELAY1: MOVTHO,#0B1H

MOV TL0,#0EOH

DELAY2: JNB TF0,DELAY2

CLR TF0

CPL P3.1

DEC A

DJNE A,#00H,DELAY1

LOOP1: JNB P1.7,LOOPl

LOOP2: JB P1.7,LDOP2

INC R0[page]

CJNE R0,#02H,LOOP3

SETB P1.2

LOOP3: JNB P1.7,LOOP3

SETB P1.3

LOOP4: JB Pl.7,LOOP4

CLR P1.3

INC R0

LOOP5: JNB Pl.7,LOOP5

LOOP6: JB P1.7,LOOP6

CLR P1.2

INC R0

SETB P1.0

LOOP7: JNB P1.7,LOOP7

LOOP8: P1.7,LOOP8

INC R0

CJNE R0,#24H,LOOP7

CLR P1.0

CPL P3.1

MOV R0,# 00H

SJMP LOOPl

END

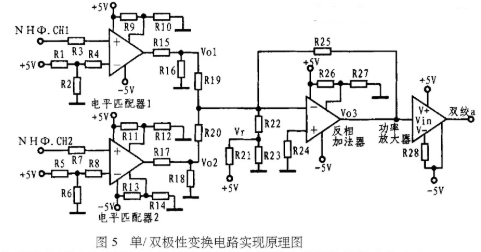

4 、单/双极性变换电路

单/双极性变换电路主要是由电平匹配器1、电平匹配器2、反相加法器以及功率放大器等4部分组成,具体的电路原理如图5所示。

该电路的基本工作原理是将32位单极性串行码发送电路产生的双通道互补对称串行码NHΦCH1和NHΦ.CH2信号送电子匹配器1和2进行处理,以形成反相加法器所需的输入信号Vol和V02,然后将Vol、V02以及补偿电子信号Vr经加法器线性叠加以得到双极性串行码“双绞a”信号。由于“双绞a”信号功率较小,不能直接驱动被测设备的内部电路,故需将其再进行一级功率放大以满足实际需要。

在图5中,电平匹配器、反相加法器均采用OPA689高精度高速集成运放芯片,而功率放大器则采用大功率高频功放芯片BUF634。

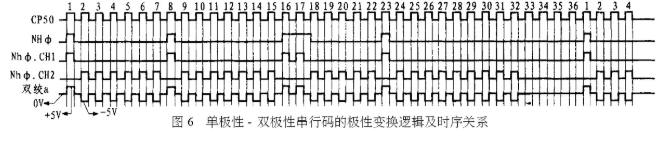

图6所示是单极性-双极型串行码的极性变换逻辑及时序关系。

责任编辑:gt

-

测试

+关注

关注

8文章

5269浏览量

126595 -

串行通信

+关注

关注

4文章

571浏览量

35394 -

信号发生器

+关注

关注

28文章

1472浏览量

108739

发布评论请先 登录

相关推荐

基于USB通信技术的自动测试系统设计

机载电子设备通用自动测试系统研究与实现

天线自动测试系统

分布式测试系统数据通信方式

基于多P89C668单片机的组合逻辑电路自动测试诊断系统设计

基于USB通信的自动测试系统设计

基于CY7C68013A的GPIF通信方式的自动测试系统

USB通信技术在自动测试系统中的应用

模拟IC自动测试系统的直流参数测试单元

采用串行通信方式实现系统中自动测试设备和被测单元的通信设计

采用串行通信方式实现系统中自动测试设备和被测单元的通信设计

评论