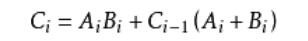

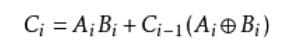

全加器逻辑表达式

一位全加器的表达式如下:

Si=Ai⊕Bi⊕Ci-1

第二个表达式也可来用一个异或门来代替或门对其中两个输入信号进行求和:

其中Ai为被加数,Bi为加数,相邻低位来的进位数为Ci-1,输出本位和为Si。向相邻高位进位数为Ci。一位全加器可以处理低位进位,并输出本位加自法进位。多个一位全加器进行级联可以得到多位全加器。常用二进制四位全加器74LS283。

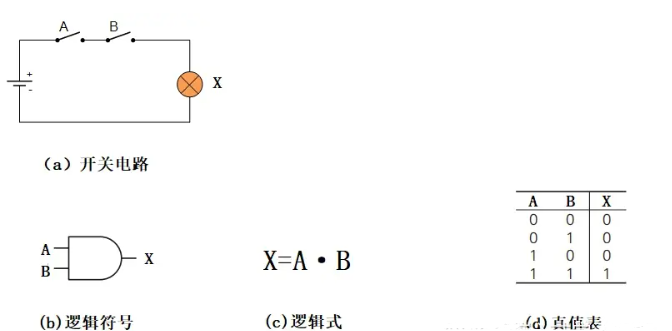

全加器的逻辑功能

当多位数相加时,半加器可用于最低位求和,并给出进位数。第二位的相加有两个待加数![]() 和

和![]() ,还有一个来自前面低位送来的进位数

,还有一个来自前面低位送来的进位数![]() .这三个数相加,得出本位和数(全加和数)

.这三个数相加,得出本位和数(全加和数)![]() 和进位数

和进位数![]() .这种就是“全加“,下表为全加器的逻辑状态表。

.这种就是“全加“,下表为全加器的逻辑状态表。

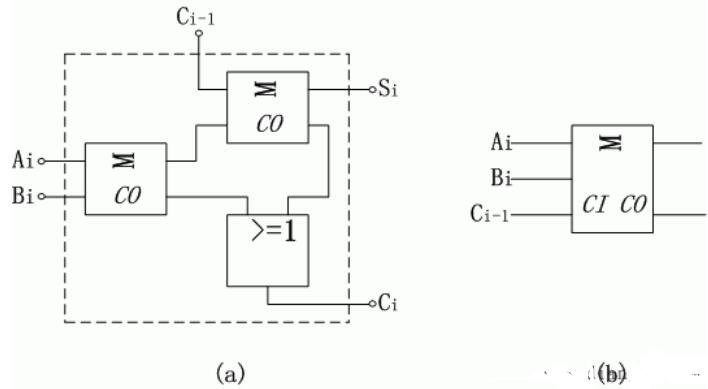

全加器可用两个半加器和一个“或“门组成。

如上图(a)所示。![]() 和

和![]() 在第一个半加器中相加,得出的结果再和

在第一个半加器中相加,得出的结果再和![]() 在第二个半加器中相加,即得出全加和

在第二个半加器中相加,即得出全加和![]() 。两个半加器的进位数通过”或“门输出作为本位的进位数

。两个半加器的进位数通过”或“门输出作为本位的进位数![]() 。全加器也是一种组合逻辑电路,其图形符号如上图(b)所示。

。全加器也是一种组合逻辑电路,其图形符号如上图(b)所示。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表德赢Vwin官网

网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

全加器

+关注

关注

10文章

62浏览量

28493

发布评论请先 登录

相关推荐

半加器和全加器的区别是什么

半加器(Half Adder)和全加器(Full Adder)是数字电路中的基本组件,用于执行二进制加法运算。它们的主要区别在于功能和输入输出的数量。 1. 功能差异 半加器 : 半加器只能处理两个

数字逻辑怎么把逻辑图画成电路图

。理解这些符号及其代表的逻辑操作是转换的第一步。 二、列出逻辑表达式 从逻辑图的输入端开始,逐级写出每个逻辑符号输出端的

鸿蒙原生应用元服务开发-仓颉基本概念表达式(二)

场景中,对于特定取值的迭代变量,我们可能需要直接跳过、进入下一轮循环,虽然可以使用 if 表达式和 continue 表达式在循环体中实现这一逻辑,但仓颉为此提供了更便捷的表达方式——

发表于 08-09 14:26

鸿蒙原生应用元服务开发-仓颉基本概念表达式(一)

程序能够表达更复杂的逻辑,在仓颉中,这种用来控制执行流的语言元素就是条件表达式和循环表达式。

在仓颉编程语言中,条件表达式分为 if

发表于 08-08 10:27

求助,有关表达式选项卡(ADS)的问题求解

你好。

我看不到表达式选项卡中的某些变量值。

数组的大小显然是 256,但我最多只能看到 100。

请问问题出在哪里?

谢谢。

发表于 06-03 06:23

具有快速进位的高速CMOS逻辑 4位二进制全加器CDx4HC283和CDx4HCT283数据表

德赢Vwin官网

网站提供《具有快速进位的高速CMOS逻辑 4位二进制全加器CDx4HC283和CDx4HCT283数据表.pdf》资料免费下载

发表于 04-28 11:01

•0次下载

mapgis属性筛选表达式

篇文章中,我们将详细讨论MapGIS的属性筛选表达式,包括语法、操作符和函数等。 属性筛选表达式是一种在MapGIS中用于指定要素选择条件的代码。它由一组操作符、函数和属性字段组成,用于描述要筛选的要素的特征。在MapGIS中,属性筛选

西门子博途的算术表达式

算术表达式既可以是一个数字值,也可以是由带有算术运算符的两个值或表达式组合而成。 算术运算符可以处理当前 CPU 所支持的各种数据类型。如果在该运算中有 2 个操作数,那么可根据以下条件来确定结果的数据类型。

rs触发器的逻辑表达式

逻辑表达式是描述逻辑关系的符号表示,可以用于定义和描述各种电路和逻辑操作。在逻辑电路中,RS触发器是一种基本的存储器元件,也被称为锁存器。

全加器的逻辑表达式怎么推

全加器是计算机中常用的一种逻辑电路,用于实现二进制加法运算。全加器接受两个输入位和一个进位位,并输出一个和位和一个进位位。它的逻辑表达式可以

全加器逻辑表达式_全加器的逻辑功能

全加器逻辑表达式_全加器的逻辑功能

评论