JEDEC固态存储协会于今日正式发布了DDR5SDRAM标准(JESD79-5),为全球计算机拉开新时代序幕。

简言之,DDR5内存芯片Bank数量翻番到32,每Bank的自刷新速度翻番到16Gbps。VDD电压从DDR4的1.2V降至1.1V,也就是减少功耗。此外,芯级ECC、更好的设计伸缩性、更高的电压耐受度等都保证了性能、产能、工艺水准等。

按照JEDEC的说法,DDR5内存的引脚带宽(频率)是DDR4的两倍,首发将以4.8Gbps(4800MHz)起跳,比末代DDR4的标准频率3200MHz增加了50%之多,总传输带宽提升了38%,未来将最高摸到8400MHz左右。

基于新标准的硬件预计将于2021年推出,先从服务器层面开始采用,之后再逐步推广到消费者PC和其他设备。

更快:一个DIMM,两个通道

DDR5再次提高了内存带宽。每个人都希望获得更高的性能(尤其是在DIMM容量不断增长的情况下),这也是这次DDR5提升的重点。

对于DDR5来说,JEDEC希望比通常的DDR内存规范更积极地开始工作。通常情况下,新的标准是从上一个标准的起点开始的,例如DDR3到DDR4的过渡,DDR3正式停止在1.6Gbps,DDR4从那里开始。然而对于DDR5来说,JEDEC的目标要高得多,预计将以4.8Gbps的速度推出,比DDR4官方3.2Gbps最高速度快了50%左右。而在之后的几年里,当前版本的规范允许数据速率达到6.4Gbps,比DDR4的官方峰值快了一倍。

这些速度目标的基础是DIMM和内存总线的变化,以便在每个时钟周期内提供和传输更多数据。对于DRAM速度来说,最大的挑战来自于DRAM核心时钟速率缺乏进步。专用逻辑仍然在变快,内存总线仍然在变快,但支撑现代内存的基于电容和晶体管的DRAM时钟速度还不能超过几百兆赫。因此,为了从DRAMDie中获得更多的收益--维持内存本身越来越快的假象,并满足实际速度更快的内存总线--已经需要越来越多的并行性。而DDR5则再次提升了这一要求。

这里最大的变化是,与LPDDR4和GDDR6等其他标准情况类似,单个DIMM被分解为2个通道。DDR5将不是每个DIMM提供一个64位数据通道,而是每个DIMM提供两个独立的32位数据通道(如果考虑ECC因素,则为40位)。同时,每个通道的突发长度从8个字节(BL8)翻倍到16个字节(BL16),这意味着每个通道每次操作将提供64个字节。那么,与DDR4DIMM相比,DDR5DIMM以两倍的额定内存速度(核心速度相同)运行,将在DDR4DIMM提供的操作时间内提供两个64字节的操作,使有效带宽增加一倍。

总的来说,64字节仍然是内存操作的神奇数字,因为这是一个标准缓存线的大小。如果在DDR4内存上采用更大的突发长度,则会导致128字节的操作,这对于单条高速缓存线来说太大,如果内存控制器不想要两条线的连续数据,充其量也会导致效率/利用率的损失。相比之下,由于DDR5的两个通道是独立的,一个内存控制器可以从不同的位置请求64个字节,这使得它更符合处理器的实际工作方式,并避免利用率的损失。

对标准PC台式机的净影响是,取代了DDR4系统模式,即2个DIMM填满2个通道进行2x64bit设置,而DDR5系统的功能将是4x32bit设置。

这种结构上的变化在其他地方有一些连锁效应,特别是要最大限度地提高这些小通道的使用率。DDR5引入了更细粒度的Bank存储体刷新功能,这将允许一些k存储体在其他使用时进行刷新。这就能更快地完成必要的刷新(电容补给)、控制延迟、并使未使用的存储库更快可用。存储体组的最大数量也从4个增加到8个,这将有助于减轻顺序内存访问的性能折扣。

电子发烧友综合报道,参考自中关村在线、IT之家,转载请注明以上来源和出处。

-

DDR5

+关注

关注

1文章

422浏览量

24140

发布评论请先 登录

相关推荐

雷克沙推出全新战神之翼系列DDR5内存条

DDR3、DDR4、DDR5的性能对比

DDR5内存的工作原理详解 DDR5和DDR4的主要区别

DDR5内存面临涨价潮,存储巨头转向HBM生产

Introspect DDR5/LPDDR5总线协议分析仪

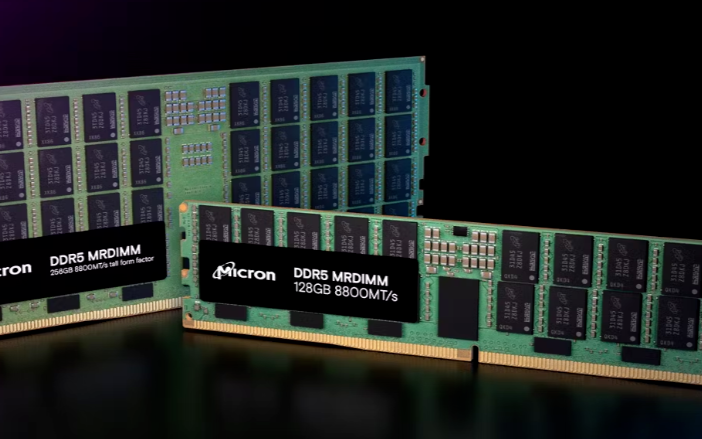

DDR5 MRDIMM内存标准将发,存储厂商方案先行

0706线下活动 I DDR4/DDR5内存技术高速信号专题设计技术交流活动

DDR5内存接口芯片组如何利用DDR5 for DIMM的优势?

DDR5内存冲上8400MHz!DDR3L依然大行其道

lpddr5时序比ddr5慢多少

影驰HOF PRO DDR5 7000内存详细评测报告

4800MHz频率起跳 DDR5内存标准正式公布

4800MHz频率起跳 DDR5内存标准正式公布

评论