随着电子设计领域的高速发展,产品越来越小,速率越来越高,信号完整性越来越成为一个硬件工程师需要考虑的问题。串扰,阻抗匹配等词汇也成为了硬件工程师的口头禅。今天,我们就来学习关于串扰的一些知识。

什么是串扰

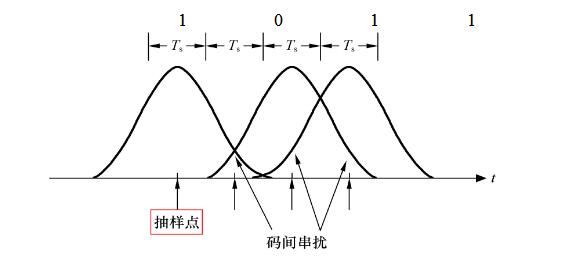

串扰(Crosstalk),顾名思义、是指不同信号互连链路之间的相互干扰。对于传输线而言,即能量从一条传输线耦合到另一条传输线上,当不同传输线产生的电磁场发生相互作用时就会产生。

串扰中的信号耦合分为容性耦合和感性耦合,通常感性串扰占的比例大于容性串扰。

容性耦合会引发驱动电流浪涌,从而导致传输线上的反射。

感性耦合会产生地弹和电源噪声。

在数字电路系统中,串扰现象相当普遍,串扰可以发生在芯片内核、芯片的封装、PCB板上、接插件上、以及连接线缆上,只要有临近的铜互连链路,就存在信号间的电磁场相互作用,从而产生串扰现象。

串扰的危害

串扰可能是数据进行高速传输中最重要的一个影响因素了。它是一个信号对另外一个信号耦合所产生的一种不受欢迎的能量值。根据麦克斯韦定律,只要有电流的存在,就会有磁场存在,磁场之间的干扰就是串扰的来源。这个感应信号可能会导致数据传输的丢失和传输错误。 所以串扰对于综合布线来说,无疑是个最厉害的天敌。

减小信号间串扰的方法

我们知道,信号间的串扰来源于电磁场的互相干扰作用,电场的场强是离信号源中心越远则越弱,所以控制信号间串扰最直接有效的方法就是:

方法一:增加传输线或互连链路之间的间隔距离,减小串扰

在信号串扰的控制上通常有“3W规则”、“ 5H规则”的说法,所谓“3W规则”是指传输线的间距需要大于3倍的传输线线宽W,所谓“5H规则”是指传输线的间距需要大于5倍的传输线与参考平面的距离H。在实际的PCB设计中,要均衡考虑布线空间与串扰控制,遵循的规则可以理解为上面“3W”、“ 5H”两种规则的结合体。

“3H规则”,即传输线之间的间距不小于3倍的传输线与参考平面的距离H。

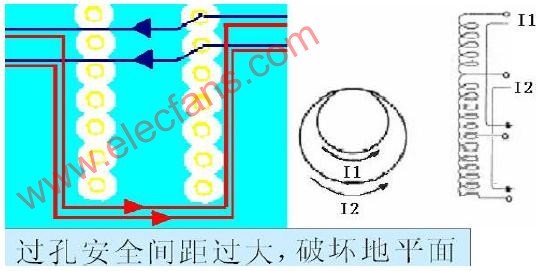

另外,信号在互连链路中的传输,是存在“回流路径”的,电路信号传输必须要形成闭环,它会寻找“环路电感”最小的路径回流到源端;对于有着完整参考地平面的PCB板,信号传输线会沿着传输线垂直正下方的地平面对应的投影路径返回源端,这时有着完美参考平面与回流路径的传输线的抗干扰能力是比较强的,因此:

方法二:让传输线有完整的参考回流地平面,并且层叠设计上尽可能靠近地平面

结合信号的反射理论,串扰信号在到达源端或接收端时,如果互连链路匹配不好,就会再产生反射信号,从而造成在互连链路上的多重发射,这些串扰信号多重反射的结果同样会叠加到受扰信号上,造成串扰噪声的增加,因此:

方法三:传输线及互连链路的良好匹配设计也能减小串扰

编辑:hfy

-

信号完整性

+关注

关注

68文章

1404浏览量

95454 -

数字电路

+关注

关注

193文章

1605浏览量

80577 -

电磁场

+关注

关注

0文章

791浏览量

47260

发布评论请先 登录

相关推荐

PCB不同频率间模拟信号的串扰

如何减小SRAM读写操作时的串扰

VHDL与数字电路系统设计实验指导书

数字电路设计的信号完整性问题探讨

数字电路系统减小信号间串扰的方法

数字电路系统减小信号间串扰的方法

评论