DDR对于做项目来说,是必不可少的。一般用于数据缓存和平滑带宽。今天介绍下Xilinx DDR控制器MIG IP核的例化及仿真。

开发工具:Vivado 2014.4

1、IP Catalog中搜索MIG,点击相应IP进入如下配置界面。

(1)DDR控制器的个数,根据你的实际需求而定,需要几个控制器,你心里应该清楚吧。

(2)MIG IP核的用户侧接口,选择AXI4。基本上,Xilinx的IP都提供了AXI标准接口,所以,控制Xilinx的IP,要先学会AXI协议。

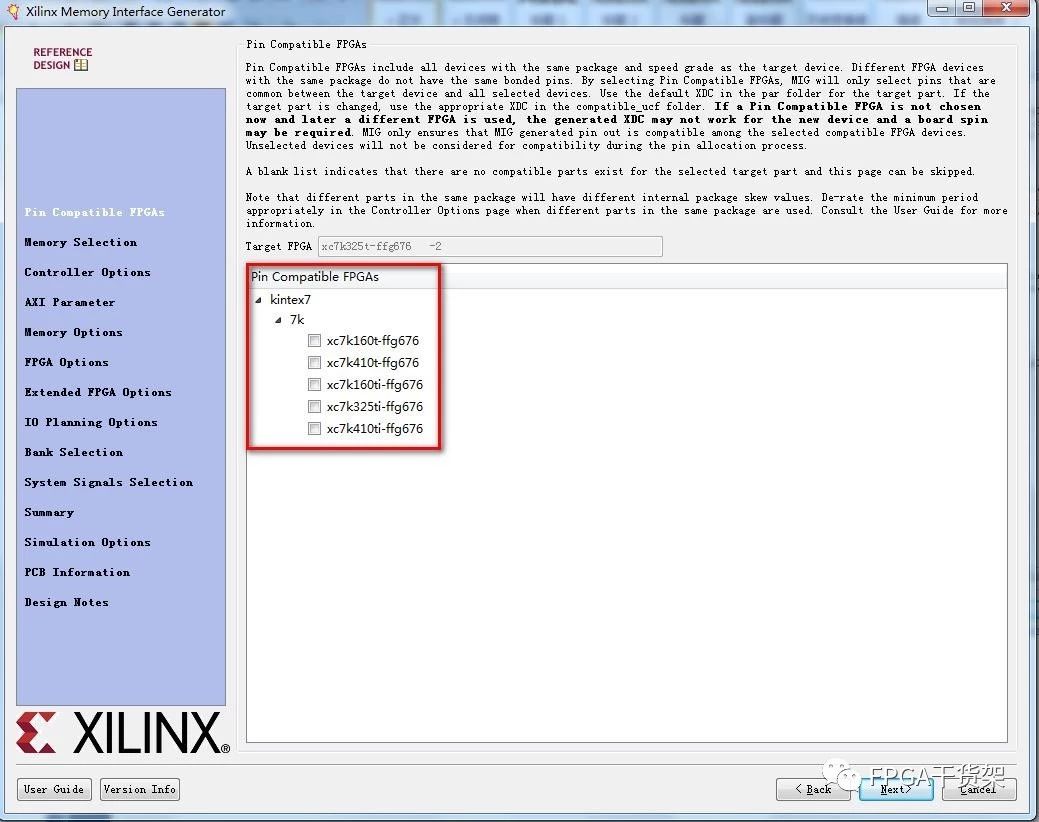

2、点击Next,进入下一配置页面,这里选择是否兼容其他相同封装的芯片,看实际需求,一般默认,直接Next。

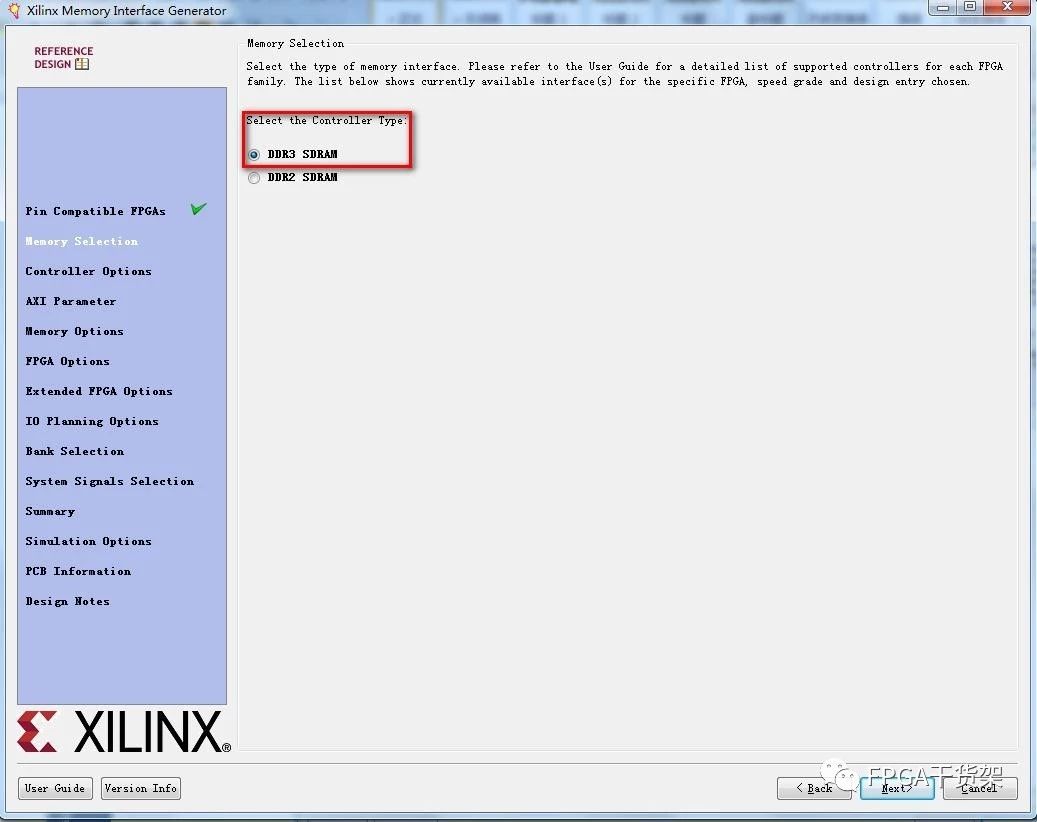

3、选择控制器类型,是DDR3还是DDR2,你自己的芯片是DDR几就选几。

4、下面的配置很重要。

(1)400MHz是DDR芯片实际跑的时钟频率,这个要看硬件设计是多少了。时钟周期范围1112ns~3300ns。

(2)4:1是DDR时钟频率:MIG控制器用户侧的用户时钟频率。若DDR时钟频率是400MHz,则用户时钟频率为100MHz。

(3)Components指的是DDR3的型号是元件类,而不是像笔记本那种的插条类(SODIMMs)。

(4)DDR的型号。

(5)DDR的位宽。

(6)DDR控制器会调度命令的顺序,当选择strict时,严格按照命令先后顺序执行;选择normal时,为了得到更高的效率,可能对命令重排序。为了操作简单,我们选择strict。

5、下面是AXI相关参数的配置,也很重要。

(1)AXI接口的数据位宽。

(2)MIG控制器的仲裁机制,读优先或者写优先。

(3)Narrow Burst支持,disable。

(4)AXI接口的地址位宽。

(5)AXI读写通道的ID宽度。ID用来标识是写响应和写数据的一致性。

6、配置同样重要。

(1)输入系统参考时钟频率。

(2)Burst读写类型为顺序读写,不选交叉读写。

(3)DDR和AXI总线之间的地址映射。涉及到DDR的操作效率。

7、配置不当,将直接导致无法生成IP。

(1)系统时钟,可以选差分、单端、No Buffer,根据实际情况选。

(2)参考时钟,可以和系统时钟共用,选择No Buffer。

(3)系统复位极性,根据实际情况选。

10、仿真

每次涉及到仿真官方提供的IP时,都要诟病一下Altera做的多难用,Xilinx做的多人性化。Xilinx针对IP的仿真,只需要在生成IP后,点击个Open Example Design即可,而脑残的Altera非要给你整得特别复杂,非得你运行个tcl脚本(这还算简单的呢),才能启动仿真,不能和Xilinx学学吗?

对于K7的MIG IP核,启动仿真后,初始化完成大约在106us左右,要耐心等待啊,初始化完成是第一步,初始化完成了,才能有后续,不然的话,老老实实先让初始化拉高再说吧。

编辑:hfy

-

FPGA

+关注

关注

1629文章

21729浏览量

602978 -

DDR

+关注

关注

11文章

712浏览量

65318 -

Xilinx

+关注

关注

71文章

2167浏览量

121299 -

MIG

+关注

关注

0文章

12浏览量

10979

发布评论请先 登录

相关推荐

mig生成的DDR的IP核的问题

xilinx MIG DDR2使用问题

例说FPGA连载41:DDR控制器集成与读写测试之DDR2 IP核接口描述

MIG IP核管脚分配问题

使用user design文件夹下的.v文件,如果编写顶层读写控制程序对mig-39-2.v进行例化,如何操作才能使用sim_tb_top.v仿真文件?

如何调试Zynq UltraScale+ MPSoC VCU DDR控制器

Xilinx DDR2 IP 核控制器设计方案介绍与实现

DDR3 SDRAM的IP核调取流程

Xilinx DDR控制器MIG IP核的例化及仿真

Xilinx DDR控制器MIG IP核的例化及仿真

评论