0 引言

随着视频显示技术的发展,视频信号从之前的标清发展到高清,再发展到全高清,其分辨越来越高,数据量也成倍增加,这就推进了显示接口技术的高速发展,显示接口技术经过了一个从vwin 到数字、从并行到串行、低速到高速的发展过程[1-3]。HDMI接口是最新的高清晰度多媒体接口,与DVI接口相比,其尺寸更小,带宽更大,传输距离更远,支持的分辨率更高,不仅能够传输视频信号,还能传输音频信号,且具备版权保护功能[4]。HDMI接口已成为液晶显示器、平板带脑、笔记本电脑等设备的标准接口之一,得到了广泛应用[5-6]。本系统中不仅实现了标准HDMI接口电路及其控制,并且还提供全高清视频数据源,选用500万像素级别CMOS摄像头OV5640,输出视频信号分辨率可达2K级别,支持多种数据格式输出。为了解决由于视频数据缓存速率和容量不足导致的拖影问题,该系统选用容量为4 Gbit的DDR3 SDRAM作为换缓存介质,通过Xilinx公司的MIG IP和对其进行控制,再结合乒乓操作,能有效解决高数大容量数据的缓存问题,使显示质量更高。本系统实现了全高清视频信号的采集及高质量显示,其能应用到多种领域,包括军用监控领域、多媒体领域、医用领域等。

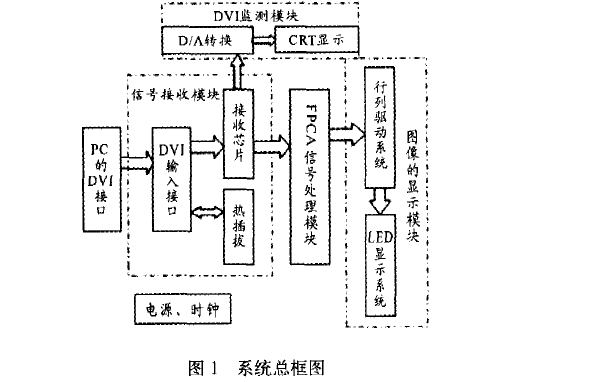

1 方案设计

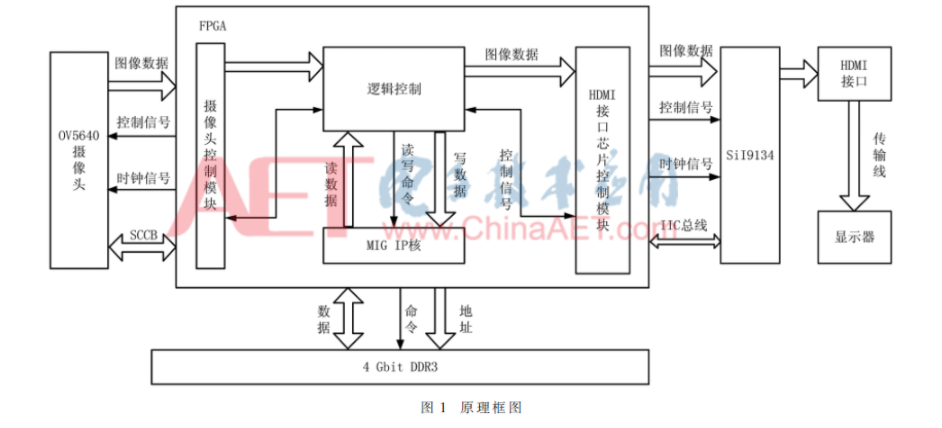

此视频采集显示系统原理框图如图1所示,该系统主要包括视频采集模块、FPGA主控模块、数据缓存模块和HDMI接口电路。视频采集模块提供全高清视频数据源,在其开始采集之前需要FPGA主控模块通过SCCB(Serial Camera Control Bus)总线将摄像头配置信息发送到摄像头中的寄存器;FPGA主控模块是此系统的控制核心,其控制着摄像头、DDR3-SDRAM、HDMI接口芯片以及视频数据流;数据缓存模块以一块4 Gbit容量的DDR3-SDRAM作为缓存介质,能有效解决高速大容量数据的缓存问题;HDMI接口电路主要包含一块HDMI接口芯片,其作用是实现视频数据的并串转换;最后,串行视频数据通过HDMI传输线传输到支持HDMI接口的显示器上,就能实时显示全高清视频图像。

2.1 视频采集模块

视频采集模块选用OmniVision公司OV5640摄像头,其为500万像素级别CMOS图像传感器,支持分辨率可达2K级别,能输出多种图像格式数据,且支持多种自适应调节功能。此CMOS图像传感器支持DVP和MIPI两种数据接口,本系统中选择DVP接口。在主控模块获取数据之前需要通过SCCB总线将传感器寄存器信息配置给传感器[7-8]。本系统中CMOS图像传感器图像数据输出格式配置为RGB24,视频分辨率配置为1 920×1 080(全高清),视频帧率配置为30 f/s,此模块还包括数字和模拟供电电路。

2.2 FPGA主控模块

系统控制核心选用的芯片是Xilinx公司Spartan6系列芯片XC6SLX45,第六代Spartan系列产品Spartan6 FPGA基于公认的低功耗45 nm、9-金属铜层、双栅极氧化层工艺技术,提供了高级功耗管理技术、150 000个逻辑单元、硬核DRAM存储器以及多种IP等,是Xlinx公司应用最为广泛、技术非常成熟的一个FPGA系列[9-11]。FPGA主控模块主要完成摄像头的配置及视频数据获取、DDR3-SDRAM数据的存取以及HDMI接口芯片的配置以及视频数据发送,其硬件电路还包括供电电路、复位电路、晶振电路、下载电路和配置SPI Flash电路。

2.3 数据缓存模块

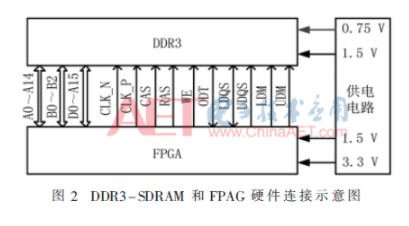

为了解决高速大容量视频数据的缓存问题,此系统选用Micron公司4 Gbit容量DDR3-SDRAM存储芯片MT41J256M16HA-125作为缓存介质,其与FPAG的硬件连接示意图如图2所示。A0~A14为地址总线,B0~B3为Bank地址,FPGA通过控制地址总线和Bank地址就能控制数据在DDR3-SDRAM中的存储位置;D0~D15为数据总线,与FPGA并行连接;CLK-N和CLK-P为差分时钟输入端口,本系统中设定时钟频率为312.5 MHz;FPGA通过列地址选择信号(CAS)、行地址选择信号(RAS)、写使能信号(WE)对DDR3-SDRAM进行读写控制,通过控制ODT使能片内电阻优化性能来防止数据线中断反射[12];DQS为DDR3-SDRAM与控制器之间的同步信号,其为双向信号,当写入数据时,其由控制器发出,当读取数据时,其由存储器发出;DM为数据屏蔽信号[13]。由于Spartan6系列FPAG只有Bank1和Bank3有MCB硬核,在本系统中选择FPGA中Bank3与DDR3-SDRAM连接,端口电压标准为1.5 V,且在FPAG UCF中,需要设定IO标准为SSTL15_II。

2.4 HDMI接口模块

本系统中选用SiI9134作为HDMI输出接口芯片,其和FPAG的硬件连接关系如图3所示。在芯片工作之前,需要通过I2C(SCL、SDA)总线将寄存器信息配置到芯片里,配置过程中频率为100 kHz,数据输入格式配置为RGB24,视频输出分辨率配置为1 920×1 080;CLK为视频数据同步时钟,此芯片1080p视频格式的时钟为148.5 MHz,DE为数据有效信号,高电平有效;HS、VS分别为行同步信号和场同步信号;D[23:0]为RGB24数据输入总线,从上到下依次为R、G、B分量数据总线,为了支持其他视频数据格式,SiI9134的总线宽度为36 bit,此系统中只使用24 bit,其余的数据总线引脚接地;SiI9134支持多种数字音频信号输入接口,包括S/PDIF、I2S等,本系统中不使用音频接口。RGB24格式视频数据经SiI9134编码后,转换成串行数据后通过连接器和传输线将数据发送给显示器,最终显示出全高清视频。

3 控制逻辑设计

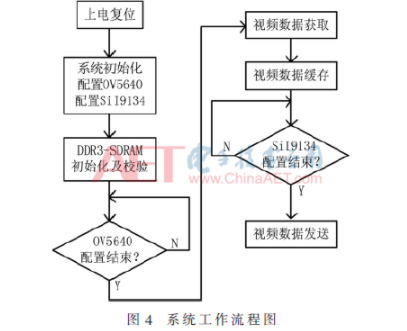

本系统控制逻辑设计中,包括OV5640配置及视频数据获取逻辑、DDR3-SDRAM数据存取控制逻辑、SiI9134配置及视频数据发送逻辑。系统通过DVP口接收RGB24格式的视频数据,然后将视频数据分区域存入DDR3-SDRAM中,再将视频数据从中读出发送给HDMI接口芯片供显示屏显示。系统工作流程如图4所示,上电后系统先进行复位操作,然后进入初始化状态,系统给OV5640和SiI9134发送配置信息,DDR3-SDRAM也开始进入初始化和校验过程。所有初始化工作完成后,系统判断OV5640是否配置结束,如果配置结束,系统将获取视频数据,并将其存入DDR3-SDRAM中。当缓存区有数据且SiI9134配置结束后,系统将缓存区的视频数据读出发送给SiI9134。

3.1 视频采集控制部分

OV5640对上电的时序有一定的要求,所以满足此上电时序的模块是必不可少的,完成初始化后,先确定OV5640的工作模式,通过SCCB总线就能完成,此系统中配置了303个寄存器;待OV5640配置完成和DDR3-SDRAM初始化和校准完成后,就可获取视频数据;控制OV5640需要先提供一个系统时钟XVCLK,为192 MHz,然后识别像素输出时钟(PCLK)、场同步信号(VSYNC)、行同步信号(HREF)来获取数据。场同步信号下降沿表示一帧数据的开始,行同步信号为高电平时为有效数据输出,在场同步信号低电平之间,行同步信号会出现1 080次高电平,代表一帧数据有1 080行数据;在行同步信号处于高电平期间会持续1 920个像素输出时钟,代表每一行有1 920个像素点。

3.2 DDR3-SDRAM缓存控制部分

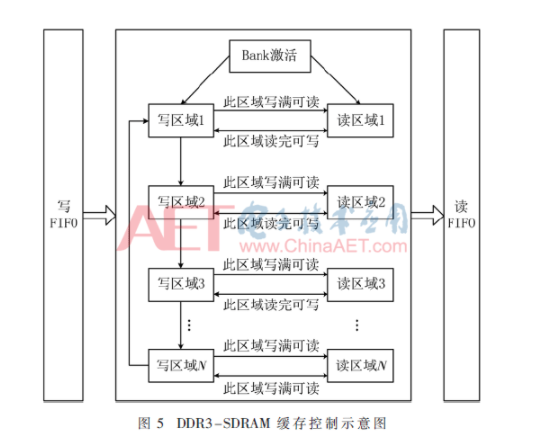

DDR3-SDRAM数据的存取使用了Spartan6系列FPGA提供的MIG IP核,同时也需要MCB硬核与外部的SDRAM芯片进行数据交换。在Xilinx编译环境ISE中生成SDRAM控制器后,就可运用MIG IP核用户接口进行数据存取,本系统中MIG IP核配置成两个位宽为64 bit的双向端口,一个端口用于写数据,一个端口用于读数据。其工作状态示意图如图5所示,在MIG IP核的前端和后端分别加入一个写数据FIFO和读数据FIFO,对于调用此缓存模块的逻辑来说,就相当于一个大容量的FIFO。在MIG IP核内部,采用乒乓操作的方式来提高缓存效率,在缓存的过程中,将4 Gbit容量的存储区域分为N个区域,每个区域的容量为一帧视频数据的容量,在写入过程中,先将数据写入第1区域,第1区域写满后开始写下一区域(为第2区域,写下一区域时确保该区域数据为空),此时就可以读取第1区域的数据,第1区域读完再读下一区域(为第2区域,在读下一区域时确保该区域数据已满)数据,依此顺序循环读写,完成乒乓操作。这种缓存方式可极大提高视频数据缓存效率,有效解决高速大容量数据的缓存问题,一帧视频数据连续且不会出现数据交叉的情况(地址不会交叉),避免了视频显示的拖影现象。

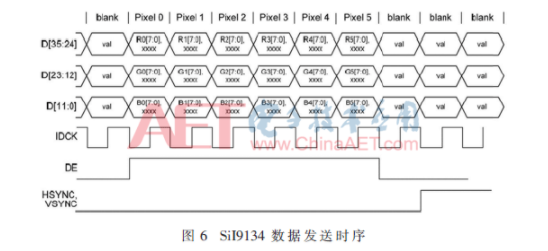

3.3 HDMI接口控制部分

在HDMI工作之前,需要通过I2C总线给寄存器配置数据,数据格式配置为RGB24,分辨率为1 920×1 080,视频帧率为30 f/s。配置完成后,缓存区一数据满时,就可读取视频数据按照特定时序发送给SiI9134,SiI9134数据发送时序如图6所示,行同步信号的下降沿代表一帧视频数据的开始,上升沿代表一帧数据的结束,当一行数据发送完后开始发送下一行数据,当一帧数据最后一行发送完成后再发送下一帧画面的第一行数据。以此重复循环发送数据,DE为数据有效信号,高电平有效。

4 测试结果

硬件电路电气性能测试完成后,开始进行整体性能的测试,在整体性能测试之前,还需要对FPGA程序进行功能仿真和时序仿真,再对各个功能模块分别进行测试,确保代码准确无误。

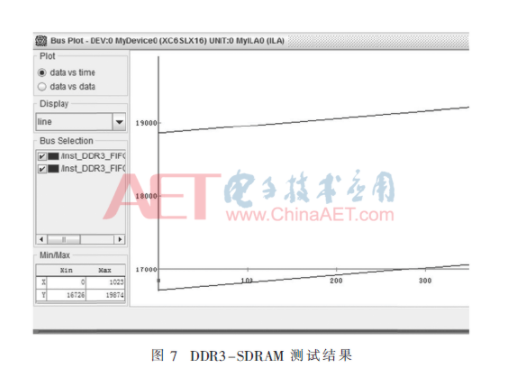

4.1 DDR3-SDRAM测试

利用Xilinx公司提供的ChipScope Pro工具对DDR3-SDRAM代码进行测试,测试过程中,由系统内部产生递增数写入到写数据FIFO中,然后从读数据FIFO中读取数据,将写入的数据和读出的数据通过ChipScope Pro工具抓取,再对抓取结果绘出波形并进行比对,测试结果如图7所示。从测试结果来看,读写速度快且没有出现数据乱码情况,符合系统要求。

4.2 HDMI接口测试

HDMI接口模块测试结果如图8所示,测试过程中,视频数据源由系统内部产生,包括三基色、棋盘格、彩色条等数据,最后将串行数据发送到支持1080p分辨率的显示器上。从测试结果来看,显示效果符合要求。

4.3 系统整体测试

图9所示为系统整体测试结果,测试过程中,视频数据源为摄像头采集的视频数据,数据经过DDR3-SDRAM缓存,再发送到HDMI接口芯片,然后通过HDMI连接器和传输线将差分数据传输给显示器。从测试结果来看,如图9(a)所示,视频显示清晰完整;当摄像头移动时,如图9(b)所示,图像显示无拖影现象,证明通过DDR3-SDRAM高效缓存和乒乓操作结合的方式,能够有效解决高速大容量数据的缓存问题。

5 结论

为了满足人们对视频显示质量的需求,本系统设计了一种全高清视频采集显示系统,系统以OminiVision公司的500万像素级别CMOS图像传感器OV5640为前端采集摄像头,以Xilinx公司Spartan6系列FPGA作为主控芯片,以4 Gbit容量DDR3-SDRAM作为缓存芯片,再结合MCB硬核、MIG IP核以及乒乓操作,实现视频数据的高效缓存;同时以Silion Image公司的SiI9134为HDMI芯片,能有效支持全高清视频。系统能够稳定采集显示全高清视频,显示质量高且无拖影现象,该系统可应用于军用监控系统、民用多媒体系统以及医学等领域。

参考文献

[1] 黄庆敏,罗键.HDMI接口标准及应用设计[J].电视技术,2007(2):32-34.

[2] 顾海峰,夏宁,吴杰.一种基于CH7301C的显示接口电路设计[J].信息化研究,2012,38(6):30-34.

[3] 刘佳.数字图像高速采集和传输技术的研究与实现[D].天津:天津大学,2014.

[4] 李先友,赵曙光,段永成,等.基于FPGA的实时MIPI CSI-2图像采集与处理系统[J].电子技术应用,2019,45(1):97-100.

[5] 潘磊,葛中芹,庄建军,等.基于FPGA的HDMI视频流图像处理的系统设计[J].实验室研究与探索,2015,34(10):76-80.

[6] 向梓豪,陆安江.基于FPGA的HDMI多模式显示模块设计[J].电子技术应用,2017,43(12):48-51.

[7] 陈一波,杨玉华,王红亮,等.基于DDR3-SDRAM的图像采集与显示系统[J].电子器件,2017,40(3):702-707.

[8] 周浩,王浩全,任时磊.基于FPGA和NAND Flash的便携式信号采集系统设计[J].电子技术应用,2018,44(9):82-86.

[9] 林谋锦,林子威.DVI接口与HDMI接口的比较[J].中国有线电视,2005(6):581-582.

[10] 杨帆,张皓,马新文,等.基于FPGA的图像处理系统[J].华中科技大学学报(自然科学版),2015,43(2):119-123.

[11] 宋海吒,唐立军,谢新辉.基于FPGA和OV7620的图像采集及VGA显示[J].电视技术,2011,35(5):45-47.

[12] 李华.基于FPGA的高精度图像采集系统设计[J].电子器件,2014,37(5):840-843.

[13] 潘明,陈元枝,李强.基于FPGA的图像采集系统的设计[J].国外电子测量技术,2012,31(3):58-61.

编辑:hfy

-

FPGA

+关注

关注

1629文章

21729浏览量

602977 -

HDMI

+关注

关注

32文章

1694浏览量

151858 -

SDRAM

+关注

关注

7文章

423浏览量

55204 -

显示技术

+关注

关注

13文章

1048浏览量

73102

发布评论请先 登录

相关推荐

机载高清视频处理模块的设计方案

基于PCI Express实时视频采集系统的设计

基于FPGA的视频传输流发送系统设计方案

基于FPGA的视频采集需要实施显示和视频数据存储的问题

基于Xilinx FPGA的视频图像采集系统

基于FPGA的全高清视频采集显示系统设计方案

基于FPGA的全高清视频采集显示系统设计方案

评论