上一期,我们重点学习了ZYNQ的PL开发,本期我们侧重于进行PS开发的学习。我们将在 VIVADO 开发环境下搭建 ARM+FPGA 的系统架构,并在 SDK 中编译软件实现软硬件联合开发。

本部分的学习,我们依旧借助得力的助手与伙伴——PYNQ_z2来完成。

一. 实验目的

1. 点亮开发板右下角三个灯

2. 输出“Hello,World!”

二. 实验要求

1. 在 VIVADO 中编译 bit 文件;

2. 在 SDK 中编译 elf 文件并将 FPGA 的 bit 文件和 ARM 处理器 的 elf 文件下载到开发板中

三. 实验步骤

1. 启动 VIVADO

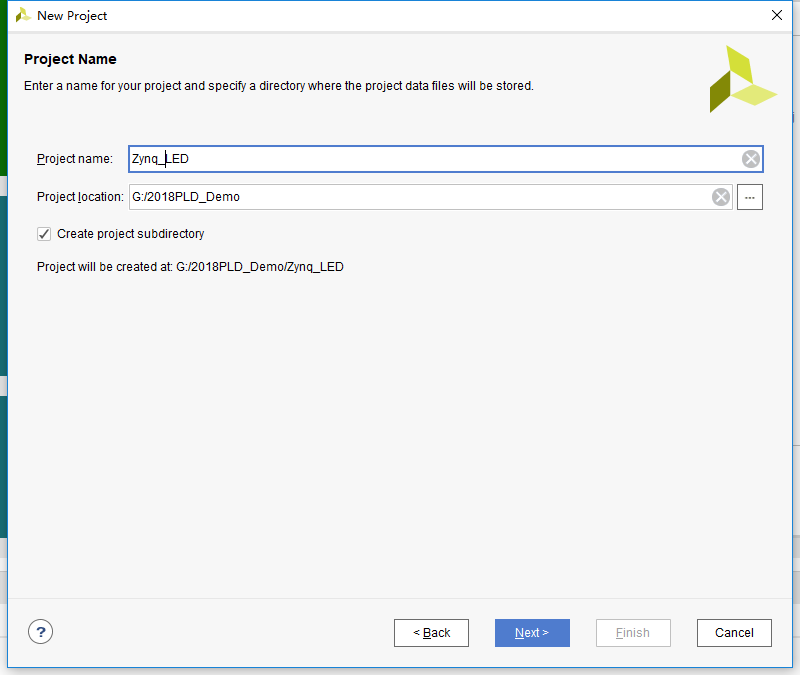

2. 在 File 菜单中选择 New Project 选项启动项目向导。填写所要新建的工程名,然后点击 Next

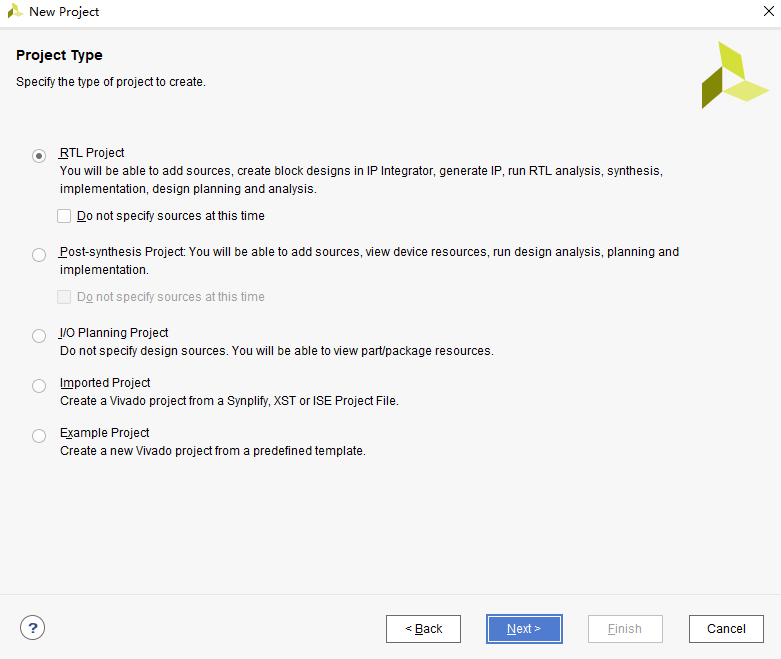

3. 在 File 选择项目类型

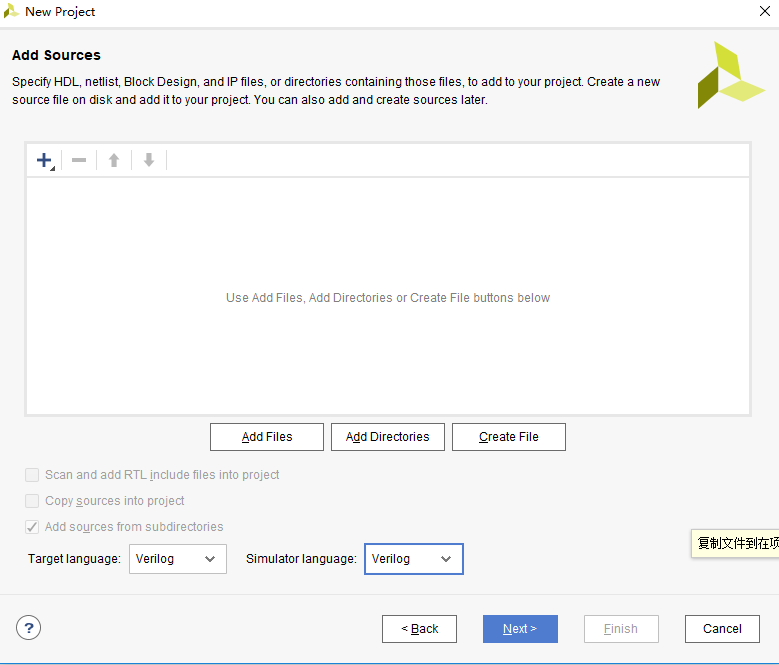

4. 此处默认没有可以添加的源文件,并且设置编程语言和仿真语言均设置为 Verilog。点击 Next

5. 没有可以添加的 IP,所以不添加 IP,直接点击 Next

6. 没有可以添加的约束文件,所以不添加,直接点击 Next

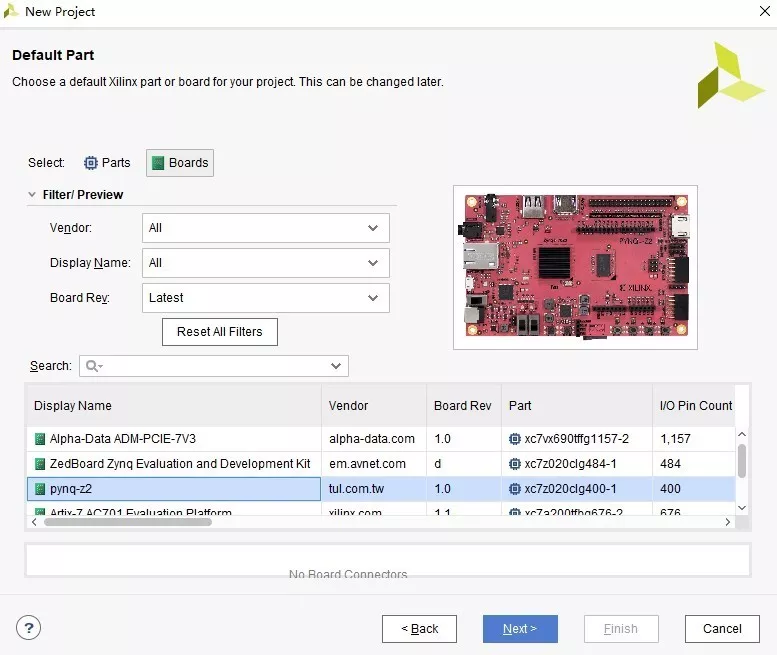

7. 器件的选择是和实验平台的硬件相关的,根据我们的实验开发板,它使用的是 Pynq 的器件,找到相应的器件

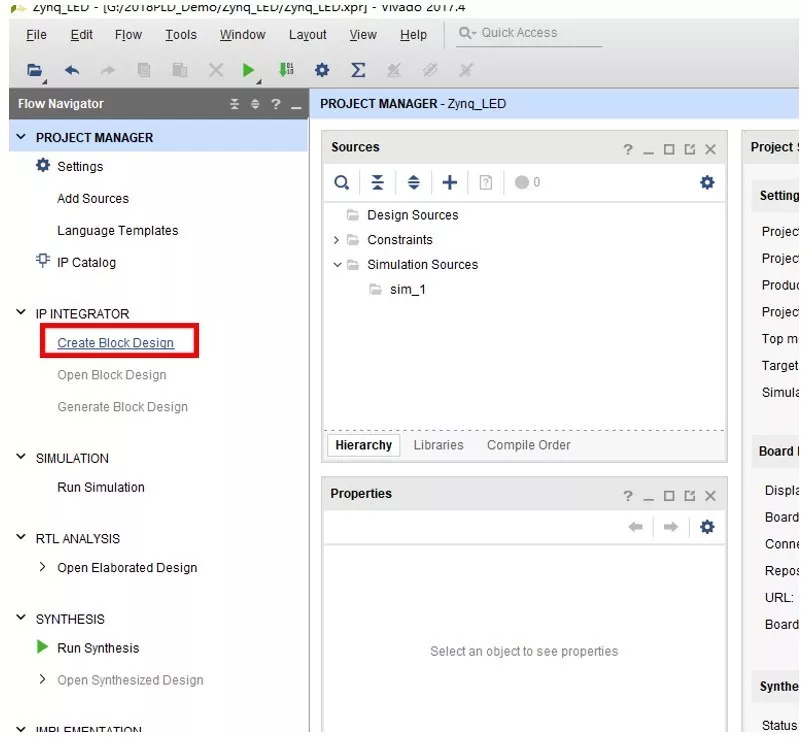

8. 创建 Block Design

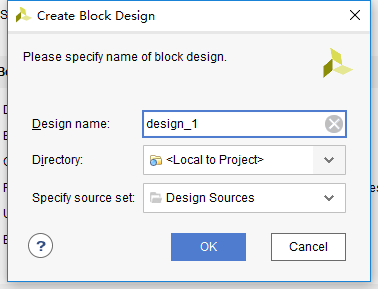

9. 输入 name,然后 OK

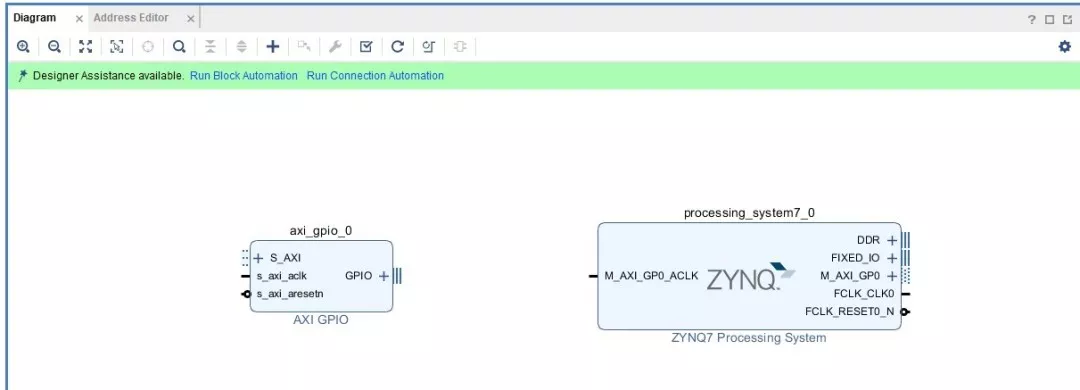

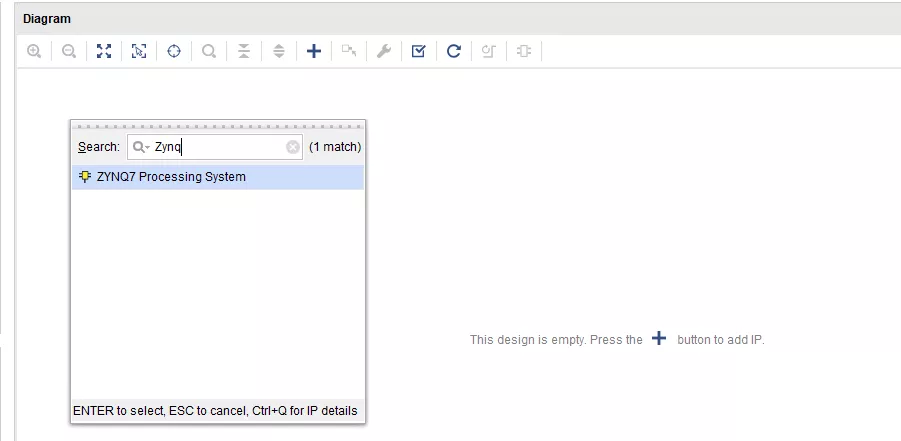

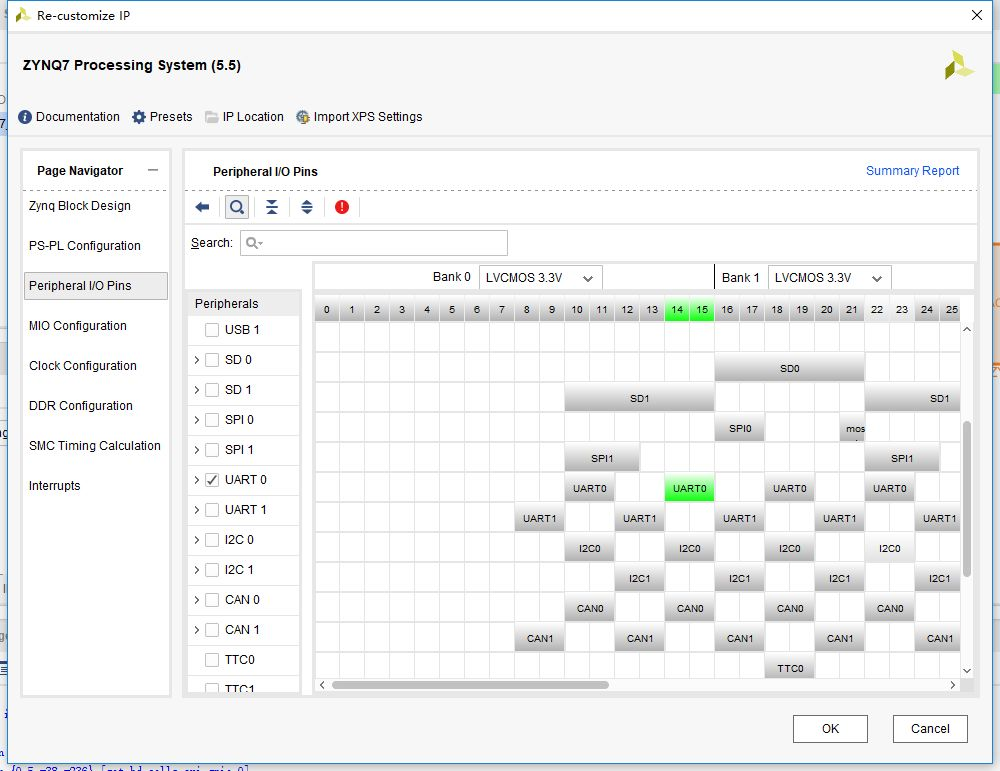

10. 选择 add IP,输入 zynq

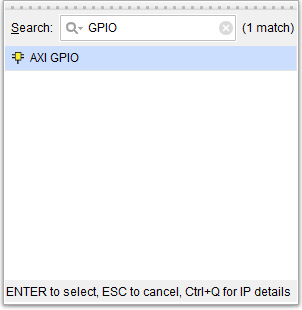

11. 再次添加 IP,输入 GPIO

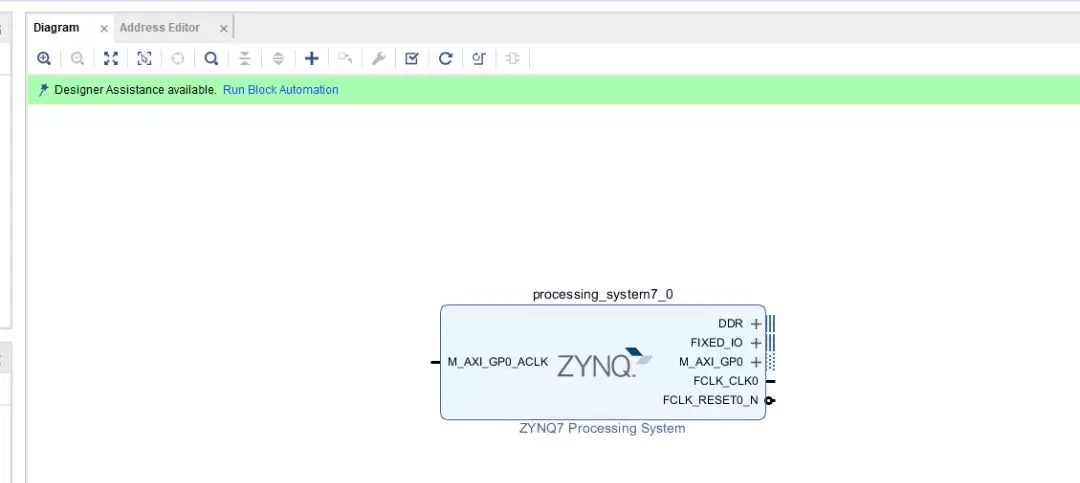

12. 双击 Zynq 模块,勾选上 UART0

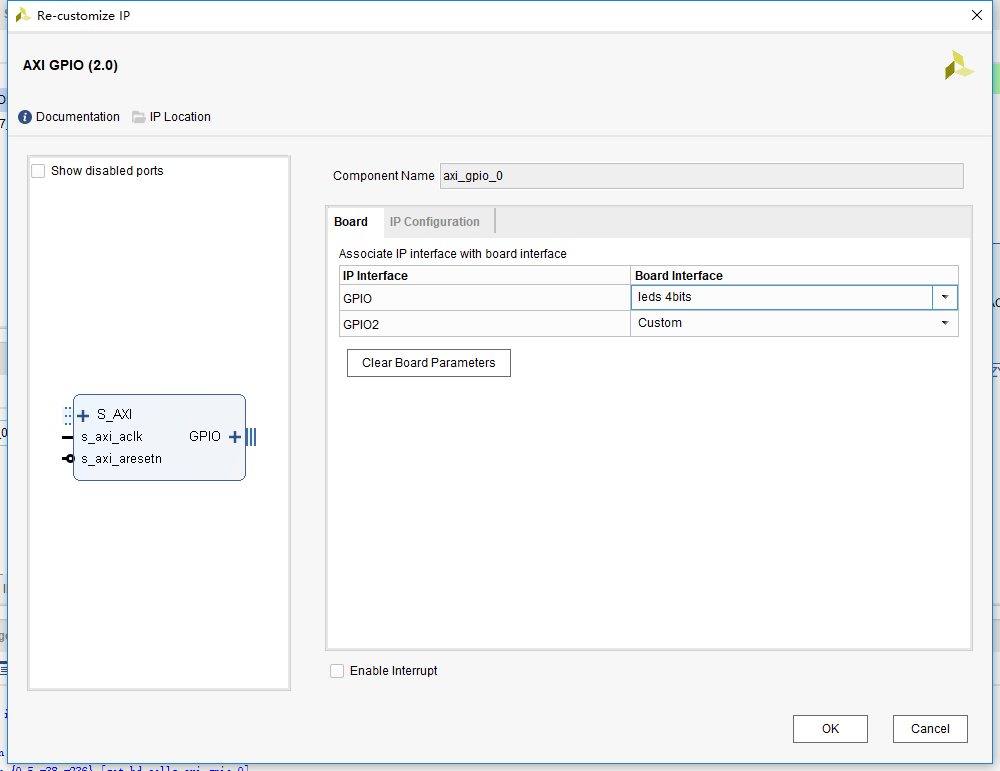

13. 双击 GPIO

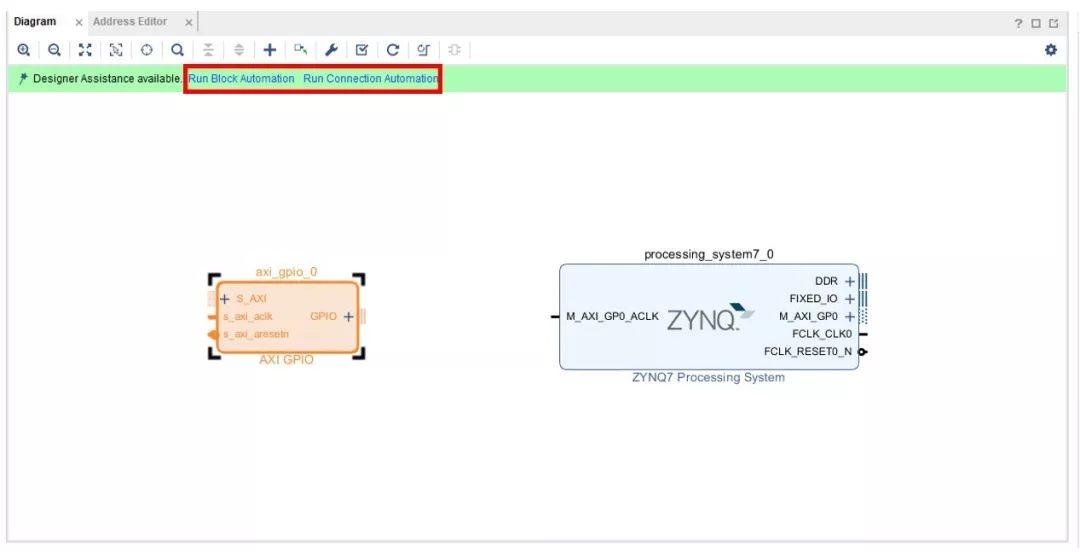

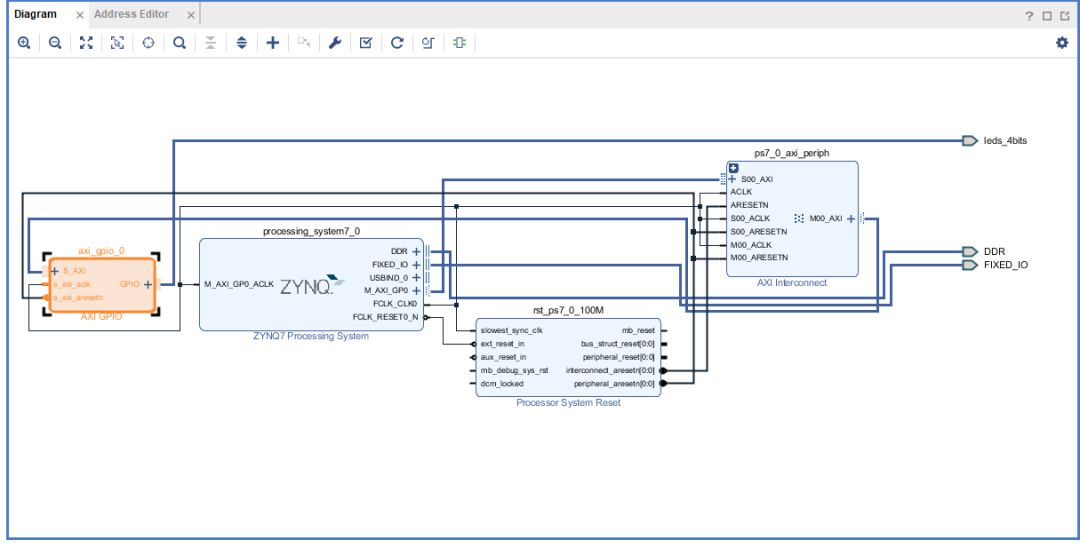

14. 分别点击Run Block Automation 和 Run Connection Automation

15. 勾选所有候选,然后点 ok

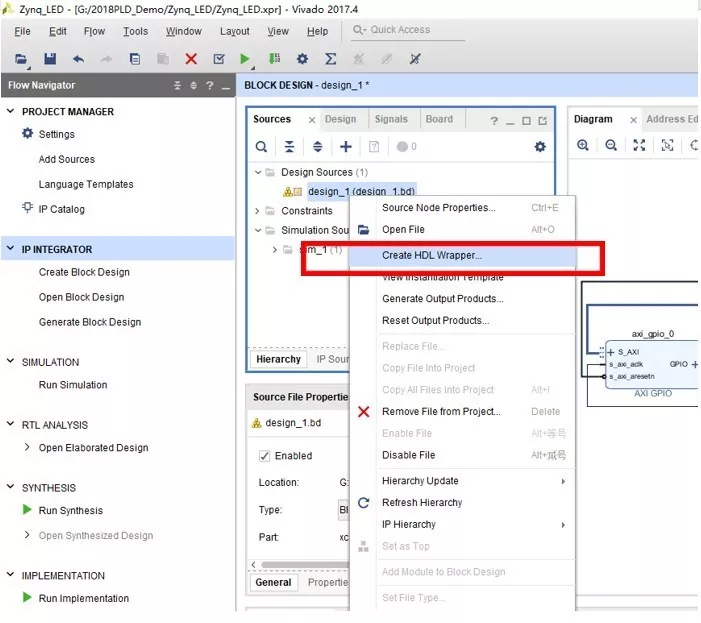

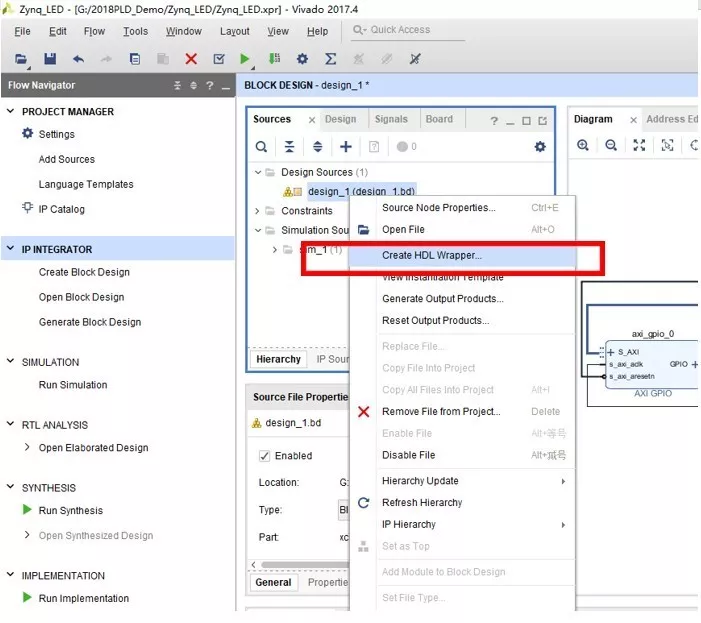

16. 右击 design_1.bd,create HDL Wrapper

17. 选择默认第二项,点击 OK

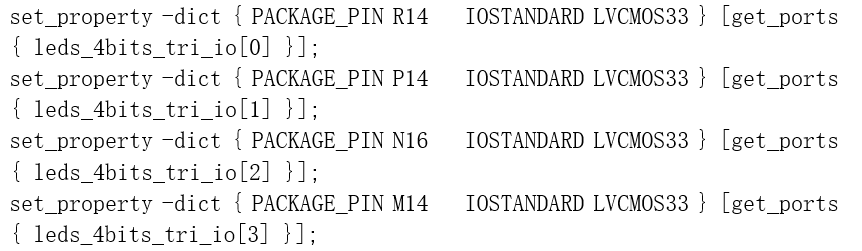

18. 添加引脚约束文件

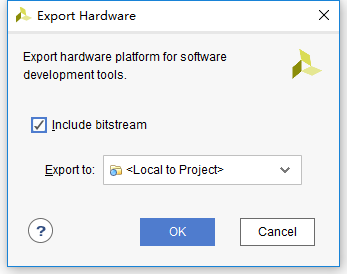

19. 然后直接点击 Generat Bitstream,等待几分钟,编译完成之后,点击工具 栏的 File→Export->Export Hardware

20. 勾选 Include bitstream,点击 OK

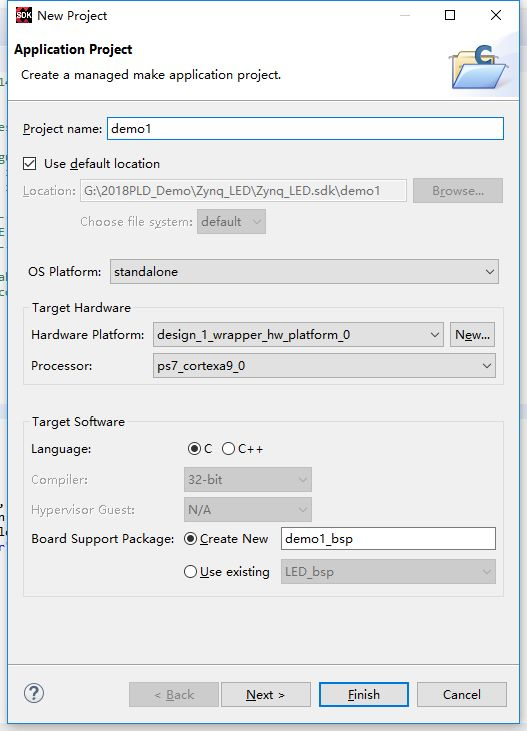

21. 点击工具栏的 File→lauch SDK,等待 SDK 启动完成之后,新建工程。

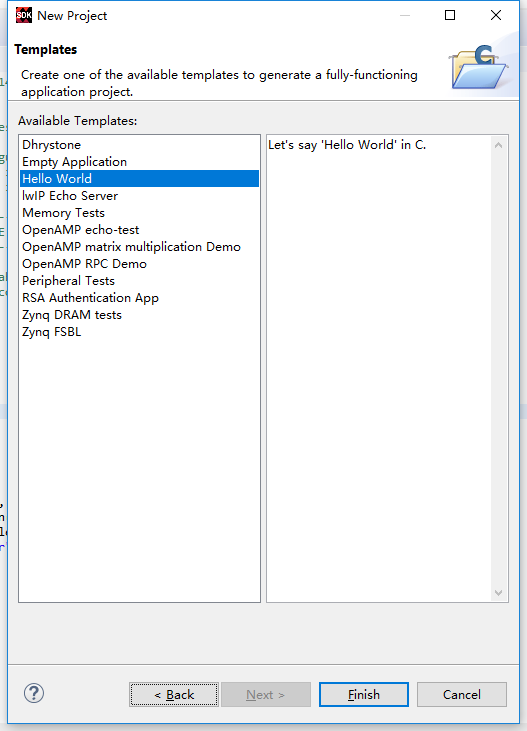

22. 点击 NEXT,选择工程类型

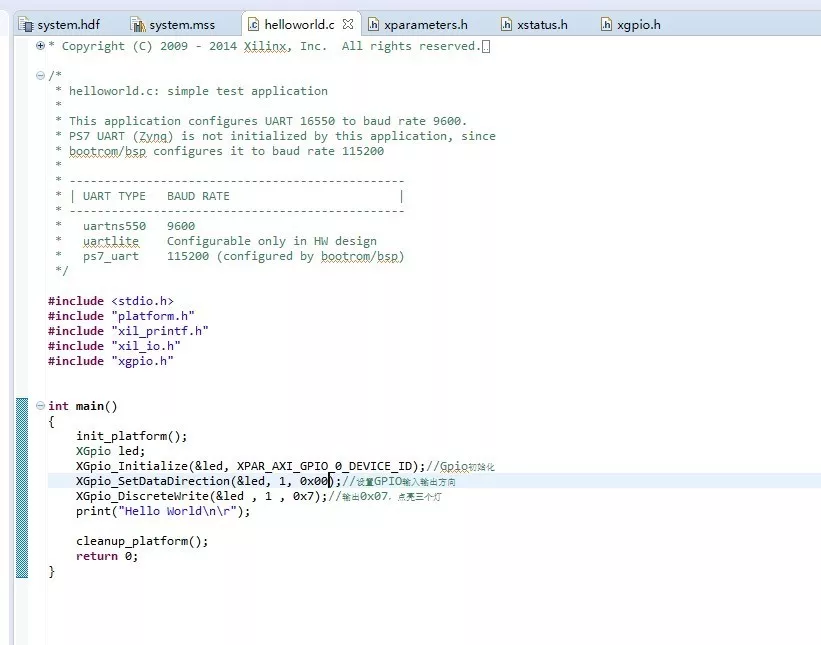

23. 点开 HelloWorld.c,输入如下代码:

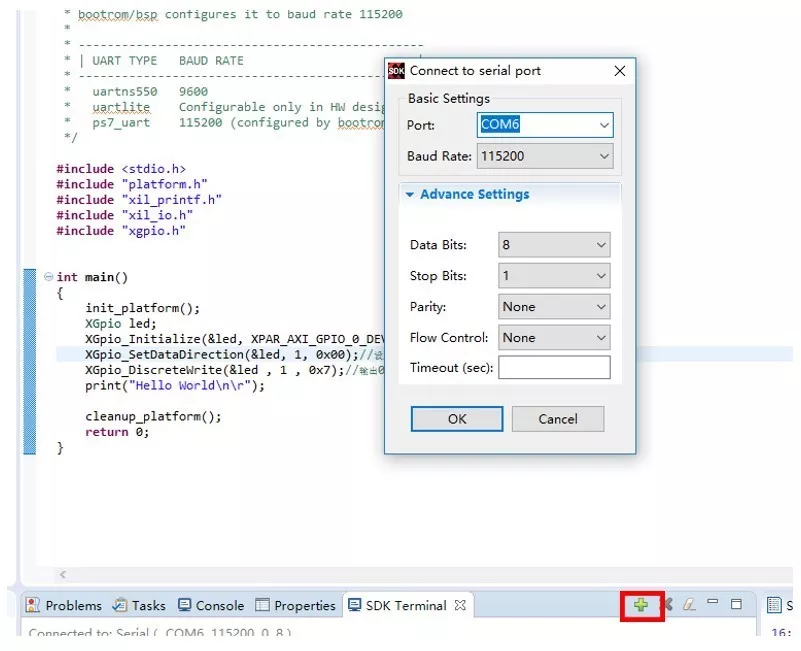

25. 连接串口,com 号在个人电脑的设备管理器中可以查看

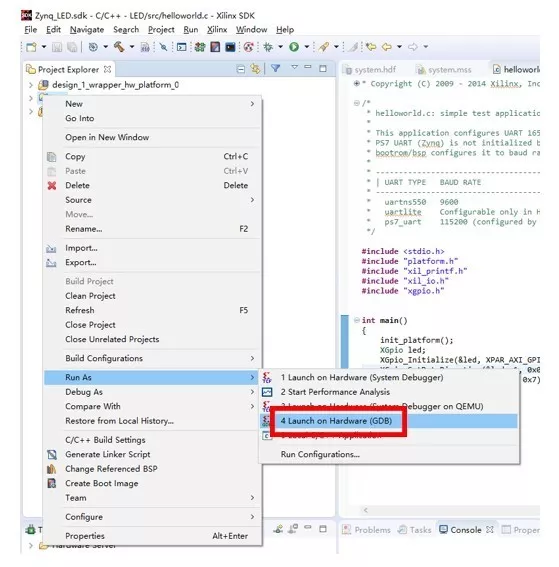

26. 右击工程目录,烧写 C 程序

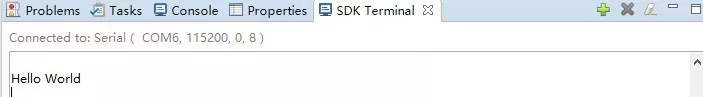

27. 开发板右下角三个灯点亮,输出如下:

编辑:hfy

-

FPGA

+关注

关注

1629文章

21729浏览量

602954 -

ARM

+关注

关注

134文章

9083浏览量

367369 -

Zynq

+关注

关注

10文章

609浏览量

47174 -

Vivado

+关注

关注

19文章

812浏览量

66470

发布评论请先 登录

相关推荐

单片机软硬件联合仿真解决方案

基于FPGA的以太网系统软硬件实现方案

基于FPGA的以太网系统软硬件实现方案

基于Altera FPGA的软硬件协同仿真方法介绍

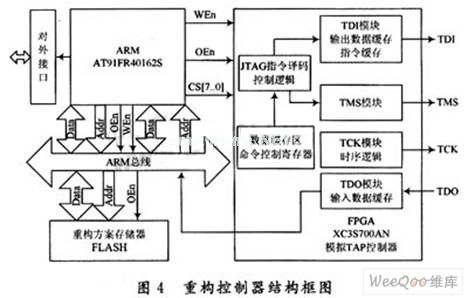

基于ARM+FPGA的重构控制器设计

利用FPGA软硬件协同系统验证SoC系统的过程和方法

基于FPGA的软硬件协同测试设计影响因素分析与设计实现

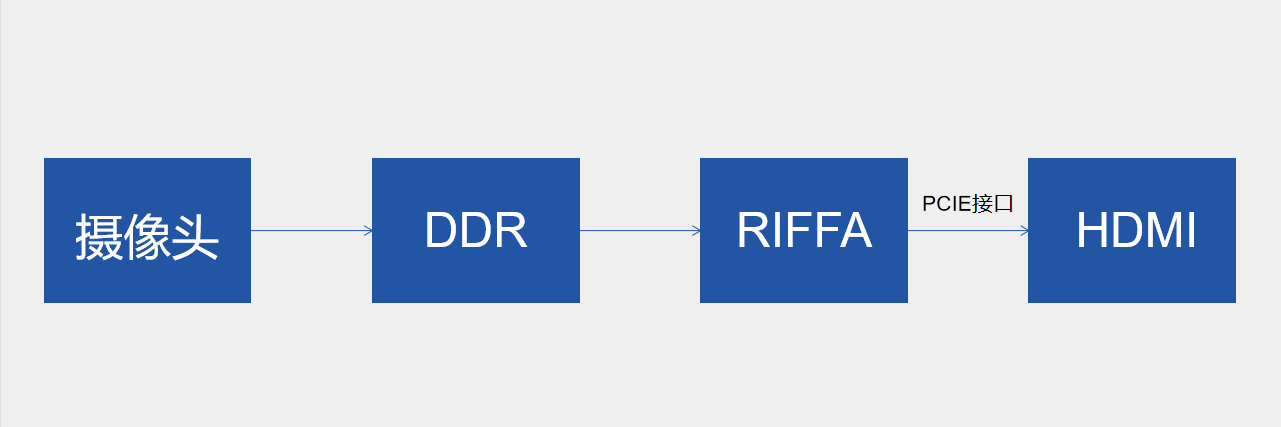

米尔ARM+FPGA架构开发板PCIE2SCREEN示例分析与测试

基于VIVADO搭建ARM+FPGA系统架构实现软硬件联合开发

基于VIVADO搭建ARM+FPGA系统架构实现软硬件联合开发

评论