你知道如何借助Cyclone 10 GX ATX PLL refclk切换实施功能vwin 吗?嵌入式流转换器实施ATX PLL重配置和通道重配置以及实施ATX PLL和通道再校准呢?想学啊?我(视频)教你啊。

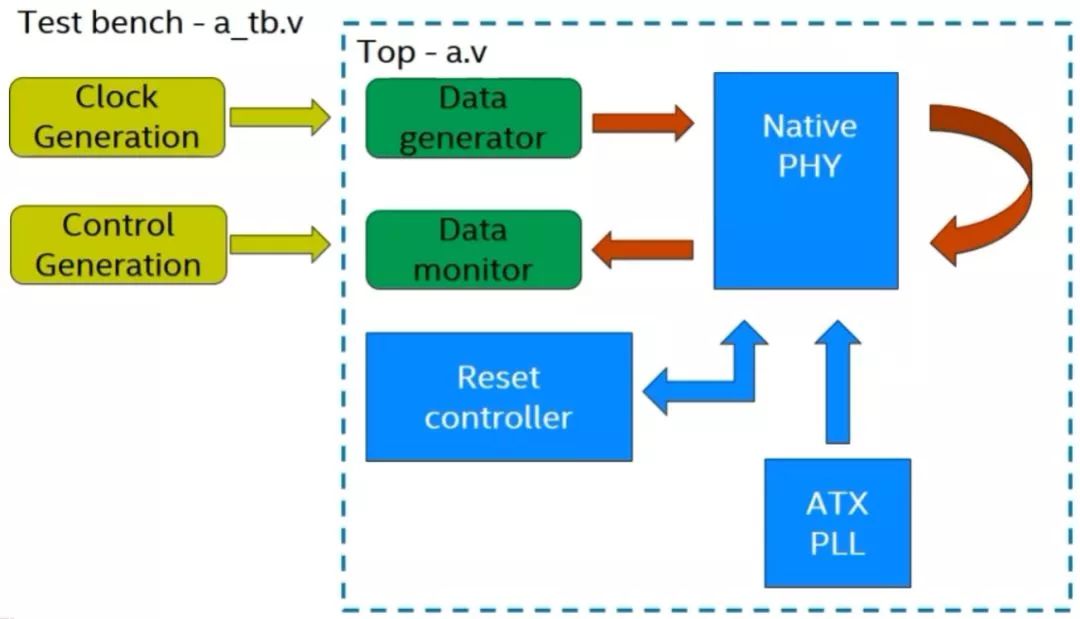

设计中的实例包括:Native PHY、TX PLL、重置控制器,数据和时钟生成逻辑等。两个refclk用于支持,无法通过TX本地除法器实现的两个不同数据速率。125MHz用于2Gbps,150MHz用于1.2Gbps。

在模拟开始时,收发器以2Gbps的数据速率运行,然后使用ATX PLL refclk切换动态重配置,重新配置为1.2Gbps。ATX PLL refclk切换通过寄存器写操作实施,接着使用嵌入式流转换器进行ATX PLL重配置和再校准,然后就可以实施CDR refclk切换、通道重配置和再校准了。

温馨提示

在上面的视频中有实施ATX PLL refclk切换的高级步骤,详情见视频。

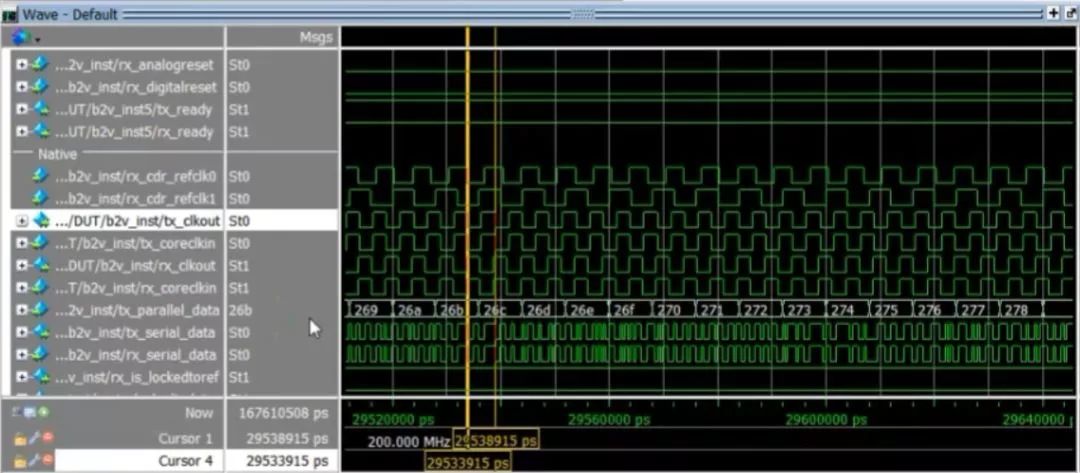

在最后的运行模拟示例中,我们可以看到增量数据从TX发送至RX。在启动过程中,收发器通道的运行速率为2Gbps。PCS内核宽度为10比特时,tx_clkout频率为200MHz。在实施ATX PLL refclk切换和通道重配置后,收发器通道的运行速率变为1.2Gbps。Tx_clkout频率将变为120MHz。这显示ATX PLL refclk切换和通道重配置已成功完成。

责任编辑:xj

原文标题:参考时钟切换动态重配置不会玩儿?我教你啊

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

-

时钟

+关注

关注

10文章

1733浏览量

131445 -

Cyclone

+关注

关注

0文章

54浏览量

30093

原文标题:参考时钟切换动态重配置不会玩儿?我教你啊

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

config108读取config108寄存器的值时钟为000f,只是serdes_pll未锁定,为什么?

使用FPGA的LVDS_serdes模式驱动DP83867E,可以不使用PHY芯片上自带的SGMII_SCO(625MHz)的时钟吗?

锁相环PLL在无线电中的应用 锁相环PLL与模拟电路的结合

借助 MSPM0 精密模拟,轻松进行系统设计应用说明

atx电源标准尺寸是多少

ATX电源插座可以提供几种电压

atx电源分别提供什么和什么电压

atx电源的技术参数有哪些

atx电源接口定义及颜色定义

atx电源和matx电源哪个大

FPGA片内PLL电磁抗扰度的热应力效应研究与测试分析

如何借助Cyclone 10 GX ATX PLL refclk切换实施功能模拟

如何借助Cyclone 10 GX ATX PLL refclk切换实施功能模拟

评论