量子计算是未来信息技术发展的重要方向,在一些特定领域具有较大应用潜力。基于硅量子点的量子比特是实现通用量子计算最有前景的方案之一,具有较长的退相干时间和出色的CMOS制造工艺兼容性。目前,硅量子点量子计算正处在采用集成电路先进制造工艺实现量子点规模集成并进行量子比特扩展验证的关键研究阶段。

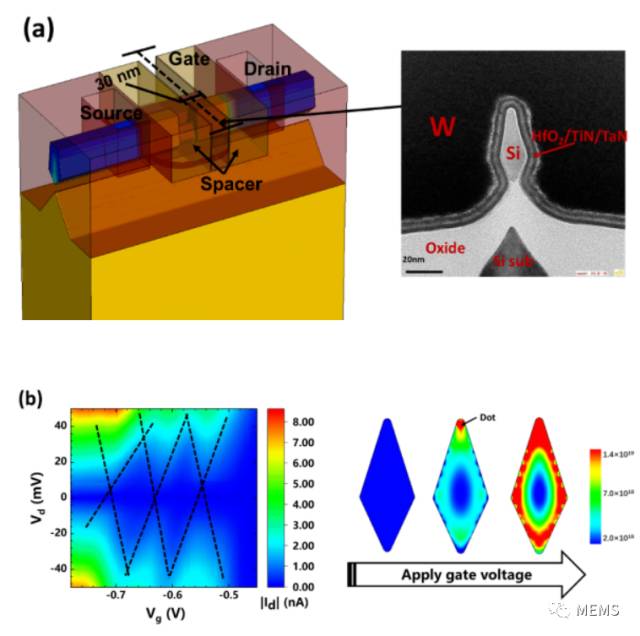

近期,中国科学院微电子研究所集成电路先导工艺研发中心研究员殷华湘带领的科研团队基于主流的体硅高κ/金属栅FinFET工艺,提出了一种利用拐角效应,在钻石形Fin沟道顶部尖端实现载流子局域化,并借助栅极两边侧墙的电势限制,构建量子点器件结构的方案。该器件在先导中心8吋工艺线研制成功,集成方案完全兼容主流通用的先进CMOS工艺。在制备过程中,研究人员先后优化了Fin刻蚀、浅槽隔离等关键工艺,;在高κ/金属栅后栅工艺中,利用氧化腐蚀的方法完成了衬底隔离的钻石形硅Fin沟道形貌修饰。在20 K低温电学测试中,该器件展示出明显的库伦振荡电流。研究人员通过分析库伦菱形稳定图,证明了该器件拥有较大的量子点充电能,具备在传统CMOS FinFET工艺中实现量子点规模化集成的潜力。

(a)器件结构示意图及沟道截面TEM分析;(b)库伦菱形稳定图及部分仿真分析

相关研究成果发表在《电气和电子工程师协会电子器件学报》(IEEE Transactions on Electron Devices,DOI: 10.1109/TED.2020.3039734)上,微电子所博士生顾杰为论文第一作者。殷华湘、微电子所副研究员张青竹为论文的通讯作者。研究工作得到科学技术部、国家自然科学基金委、中科院的支持。

责任编辑:lq

-

CMOS

+关注

关注

58文章

5710浏览量

235405 -

微电子

+关注

关注

18文章

380浏览量

41195 -

FinFET

+关注

关注

12文章

248浏览量

90208 -

量子计算

+关注

关注

4文章

1093浏览量

34941

原文标题:微电子所在基于先进FinFET工艺的硅量子器件研究中获进展

文章出处:【微信号:MEMSensor,微信公众号:MEMS】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

常见场效应管类型 场效应管的工作原理

高K金属栅极的结构、材料、优势以及工艺流程

当前主流的大模型对于底层推理芯片提出了哪些挑战

场效应管栅源极电压的影响因素

结型场效应管和金属氧化物场效应管的分类

高k金属栅(HKMG)工艺详解

碳纳米管晶体管兼容已有半导体制程工艺,解决碳纳米管均匀可控掺杂难题

基于主流的体硅高κ/金属栅FinFET工艺,提出了一种利用拐角效应

基于主流的体硅高κ/金属栅FinFET工艺,提出了一种利用拐角效应

评论