用户定义的原语

在前一章中,我们介绍了Verilog HDL提供的内置基本门。本章讲述Verilog HDL指定用户定义原语U D P的能力。

U D P的实例语句与基本门的实例语句完全相同,即 U D P实例语句的语法与基本门的实例语句语法一致。

6.1 UDP的定义

使用具有如下语法的U D P说明定义U D P。

p r i m i t i v e U D P _ n a m e (OutputName, List_of_inputs )

O u t p u t _ d e c l a r a t i o n

L i s t _ o f _ i n p u t _ d e c l a r a t i o n s

[R e g _ d e c l a r a t i o n]

[I n i t i a l _ s t a t e m e n t]

t a b l e

L i s t _ o f _ t a b e l _ e n t r i e s

e n d t a b l e

e n d p r i m i t i v e

U D P的定义不依赖于模块定义,因此出现在模块定义以外。也可以在单独的文本文件中

定义U D P。U D P只能有一个输出和一个或多个输入。第一个端口必须是输出端口。此外,输出可以取值0、1或x(不允许取z值)。输入中出现值z以x处理。U D P的行为以表的形式描述。在U D P中可以描述下面两类行为:

1) 组合电路

2) 时序电路(边沿触发和电平触发)

6.2 组合电路UDP

在组合电路U D P中,表规定了不同的输入组合和相对应的输出值。没有指定的任意组合输出为x。下面以2 - 1多路选择器为例加以说明。

p r i m i t i v e MUX2x1 (Z, Hab, Bay, Sel ) ;

o u t p u t Z;

i n p u t Hab,Bay, Sel;

t a b l e

// Hab Bay Sel : Z 注:本行仅作为注释。

0 ? 1 : 0 ;

1 ? 1 : 1 ;

? 0 0 : 0 ;

? 1 0 : 1 ;

0 0 x : 0 ;

1 1 x : 1 ;

e n d t a b l e

e n d p r i m i t i v e

字符?代表不必关心相应变量的具体值,即它可以是0、1或x。输入端口的次序必须与表中各项的次序匹配,即表中的第一列对应于原语端口队列的第一个输入 (例子中为 H a b),第二列是 B a y,第三列是 S e l。在多路选择器的表中没有输入组合 0 1x项(还有其它一些项 );在这种情况下,输出的缺省值为 x(对其它未定义的项也是如此 )。

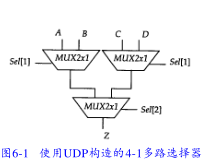

图6 - 1为使用2 - 1多路选择器原语组成的4 - 1多路选择器的示例。

如上例所示,在U D P实例中,总共可以指定 2个时延,这是由于U D P的输出可以取值0、1或x(无截止时延)。

6.3 时序电路UDP

在时序电路U D P中,使用1位寄存器描述内部状态。该寄存器的值是时序电路U D P的输出值。共有两种不同类型的时序电路U D P:一种vwin 电平触发行为;另一种模拟边沿触发行为。时序电路U D P使用寄存器当前值和输入值决定寄存器的下一状态 (和后继的输出)。

6.3.1 初始化状态寄存器

时序电路U D P的状态初始化可以使用带有一条过程赋值语句的初始化语句实现。形式如下:

i n i t i a l r e g _ n a m e = 0,1,or x;

初始化语句在U D P定义中出现。

6.3.2 电平触发的时序电路UDP

下面是D锁存器建模的电平触发的时序电路 U D P示例。只要时钟为低电平 0,数据就从输入传递到输出;否则输出值被锁存。

p r i m i t i v e Latch (Q, Clk, D) ;

o u t p u t Q;

r e g Q;

i n p u t Clk, D;

t a b l e

// Clk D Q(State) Q( n e x t )

0 1 : ? : 1 ;

0 0 : ? : 0 ;

1 ? : ? : - ;

e n d t a b l e

e n d p r i m i t i v e

“-”字符表示值“无变化”。注意U D P的状态存储在寄存器D中。

6.3.3 边沿触发的时序电路UDP

下例用边沿触发时序电路U D P为D边沿触发触发器建模。初始化语句用于初始化触发器的状态。

表项( 0 1 )表示从0转换到1,表项( 0 x )表示从0转换到x,表项( ? 0 )表示从任意值( 0 , 1或x)转换到0,表项( ? ? )表示任意转换。对任意未定义的转换,输出缺省为 x。

假定D _ E d g e _ F F为U D P定义,它现在就能够象基本门一样在模块中使用,如下面的 4位寄存器所示。

6.3.4 边沿触发和电平触发的混合行为

在同一个表中能够混合电平触发和边沿触发项。在这种情况下,边沿变化在电平触发之前处理,即电平触发项覆盖边沿触发项。下例是带异步清空的D触发器的U D P描述。

6.4 另一实例

下面是3位表决电路的U D P描述。如果输入向量中存在2个或更多的1,则输出为1。

6.5 表项汇总

原文标题:Verilog入门-用户定义的原语

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

Verilog

+关注

关注

28文章

1351浏览量

110073 -

HDL

+关注

关注

8文章

327浏览量

47374

原文标题:Verilog入门-用户定义的原语

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Verilog HDL指定用户定义原语UDP的能力介绍

Verilog HDL指定用户定义原语UDP的能力介绍

评论