在研制雷达系统时,常常需要应用频率合成技术来实现跳频信号源。频率合成是指从一个高稳定的参考频率,经过各种技术处理,生成一系列稳定的频率输出。现在应用最广的是锁相环(PLL)频率合成技术,它是通过变化PLL中的分频比N来实现输出频率的跳频的,但无法避免缩短环路锁定时间与提高频率分辨率的矛盾,因此很难同时满足高速和高精确度的要求。直接数字式频率合成(DDS)是近年发展起来的一种新的频率合成技术。它将先进的数字处理理论与方法引入频率合成领域,是继直接频率合成(DS)和间接频率合成(IS)之后的第三代频率合成技术。DDS的优点是:相对带宽很宽,频率转换时间极短(ns级),频率分辨率很高(可达μHz),全数字化结构便于集成,输出相位连续,频率、相位和幅度均可实现程控。因此能够与计算机紧密结合在一起,充分发挥软件的作用。在实际应用中,可以采用单片机来代替计算机对DDS芯片进行控制,实现合成频率的输出。因此在很短的时间内,DDS得到了飞速的发展和广泛的应用。

1 DDS的基本原理

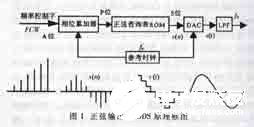

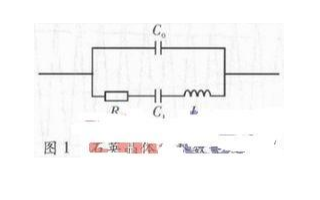

DDS技术是一种把一系列数字量形式的信号通过DAC转换成vwin 量形式的信号的合成技术。正弦输出的DDS的原理框图如图1所示。相位累加器在A位频率控制字FCW的控制下,以参考时钟频率fc为采样率,产生待合成信号相位的数字线性序列。将其高P位作为地址码,通过查询正弦表ROM,产生S位对应信号波形的数字序列S(n),再由数/模转换器(DAC)将其转化为阶梯模拟电压波形S(t),最后由低通滤波器LPF平滑为正弦波输出。

频率控制字FCW和时钟频率fc共同决定了DDS输出信号的频率f0,它们之间的关系满足:

f0=FCW/2Afc (1)

所以,在DDS结构及fc确定的前提下,通过FCW的控制就可以方便地控制输出频率f0。其频率分辨率为:

f=f0min=fc/2N (2)

按照Naquist准则,最高输出频率可达0.5fc。但考虑到实际低通滤波器的限制,最高输出频率一般为0.4fc。

由于DAC非线性作用的存在,使得查表所得的幅度序列从DAC的输入到输出要经过一个非线性过程。于是就会产生输出信号f0的谐波分量。又因为DDS是一个采样系统,所以这些谐波会以fc为周期搬移,即:

f=μfc±vf0 (3)

其中,u、v为任意整数。它们落到Nyquist带宽内就形成了有害的杂散频率,频率的位置可以确定,但幅度难以确定。所以在工程设计过程中要充分考虑输出频带,注意避免上述杂散分量落入其中,以此来获得较好的杂散指标。

2 DDS芯片介绍

DDS的诸多优点使它得到了非常广泛的应用。在数字调制方面,它可以用来实现FSK、QPSK、8PSK等调制。在雷达频率源方面,它可以实现多点、窄步长、高相噪的点频输出频率源以及线性调频输出频率源。在扩频通信方面,它可实现CDMA工作方式以及多种规律的跳频模式。

现在国外已经有非常成熟的DDS芯片。Qualcomm公司推出了DDS系列Q2220、Q2230、Q2334、Q2240、Q2368,其中Q2368的时钟频率为130MHz,分辨率为0.03Hz,杂散控制为-76dBc,变频时间为0.1μs;美国AD公司也相继推出了他们的DDS系列:AD9850、AD9851、可以实现线性调频的AD9852、两路正交输出的AD9854以及以DDS为核心的QPSK调制器AD9853、数字上变频器AD9856和AD9857。AD公司的产品全部内置了D/A变换器,称为Complete-DDS。其中AD9852时钟频率为300MHz,近端杂散抑制优于-80dBc,远端优于-48dBc,相位噪声为-148dBc/Hz@10kHz,频率跳变速度为130ns,频率分辨率为1μHz。

AD9852主要由48位的频率寄存器、48位相位累加器、正(余)弦查询表(带正交输出)、幅度调制寄存器、乘法器和12位D/A转换器构成。

AD9852可以实现单频、FSK、Chirp、FM Chirp、BPSK等多种输出形式。用其中的Chirp模式和FSK模式可以方便地实现跳频功能,满足雷达跳频系统的要求。使用时只要初始化DDS,设定跳频持续时间和跳频间隔时间即可实现自动跳频。这比以往的DDS芯片如AD9850要方便得多。

AD9852的管脚分为三部分:(1)数据及控制端口;(2)电源部分;(3)参考及输出部分。

由于AD9852是目前市场上性价比较高的DDS器件之一,而且AD9852具有线性调频功能,可以方便实现频率的跳变。所以在雷达跳频系统中最终采用了AD9852芯片。下面就该芯片的应用设计做一简要介绍。

3 频率合成器的设计

要让AD9852工作,需要按下列流程初始化:

(1)数据在WR信号控制下从并行输入口D0~D1写入48位并行寄存器,或在SCLK控制下从串行输入口SDATA写入48位串行寄存器。

(2)对S/P SELECT置1或置0以决定输入数据是并行还是串行。1为并行,0为串行。

(3)AD9852芯片内部不带带通滤波器,所以外围电路中应该按实际工作需要外接带通滤波器,滤除不需要的频率分量。

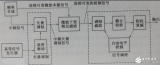

利用一片AD9852及简单的外围电路实现频率合成器的结构框图如图2所示。

根据我在设计过程中的实际经验,有以下几个问题需要注意。

3.1 单片机的选择

因为AD9852是3.3V系统,所以必须选择可以工作在3.3V的单片机。设计之初,忽略了这个问题,选用了普通51系列芯片,因为其输出电平只能为5V, 高于3.3V,DDS芯片因此被损坏。后打算采用51系列,但因为其在市场上很难买到,所以最终采用了Microchip公司的PIC系列单片机PIC16F874。该单片机可以工作在2.2~5.5V的范围内。又考虑到设计要求的高速控制,PIC16F874单片机的速度是51系列的3倍,所以PIC16F874单片机满足设计要求。

3.2 单片机的外围电路

DDS的工作电压是3.3V,而PIC的掉电复位电压是4.5V[4],所以PIC单片机的外围电路需要使用上电复位模式。

3.3 要避开DDS杂散较大的输出频点

在实际应用中,还有一些点的杂散信号很大,而且离主频很近,无法去除。所以应该避免输出这些频点。这些频点为靠近fc/3、fc/4、fc/5、fc/6……的频点。

3.4 去 耦

在一个电子系统中,通常多个器件共用一个电源。而电源线给交流信号提供了一个通路,使得交流信号通过电源线在器件之间传输,形成了干扰。所以必须在器件之间和电源到器件之间的电源线上加入滤波部分,滤掉交流干扰,称为去耦。电源的去耦通常用几个并联电容和串联电感来实现,如图3所示。

3.5 接 地

接地可以分为单点接地和多点接地。一般认为,连线长度大于信号波长的二十分之一时,应采用多点接地;反之,则采用单点接地。

实现多点接地就要在PCB板上布出一个面积较大的接地面,此接地面又与接大地的屏蔽外壳大面积接触。这样整个地的阻抗很小,电位可以认为是一致的,各器件就近接地,就避免了在地线上形成干扰。 在数模混和的电路中,由于数字部分干扰源很多,所以模拟部分易受影响。因此要注意把模拟地和数字地分开。一般的方法是用一根线来连接数字地和模拟地,而且只在一处相连,这样可以较好地切断数字部分的干扰源。

3.6 充分利用DDS的sweet pots

如前所述,在DDS中,其相位累加器的位数为A,但用来查询正弦表的位数只有其高P位,剩下的就四舍五入丢弃了,这样做会产生一种相位截断误差。但是如果相位累加器中的A-P位恰好为0,则其相位截断误差就为0,其输出频点的特性就会比较好,这就是所谓?quot;sweet pots“。所以在DDS单点输出时,使DDS尽量在sweet pots频点输出,可以达到优化输出特性的目的。

3.7 DDS参考信号输入端的注意事项

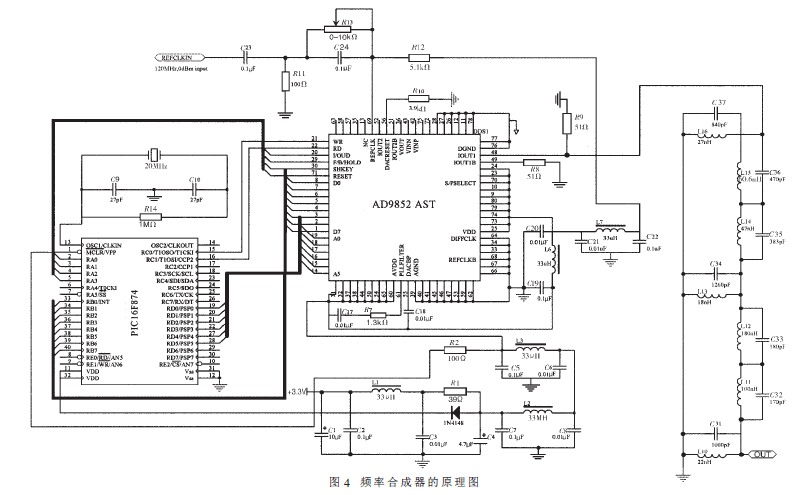

由于采用了参考信号单端输入的方式,所以REFCLKB端应该接地或电源;参考信号输入端REFCLK要跟电源相连接。因为DDS的参考信号要求有1.6V的直流电平,在参考信号输入到REFCLK端的端点处,应接一个5.1kΩ的电阻到3.3V直流电源,同时接一个0~10kΩ的可变电阻(此处取5kΩ)到100Ω的电阻,经过电阻分压,REFCLK端就有1.6V的直流电压。这个0~10kΩ的可调电阻同时用来微调REFCLK端对地的电阻,以调节REFCLK的直流电位,具体情况请参看图4。图4中的∏形滤波部分是为了滤除电源对REFCLK端的干扰。该频率合成器原理图如图4所示。

检验证明,利用AD9852设计的频率合成器具有跳频速度快、频率分辨率高、体积小、系统工作稳定、使用方便等优点。因此它有很强的实用价值。

DDS除了用于跳频系统中外,还可以用于任意波形产生、信号调制等。随着高速集成电路的飞速发展,DDS必将开拓更多新的应用领域。

责任编辑:gt

-

分辨率

+关注

关注

2文章

1058浏览量

41918 -

雷达

+关注

关注

50文章

2930浏览量

117461 -

DDS

+关注

关注

21文章

633浏览量

152629

发布评论请先 登录

相关推荐

ad9852应用

单片机简易信号源

基于8051F单片机的数字音频信号源的幅度控制

单片机脉冲信号源的CPLD实现方案

基于DSP和DDS的三维感应测井高频信号源实现

基于DDS的雷达校准信号源设计

基于AD9850_DDS芯片的宽频信号源

基于DDS的雷达中频信号源设计与实现

如何使用PIC单片机控制DDS芯片AD9852实现雷达跳频系统

利用STM32F103ZET6和AD9852DDS实现信号源的设计

基于单片机和AD9852芯片实现雷达系统跳频信号源的设计

基于单片机和AD9852芯片实现雷达系统跳频信号源的设计

评论