0 引言

随着工艺的进步以及深亚微米集成电路技术的不断发展,芯片的集成度越来越高,芯片的规模也越来越大。在无线通信、图像处理等各个芯片应用领域,越来越多的系统芯片(SoC)选择将各个功能不同的vwin 电路模块和数字电路模块集成在同一芯片中,以便在整个系统的性能达到最优的同时使成本降到最低。但这却给芯片的测试带来了意想不到的困难,也使得测试成本大为增加。ADC作为连接数字系统和模拟系统的桥梁,其测试显得格外重要。随着ADC性能的不断提高,芯片外部环境也已经成为ADC测试的主要障碍。

为了解决上述问题,同时更准确地测试ADC作为IP核集成到SoC中工作时的真实性能,各种ADC的内建自测试(Built-In-Self Test)方法应运而生,而如何精确而高效地为ADC内建自测试提供测试激励是一个非常关键的问题。本文提出一种可用于ADC片上测试的三角波信号发生器的实现方法,产生的三角波具有非常好的线性度,可以满足14 b高精度ADC的测试要求。整个设计采用UMC 0.18 μm CMOS工艺实现,电源电压为1.8 V。

1 三角波信号发生器的设计约束

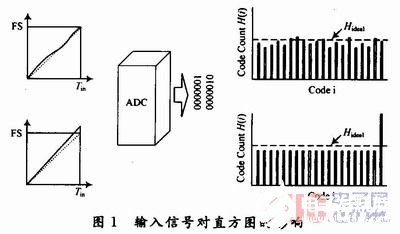

码密度直方图测试法基于统计学,用该法对ADC的静态特性进行测试时所加的测试激励必须尽量接近理想,在本文中也就是要尽量获得精准的三角波。如果获得的三角波信号存在非线性或增益误差,则用该信号去测试一个理想的ADC,测得的码元的直方图分布就会不均匀(如图1所示),这种不均匀来自测试激励本身的误差,所以由此测得的ADC的积分非线性(INL)和微分非线性(DNL)就引入了误差。

这样一来,测试结果的精确性很大程度上取决于所加三角波信号的精确度。所以,在设计三角波发生器时,必须根据被测ADC的性能指标来确定所需要的三角波发生器的线性度以及幅度。本文所设计的三角波信号发生器要满足精度为14 b的ADC的测试要求,那么其精度要求必须不低于16 b。

2 三角波信号发生器的原理

产生三角波信号的原理是用一个恒定不变的正向电流对电容进行充电得到一个均匀上升的斜波电压,当电压上升到一定值时再用一个恒定不变的负向电流对电容放电,从而得到一个均匀下降的斜波电压,交替用正负方向的电流对电容进行充放电,就可以得到连续的三角波电压信号,上升和下降的斜率由正负向电流与电容的比值I/C决定。为了满足ADC测试的要求,三角波信号应具有较好的线性度,同时也要保证较低的斜率,这就需要一个精确的小电流和一个较大的电容。

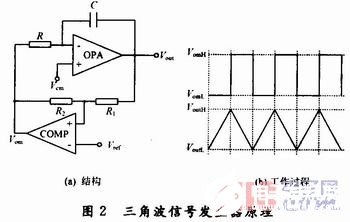

图2描述了三角波信号发生器的原理。图中运算放大器、电阻R、电容C组成一个方波积分器;比较器、电阻R1、电阻R2组成一个迟滞比较器作为一个反馈控制电路。电路的工作过程如下:

(1)当比较器输出电平为低电平VomL时,电容C处于充电状态,Vout不断上升,当Vout的值上升到使得比较器正相输入端电压高于Vref时,比较器输出翻转,输出高电平VomH,同时电流方向改变,电容C进入放电状态;

(2)当比较器输出电平为高电平VomH时,电容C处于放电状态,Vout不断下降,当Vout的值下降到使得比较器正相输入端电压低于Vref时,比较器输出翻转,输出低电平VomL,同时电流方向也翻转,电容C进入充电状态;

(3)如此循环振荡,便产生了周期的连续三角波电压信号。

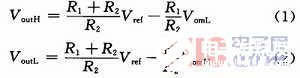

输出三角波电压信号Vout的阈值电压为:

式中:Vref为比较器负端参考电压;VomH,VomL分别为比较器输出的高、低电平。

由以上公式可知,周期T由RC常数、峰峰值Vout.pp以及比较器输出的高低电平VomH,VomL决定。

3 具体电路设计实现

3.1 运算放大器设计

运算放大器是整个电路结构中的关键部分,它直接决定了三角波信号发生器的线性度和线性输出范围。运算放大器与电阻R、电容C构成积分电路,其主要作用是使积分电容C一端电平保持稳定,这就要求运放具有较高的增益;同时,为了使三角波信号发生器的线性输出范围尽可能大,要求运放具有较大的输出摆幅。

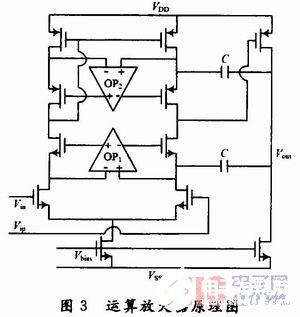

本文中运算放大器采用两级结构,如图3所示。其中:输入级采用带增益自举电路的套筒式共源共栅结构,包括主运放和辅助运放。主运放采用NMOS输入的套筒式共源共栅结构,具有高增益、低功耗以及良好的频率特性。辅助运放OP1,OP2分别为采用PMOS输入和NMOS输入的折叠式共源共栅全差分结构,进一步提高运放增益。

第二级采用共源结构来改善套筒式共源共栅结构输出摆幅小的缺点,同时也能一定程度上提高运算放大器的开环增益。由于级数增加也会引入新的零极点,从而会影响运放的稳定性。所以,必须加入补偿电容C,使相位裕度满足要求。

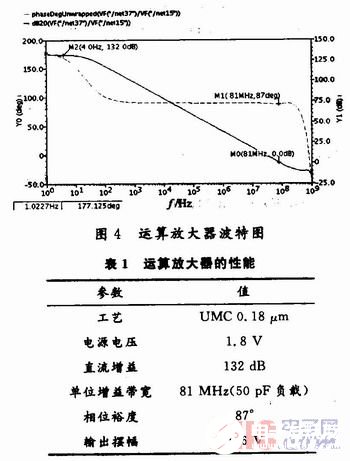

由Spectre仿真所得的运算放大器的交流幅频、相频特性如图4所示。表1总结了运算放大器的基本性能参数。

3.2 迟滞比较器设计

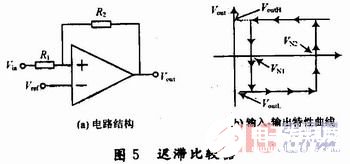

迟滞比较器的迟滞特性是比较器中引入正反馈的结果。迟滞比较器有两个输入阈值,当输入电压经过其中一个阈值时输出电压会改变,同时输入阈值会跳变到另一个值。要再次改变输出,输入必须到达跳变之后的阈值,在输出改变的同时,阈值又会跳变回原来的值。本文所采用的迟滞比较器电路及输入-输出特性曲线如图5所示。

两个输入阈值分别为:

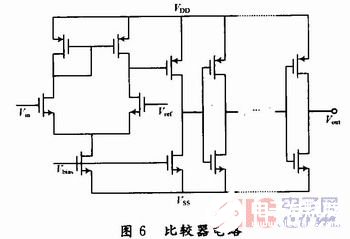

迟滞比较器中的比较器电路采用两级开环运放实现,由于比较器后级是一个2 mΩ的电阻,所以必须使比较器输出级电阻足够低,以防止由于电阻分压而导致比较器输出电压达不到电源电压以及地电压。因此,在两级开环运放之后增加了一个大宽长比的反相器链以获得较低的输出电阻,如图6所示。

4 仿真结果

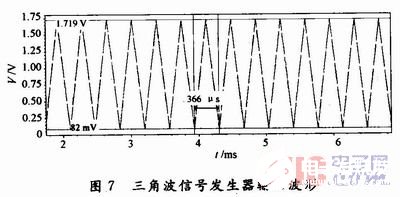

对该三角波信号发生器整体电路进行晶体管级仿真,仿真得到的三角波电压信号范围为82 mV~1.719 V,周期为366μs,如图7所示。

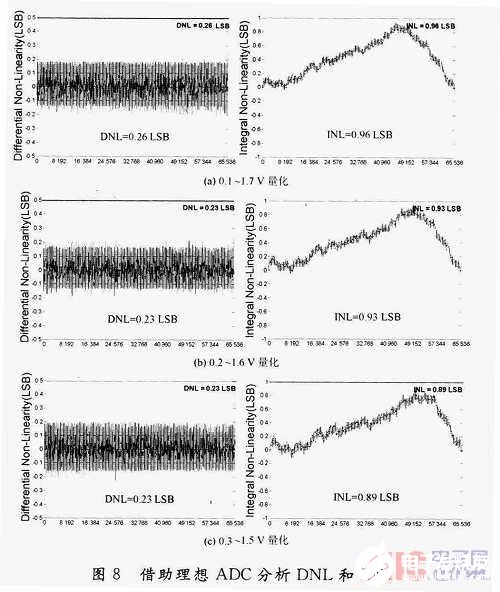

对该三角波信号进行多个周期的采样,利用16 b理想ADC分别对0.1~1.7 V,0.2~O.6 V,0.3~1. 5 V这三个不网的电压范围进行量化转换,并做相应的码密度直方图分析,得到各自的DNL和INL,如图8所示。从图8中可以看到,对于16 b理想ADC的量化,这三种不同的电压范围INL都在1 LSB以下(等价于INL《24μV),可以满足14 b ADC静态特性的测试。

5 结语

本文设计了一款应用于高精度ADC片上测试的高精度高线性度模拟三角波信号发生器,可为高达14 b的ADC静态参数片上测试提供有效的激励。仿真结果表明,该信号发生器所生成的三角波电压信号范围为82 mV~1.719 V,周期为366μs,INL《24 μV,等效精度达到16b以上,其幅值和频率可根据具体的设计要求进行调节,而且其线性度表现良好,可满足14 b高精度ADC静态参数的测试需求。

编辑:jq

-

芯片

+关注

关注

455文章

50712浏览量

423106 -

adc

+关注

关注

98文章

6495浏览量

544445 -

soc

+关注

关注

38文章

4161浏览量

218152 -

信号发生器

+关注

关注

28文章

1472浏览量

108739

发布评论请先 登录

相关推荐

一种用于高精度ADC片上测试的信号发生器

一种用于高精度ADC片上测试的信号发生器

评论