总线半握手跨时钟域处理

简要概述:

在上一篇讲了单bit脉冲同步器跨时钟处理,本文讲述控制信号基于脉冲同步机制的总线单向握手跨时钟域处理。由于是单向握手,所以比全握手同步效率高一些。

总线半握手同步器应用场景:

适用有脉冲控制信号的总线跨时钟域处理,不适用电平控制信号。慢到快,快到慢均可,大多数应用于快到慢的场景,尤其是频率比较大时,同步时间不仅要满足单bit脉冲同步器的同步时间,还要保证脉冲同步后采集是更新前总线数据。

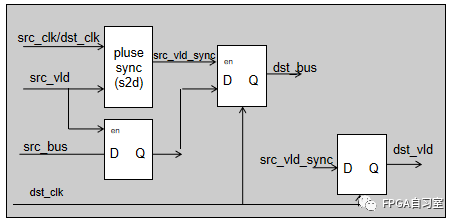

总线半握手同步器原理框图:

总线半握手同步器跨时钟域原理图如下所示,内部使用了脉冲同步器跨时钟处理机制来处理总线对应的控制信号。因为总线数据没有参与同步过程,所以需要输入的总线数据在控制信号变化时才更新,其他时间锁存原来的值。这样使得同步后的控制信号信号能采集到对应的总线数据。

总线半握手总线同步器仿真测试 :

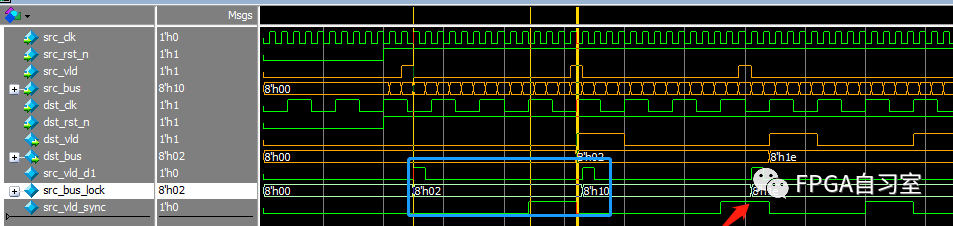

场景:快到慢, 源时钟100Mhz 目的时钟 25Mhz ,RATIO 比例设置为4(实际展宽了5倍)。

从上图中可以看出,源总线对应的控制信号src_vld_d1间隔是有要求的,同步之后的脉冲src_vld_sync 必须在前后两个脉冲之间,否则会导致前级同步后的脉冲采集到下级锁存的数据,如图红色箭头,本应采集数据是8’h10而实际误采集了8’h1e。

总线半握手与总线全握手对比:

1.效率:全握手不管快到慢还是慢到快其同步时间为6个慢速时钟。

半握手快到慢其同步时间为4个慢速时钟。(100Mhz->25Mhz)

2.接口:全握手没有对应的控制信号,握手信号上电解复位后即可工作起来,

半握手信号有对应有脉冲控制信号,内部通过脉冲同步器握手。

3.应用:全握手适用总线没有对应控制信号的场景,比如一些静态配置信号。

半握手适用总线有对应控制信号的场景,比如慢速的数据流信号。

易错点:把控制信号(脉冲)和总线拼接后,错误使用全握手同步器处理,而没有使用内有脉冲采样机制的半握手同步器处理。

原文标题:CDC(三)总线半握手跨时钟域处理

文章出处:【微信公众号:FPGA自习室】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

同步器

+关注

关注

1文章

98浏览量

14629

原文标题:CDC(三)总线半握手跨时钟域处理

文章出处:【微信号:FPGA_Study,微信公众号:FPGA自习室】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

前端总线频率的类型是什么?

总线时钟周期与CPU时钟周期的区别

极限失控的大模型使电力系统面临的跨域攻击风险及应对措施

单芯片运行六个操作系统,芯驰科技交卷跨域融合

航盛与高通发布全新一代墨子舱驾跨域融合平台

黑芝麻智能与斑马智行达成单芯片跨域融合平台项目合作

介绍一个IC设计错误案例:可读debug寄存器错误跨时钟

总线半握手跨时钟域处理

总线半握手跨时钟域处理

评论