前几天,临危受命,帮几个初学者的学生写一个简易AM信号的FPGA实现,以帮助他们搭建一个相对完整的系统,测试他们的低速ADC,高速DAC,AGC控制等等模块。本文的FPGA代码已经经过上板测试,由于时间紧急没有保存图片,所以文章只有仿真图片。

首先,为什么是AM信号的调制过程,是因为在短时间情况下,AM信号的实现相对简单,而且上述提到的几个模块都可以得到使用和验证。因为FPGA的价格因素,做课设/比赛使用最多的还是Altera的Cyclone系列板。所以,本文使用QuartusII 13.1 作为Verilog代码综合实现工具。AM信号调制过程就不做过多介绍了,简单来说,就是基带信号和一个直流信号相加,然后与载波相乘。那么,在实现过程中,做了些许改变,先让基带信号与载波相乘,然后将截位后的信号与载波相加。如果想要实现更精细的AM信号调制(变更调制深度等参数),可以修改这个地方的先后顺序。AM公式表达如下:

为直流信号,是基带信号,是载波信号。

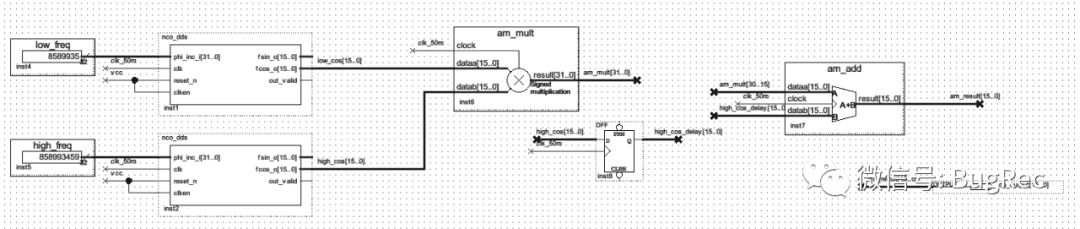

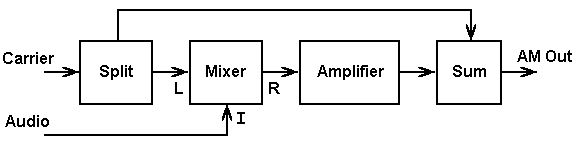

实现过程如上图,顶层文件使用BSF文件,更为直观。由上图可以看出,基带信号和载波信号是由NCO(DDS)产生,在上板验证中,低频部分的NCO被删去,由低速ADC采样外部信号替换这部分的低频信号。所以在刚开始搭建模块时,低速NCO输出信号位宽就兼容了低速ADC的16位位宽。根据资料1可得,Altera提供的NCO是根据32位输入信号phi_inc_i而输出对应的频率的正弦波。公式为:

是NCO预设输出正弦波频率,是输入时钟频率,是NCO的相位精度。这里的设置是32位。NCO(DDS)的本质是ROM表,ROM表存储着正弦波的波形数据,相位精度代表波形数据的多少。根据phi_inc_i累加地址,ROM根据地址输出波形数据,最后数据计算如下。

基带载波

频率(MHz)0.110

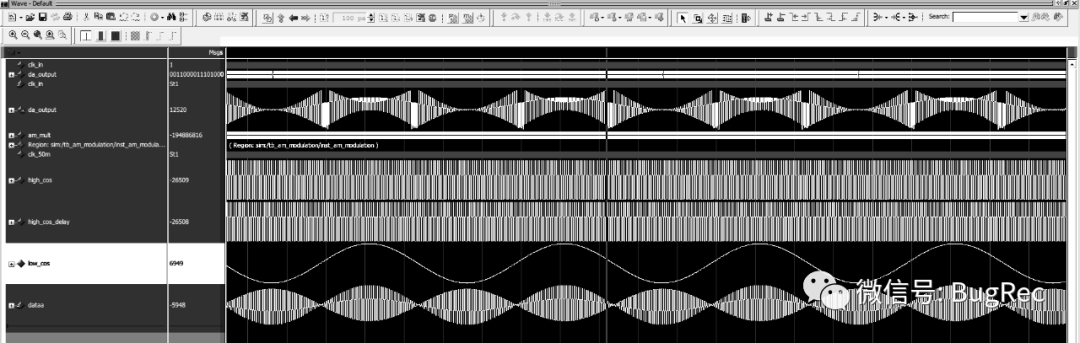

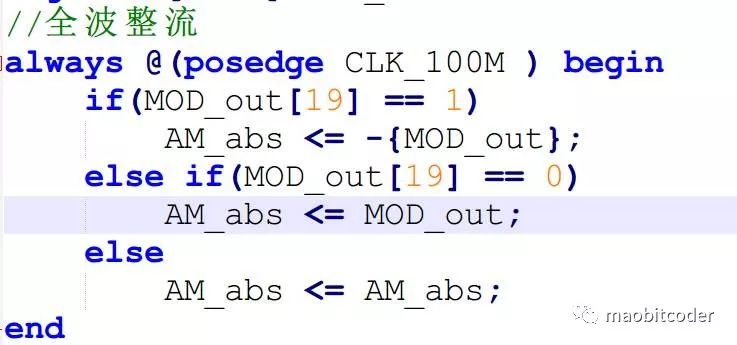

phi_inc_i8589935858993459

然后让基带和载波信号相乘,使用LPM_MULT IP核,设置好位宽,数据类型设为“signed”,设置流水线(增加clock),延迟设为1,便于后续通过时序检查。相乘输出信号位宽为32位,保险起见我们只截取最高位的符号位,再截取低位的数据。但是经过上板测试和仿真,符号位实际上有很多位。当然,这部分可以将符号位进行优化,或者设置一个模块,根据输入的参数输出不一样的截位信号,相当于在调整调制深度。同时,将载波信号延迟一个周期,与乘法器延迟一周期的信号做好时序对齐,然后经过LPM_ADD_SUBIP核的加法运算;同样,LPM_ADD_SUB IP核设置好输入信号位宽,数据类型设为“signed”,设置流水线,延迟设为1。最后输出的信号就可以经过高速DAC输出。整个调制过程就结束了。仿真结果:

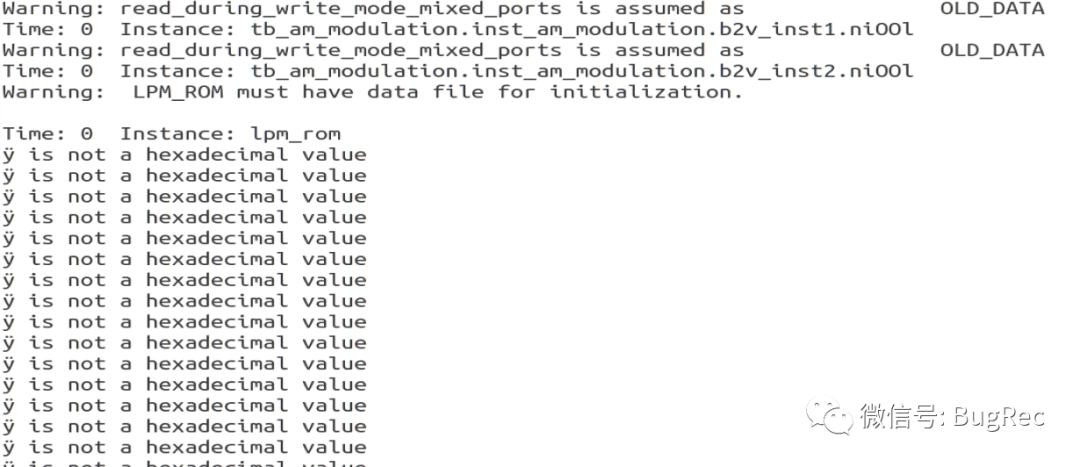

最后思考,可以在加法器和乘法器增加一个enable端口,IP核可以增加这个输入信号;如果先加再乘,由于直流信号一般不会变动,使能信号可以等待每次低速ADC或低速NCO数值更新再拉高一次;乘法器也可以使用使能信号控制,这样的话性能可能没有变化,功耗或许可降低些。此外,使用VCS仿真NCO的nco.vo文件时,一直遇到一个问题,报错如下:

大概是说NCO生成的4个hex文件有问题,但是使用modelsim就没这个问题了。

原文标题:简易AM信号调制的FPGA实现过程简单讲解

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

- FPGA

+关注

关注

1620文章

21472浏览量

597978 - 加速器

+关注

关注

2文章

781浏览量

37033

原文标题:简易AM信号调制的FPGA实现过程简单讲解

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先登录

相关推荐

fpga仿真文件怎么写

射频信号源的LF源与AM调制信号源是如何调试的呢?

如何写一个内存泄漏检测工具

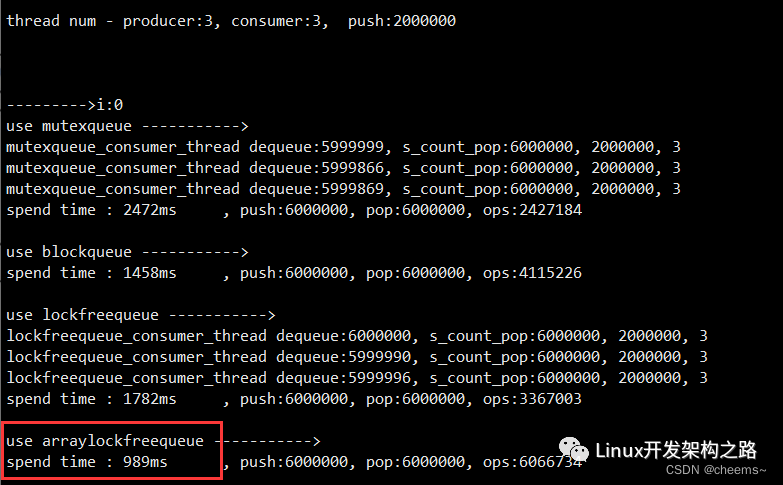

如何实现一个多读多写的线程安全的无锁队列

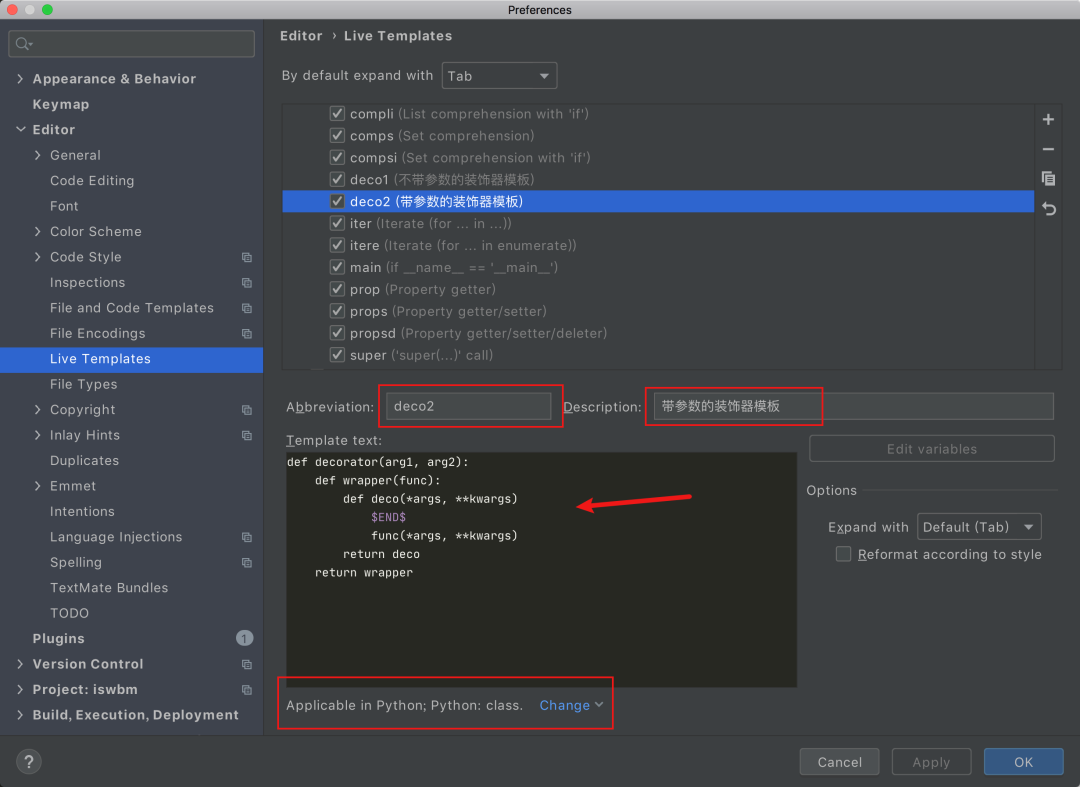

如何写一个简单的装饰器

米尔AM62x核心板续写AM335x经典 助力新一代工业4.0升级

FPGA为什么有时候还需要一个时钟配置芯片提供时钟呢?

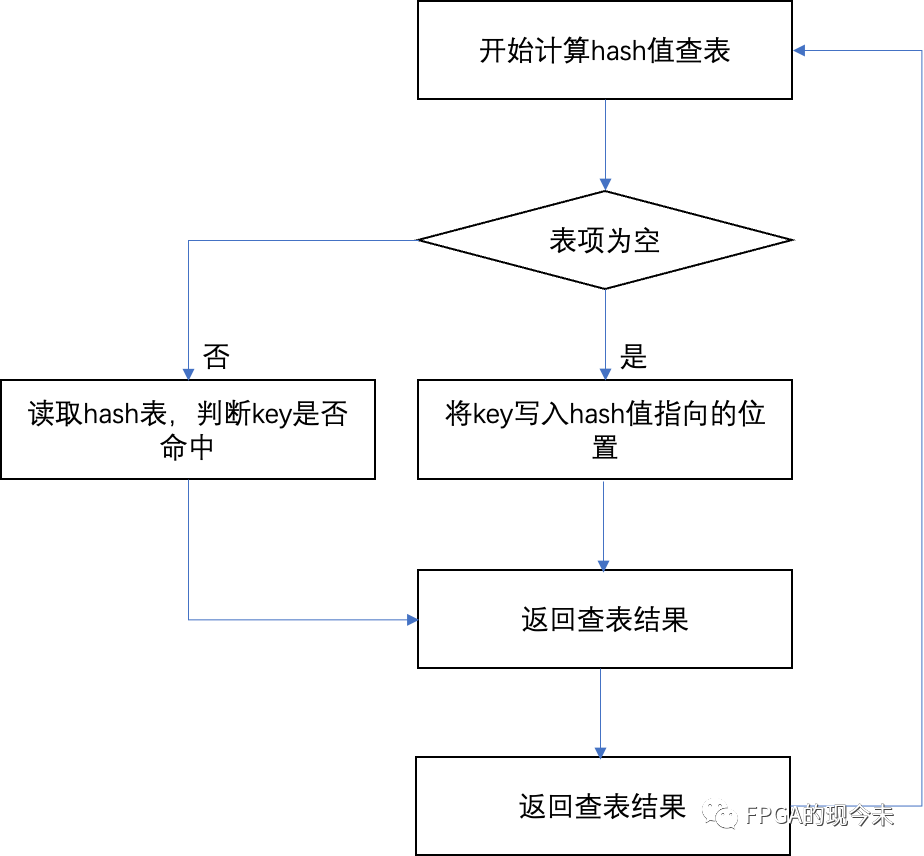

hash算法在FPGA中的实现(3)

如何写一个简易AM信号的FPGA实现?

如何写一个简易AM信号的FPGA实现?

评论