1 车速传感器性能测试平台简介

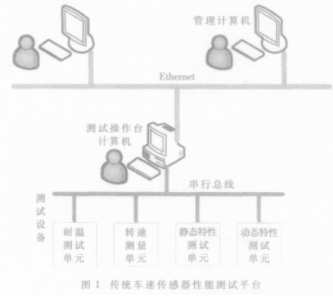

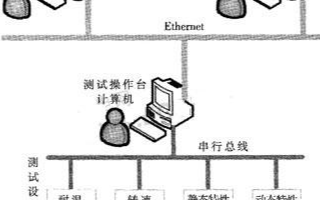

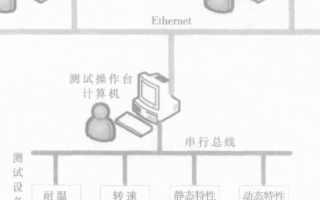

车速传感器是电控汽车的关键部件,其性能优劣直接关系到发动机怠速和变速器控制,因此,必须对其各项性能进行全面严格的测试。而这一系列的性能测试又有赖于一个稳定、高效的测试平台。传统测试平台通常采用由测试设备、测试操作台计算机和后台管理计算机组成的三级系统结构,如图1所示。

在此测试平台中,测试设备一般只提供串行通信接口(如RS-232、RS-485等),无法直接接入管理计算机所在局域网(如最常用的Ethernet)。所以,整个系统必须通过一个测试操作台计算机将上层局域网和底层串行总线网络连接起来以保证实测数据(各项性能指标数据)的顺利上传和测试操作命令(如车速传感器耐温测试、动/静态特性测试)的准确下达。为此不但要增设测试操作台计算机工作站,同时还必须安装各种串行口通信卡、以太网网卡和相应的板卡驱动程序,开发包含串行口通信模块和以太网通信模块的测控软件。由此可见,由于通信接口和协议的不兼容,使得传统车速传感器性能测试平台不仅软硬件投资成本高,系统结构复杂,调试和维护工作量大,而且管理计算机和测试设备间的数据传输要经过中转,传输过程显得过于复杂。

2 基于串行口-以太网桥的测试平台

通过对图1所示测试平台的研究,发现造成系统平台成本高、结构复杂、中间处理过程繁多的根本原因是底层各测试设备和上层局域网通信接口、协议的不兼容。一般来说,底层测试设备需传输的数据量很小,大多只提供通信距离短、成本低的串行口(如RS-232、RS-485);而上层的局域网大多采用以太网。所以针对此类应用,可以开发一种基于微处理器的嵌入式串行口-以太网桥实现协议转换,直接将各种仅支持串行口的测试设备接入以太网,实现各测试设备与管理计算机局域网的无缝连接,简化数据传输过程。

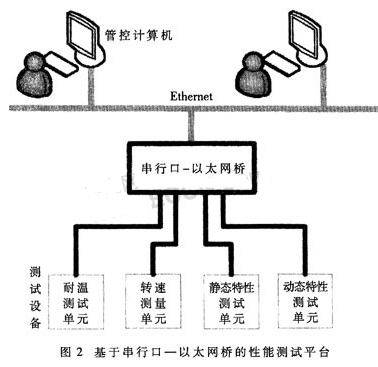

引入嵌入式串行口-以太网桥后的车速传感器性能测试平台结构如图2所示。

相比图1所示的传统测试平台,新测试平台下的串行口-以太网桥负责完成串行口测试设备和以太网之间的协议转换(即在底层完成串行帧数据和以太网帧数据的格式转换),实现了各测试设备和以太网的无缝连接,简化了数据传输过程。测试人员可以在远端通过上层管理计算机直接下达各种测试命令来控制各测试设备完成传感器各项性能指标的测试;而各项实测数据也能从各测试设备直接传送到后台管理计算机进行处理;从而使后台管理计算机能以多任务方式同时完成前台测试设备控制和后台数据处理(如数据报表统计分析,图形曲线显示和数据库更新),成为平台中的管控一体化工作站,省去了原平台中的测试操作台计算机工作站,测试人员也不必再亲临现场进行各种测试操作,极大地降低了工作强度。这样一来,不仅使系统成本大为降低、体积大为缩小、结构更加简单,同时将前台测试控制和后台数据处理集中于一台计算机,实现了管控一体化,节省了人力资源,使得系统的软硬件资源得到了最大限度的利用。

3 串行口-以太网桥设计

通过新旧测试平台对比,可以看到测试设备和后台管理计算机两大部件在性能和成本上基本相同。所以新测试平台的性能好坏和成本高低很大程度上取决于新引入的嵌入式串行口-以太网桥的性能和成本。目前嵌入式产品市场上此类网络设备大多是基于高档微处理器和实时操作系统开发的,其价格昂贵,且提供的串行口也只有1~2个,不适合需将多个串行口设备集中接人以太网,同时又要控制成本的应用场合。本文根据这类具体的应用需求在8位微控制器平台上设计了一种提供多个串行口的低成本嵌入式串行口-以太网桥。下面对其硬件和软件系统设计进行介绍。

3.1 硬件系统设计

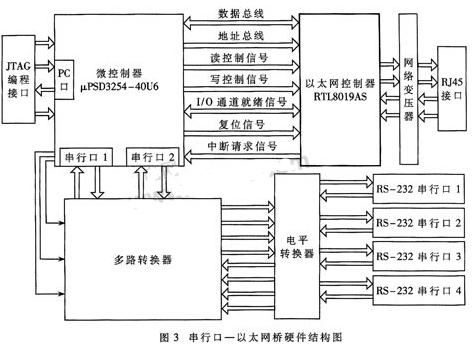

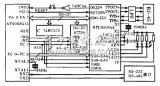

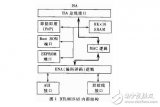

实现本系统所用串行口-以太网桥的功能,需要进行多个串行口设备的以太网接人,以及串行通信协议和以太网通信协议的相互转换。所以硬件电路设计主要包括多路串行口电路模块和以太网接口电路模块设计。本文硬件系统方案选用ST公司的工业级SoC型微控制器μPSD3254和Realtek公司的高性能以太网控制器RTL8019AS两大核心器件进行电路设计。硬件系统设计如图3所示。

其中μPSD3254是一款由8051内核模块和PSD模块构成的具有SoC特征的增强型高速微控制器。晶振频率最高可达40MHz,芯片内的PSD模块为用户提供了丰富的可配置存储器资源(256KB主Flash、32KB次Flash及32KB的SRAM)、灵活的DPLD地址译码电路以及3000门的CPLD模块电路,片内硬件看门狗大大提高了系统可靠性,芯片自带JTAG接口支持ISP在系统编程,方便了程序调试和下载;而RTL8019AS是一款非常成熟的基于ISA总线、NE2000兼容的高性价比10M以太网控制器,其本身能完成以太网协议处理,只需和微控制器进行简单连接即可实现以太网通信;另外硬件电路还包括MAX232电平转换器和20F001N网络滤波器等少数外围器件。整个硬件系统仅由4、5个芯片构成,结构简单紧凑,可靠性高,成本低廉。下面从三方面给出硬件电路的具体设计。

3.1.1 PSD模块配置设计

微控制器μPSD3254的PSD模块使得硬件电路的设计大为简化。它本身提供的两块大容量Flash以及SRAM(支持后备电池)使用户无需再进行外部程序/数据存储器扩展。同时PSD模块中的DPLD子模块为Flash和SRAM提供了灵活的地址译码,CPLD子模块可供用户设计一些简单的组合/时序逻辑电路。本设计根据具体应用需求,对PSD模块配置如下:

(1) 主Flash扇区0(fs0)配置在程序存储器的0000H~FFFFH空间;

(2) 主Flash扇区1(fsl)配置在程序存储器的8000H~7FFFH空间;

(3) SRAM(rs0)配置在外部数据存储器的0000H~7FFFH空间;

(4) CPLD的PA口和PB口被分别设计为两个多路转换器,以供串行通信时进行信道切换。

3.1.2 串行口扩展设计

由图2可知,车速传感器性能测试平台中四个仅支持串行口的测试设备(分别负责耐温、转速、传感器静态特性和动态特性的测试)要同时接人嵌入式串行口-以太网桥,而微控制器μPSD3254本身只提供两个串行口(uart0、uart1),所以必须进行串行口扩展。一种简单的扩展方法是利用单片机I/O端口控制多路转换器(如CD4052)进行串行口扩展(图3),实现了一点对多点分时串行口通信。根据微控制器μPSD3254的I/O端口资源情况,依此方法系统最多可扩展32个串行口。根据此思路并结合测试平台的具体应用需求,利用μPSD3254的CPLD模块设计了两个二选一的多路转换器,从而不仅将两个串行口扩展为四个(uart00、uart01和uart10、uart11),而且省去了多路转换器芯片。另外,电平转换器实现TTL—RS232电平转换,这样就为四个测试设备提供了四个标准RS-232串行口供其接入串行口-以太网桥。

3.1.3 以太网接口设计

以太网接口是硬件电路设计的关键。因为RTL8019AS是基于ISA总线PC主板的以太网控制器,所以在和8位微控制器进行接口(见图3)时其硬件电路与通用方式有很大不同。下面从RTL8019AS以太网控制器自身功能配置、与微控制器μPSD3254之间的总线接口及与网络介质的接口等三方面给出具体电路设计。

(1) RTL8019AS功能管脚设置

RTL8019AS提供3种工作方式:PnP即插即用方式、免跳线方式和跳线方式。由于8位微控制器μPSD3254无法支持PnP工作方式,而免跳线方式又需外加专用串行E2PROM 93C46以存放相应的工作参数,因此选择跳线工作方式。在这种方式下RTL8019AS的中断、I/O端口地址、网络接口类型选择等就完全取决于表1所示功能管脚的状态。

JP脚接高电平使芯片工作于跳线方式,IOCS16B脚接低电平选8位数据总线,IRQS0~IRQS2接低电平选INT0为中断请求源,IOS0~IOS3接低电平选芯片I/O端口基地址为300H,AUI、PL0、PL1接低电平分别选。BNC网络接口和10Base-T双绞线传输介质,SMEMRB/SMEMWB接高电平屏蔽BROM读写操作。

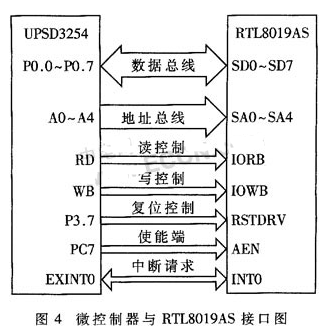

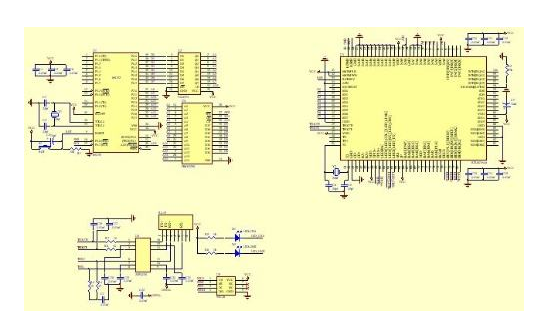

(2) RTL8019AS与微控制器的总线接口

RTL8019AS与微控制器的接口连接如图4所示。

针对以上总线接口还有几点说明:①由于在8位微处理器系统中,只需操作RTL8019AS的32个I/O端口地址,所以只需5根地址线进行译码,其余15根地址线要根据I/O端口基地址接固定电平。②AEN使能端为低电平有效,而PC7的内部逻辑方程为PC7=A15,所以RTL8019AS映射到μPSD3254外部数据区的地址范围是8000H~FFFFH,这样μPSD3254通过读写外部数据区的此地址范围就能实现对RTL8019AS的读写。③由于RTL8019AS的处理速度比μPSD3254快很多,其内部数据缓冲区也相对较大,为了避免RTL8019AS每收到一帧数据就发出中断请求,从而频繁地打断处理器,所以μPSD3254以查询而非中断方式读写RTL8019AS以太网控制器。④RTL8019AS在复位时要进行一系列内部寄存器操作,所以用单片机的P3.7端口控制其复位,以保证有足够的复位时间。

(3) 网络介质接口连接

由于RTL8019AS内部已集成以太网收发器,而且对外提供AUI(支持粗同轴电缆)和BNC(支持细同轴电缆和双绞线)两种网络介质接口,所以本方案选择较常用的BNC接口,这样就只需再外加一个网络变压器20F001N和RJ45水晶头插座即可解决网络介质接口问题。

3.2 软件系统设计

由于整个网桥的底层功能(如以太网协议实现)已由硬件电路完成(见图4),所以在软件上只需完成RTL8019AS驱动、精简TCP/IP协议栈实现、用户自定义应用层处理以及串行口通信等功能。为了便于软件功能的实现和扩充,软件系统采用模块化方法进行设计。

3.2.1 RTL8019AS驱动模块

此模块设计依赖于RTL8019AS的硬件工作原理,即对RTL8019AS的驱动是通过操作其内部寄存器组来完成的。通常,在进行数据收发前需先向各寄存器写入相应的控制字,当发送以太网数据帧时,微控制器μPSD3254通过RTL8019AS的I/O端口将打包好的数据以远程DMA方式写入到RTL8019AS的内部数据发送缓冲区,然后启动发送;接收以太网数据帧时,RTL8019AS会自动接收数据并将其存人自己的内部数据接收缓冲区,然后以寄存器标志或中断请求方式通知μPSD3254,μPSD3254再通过RTL8019AS的I/O端口将数据以远程DMA方式读到自己的数据缓冲区并进行下一步的拆包处理。基于以上分析,RTL8019AS驱动程序分三部分设计,即芯片初始化(设置MAC地址、收发缓冲区大小、中断等)、发送数据子程序和接收数据子程序。详细的驱动程序见文献[3]。

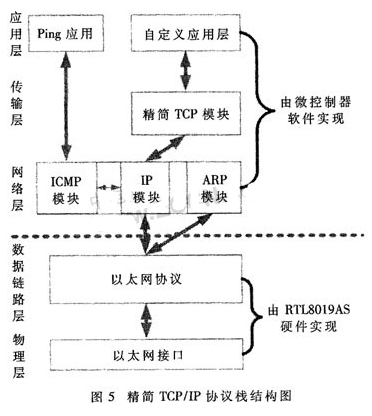

3.2.2 精简TCP/IP协议栈模块设计

此模块负责TCP/IP协议的处理。由于以太网协议只规定了物理层和数据链路层,所以要想实现进程间通信还必须实现上层的TCP/IP协议。但此协议非常复杂,而且很多功能都是针对PC平台的应用,在嵌入式系统中根本用不上;另外,8位微控制器的处理能力和内存空间也使得在其上实现完整的TCP/IP协议根本不可能。因此,在8位机上用软件实现TCP/IP协议时首先必须根据应用需求对整个协议栈进行裁剪。在本应用中,由于只需要在串行口和以太网间进行简单的测试数据和测试命令传输,所以在应用层采用了自定义协议,在传输层选择了能保证可靠性的TCP协议并进行了有针对性的TCP协议机制裁剪,而在网络层只实现了不提供分片和路由功能的IP协议、测试网络连通性所需的ICMP协议(仅支持Ping应答)以及提供IP地址到以太网地址(MAC地址)映射的ARP协议。这样,就得到了一个能在低档8位机上实现和运行的精简TCP/IP协议栈。此协议栈从物理层到应用层的完整结构如图5所示。

3.2.3 应用程序模块设计

应用程序模块直接面向用户需求提供相应服务。本设计中,根据整个软件模块的功能划分,应用程序需要完成串行口通信处理及串行帧和IP分组的格式转换。由于嵌入式串行口-以太网桥的TCP/IP协议栈传输层选择了保证数据传输可靠性的TCP协议(向应用层提供流式套接字接口),所以应用程序无需再进行超时重发和回传确认处理,仅需要完成串行口的数据收发操作以及串行数据帧和IP分组的格式转换。进行串行数据帧和IP分组的格式转换时使用了共享数据缓冲区和指针技术以避免协议分层间的数据拷贝,不仅节省了内存空间,而且大大提高了打包和拆包的处理速度;另外,由于串行口设备每次需传输的数据量很小,所以四个串行口缓冲区的数据采用集中打包、一次发送的方法减少了网络访问次数,既提高了通信效率又避免了因频繁短帧传输造成的网络拥堵;最后应用程序模块还提供了嵌入式串行口-以太网桥的串行门属性配置功能,用户可根据各测试设备串行口的具体属性,在管控计算机上通过以太网对网桥的各串行口收发数据缓冲区以及波特率进行远程动态设置,从而极大地提高了网桥的适应性。

实验证明,本文提出的嵌入式串行口-以太网桥应用于车速传感器性能测试平台,不但能完全满足测试平台的通信要求,还具有成本低、体积小、可靠性高等优点。同时在此网桥的硬件平台上,只要针对具体应用需求对应用程序模块稍作修改就可应用于其他汽车传感器性能测试平台(如轮速传感器性能测试平台)以及温室、环保、气象等需要远程监测的场合。因而该串行口-以太网桥具有很强的适应性和很高的推广应用价值。

责任编辑:gt

-

微控制器

+关注

关注

48文章

7542浏览量

151306 -

以太网

+关注

关注

40文章

5419浏览量

171588 -

接口

+关注

关注

33文章

8573浏览量

151007

发布评论请先 登录

相关推荐

基于微控制器μPSD3254和RTL8019AS实现串行口-以太网桥的设计

用51单片机控制RTL8019AS实现以太网通讯

基于ARM 嵌入式以太网接口设计与实现Design and

RTL8019以太网控制芯片

RTL8019AS实现嵌入式以太网设计.rar

RTL8019AS实现TCP IP网络通信

如何使用51单片机控制RTL8019AS实现以太网通讯

基于RTL8019AS和μPSD3254实现以太网桥的设计

基于RTL8019AS以太网控制器实现以太网通讯的应用方案

基于微控制器μPSD3254和RTL8019AS实现以太网桥的设计

基于微控制器μPSD3254和RTL8019AS实现以太网桥的设计

评论