嵌入式系统博客CNX-Software上的帖子称,基于开源RISC-V指令集体系结构芯片打造的Allwinner D1处理器定于下周发布,同样由Allwinner生产的名片大小的D1开发板将于5月上市。

据报道,该开发板是一个名片大小的单板计算机,具有运行在1GHz的单核XuanTie C906 64位RISC-V CPU和1GB DDR3 RAM,其中一些信息已经可供中国的开发人员使用。

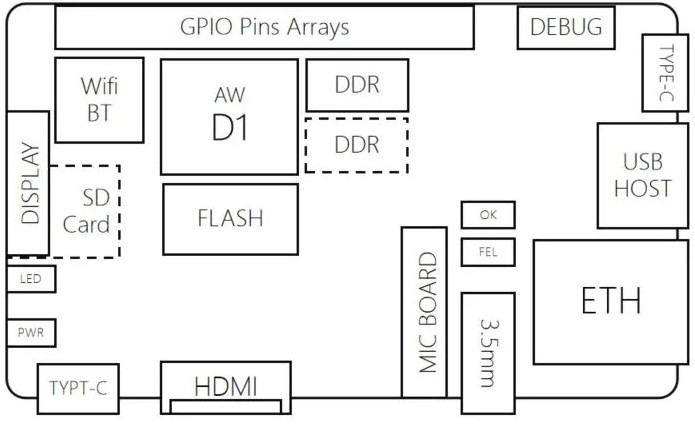

Allwinner D1开发板

首先我们看看主板规格:

SoC – Allwinner D1单核XuanTie C906 64位RISC-V处理器@ 1.0 GHz,带有HiFi4 DSP,G2D 2D图形加速器

内存– 1GB DDR3内存

存储– 256MB SPI NAND闪存,MicroSD卡插槽

输出– HDMI 1.4端口高达4Kp30,MIPI DSI和触摸面板接口高达1080p60

解码– H.265最高1080p60或4Kp30,H.264最高1080p60或4Kp24,MPEG-1 / 2/4,JPEG,VC1最高1080p60

编码– JPEG / MJPEG最高1080p60

音频– 3.5毫米音频插孔,通过HDMI输出数字音频,麦克风板连接器

连接性–通过RTL8211F PHY的千兆以太网,通过XR829模块的2.4GHz WiFi 4和蓝牙模块

USB – 1个USB 2.0主机端口,1个USB Type-C OTG端口

扩展– 40针GPIO连接器

电源–通过两个USB-C端口之一提供5V / 2A

尺寸– 85 x 56 mm(6层PCB)

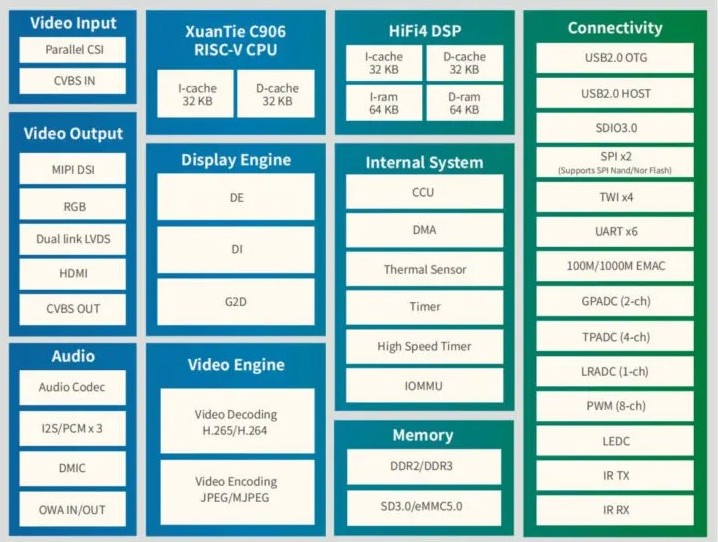

Allwinner D1 RISC-V处理器

有关Allwinner D1 RISC-V处理器的更多详细信息:

CPU –Alibaba XuanTie C906 64位RISC-V内核,具有32 KB的I缓存+ 32 KB的D缓存

DSP –具有32 KB I缓存+ 32 KB D缓存,64 KB I内存+ 64 KB D内存的HiFi4 DSP 600MH

内存I / F –最高2GB DDR2 / DDR3

存储I / F – SD3.0,eMMC 5.0,SPI NOR / Nand闪存

视频引擎

视频解码

H.265最高1080p @ 60fps或4K @ 30fps

H.264最高1080p @ 60fps或4K @ 24fps

MPEG-1 / 2/4,JPEG,VC1最高1080p @ 60fps

视频编码– JPEG / MJPEG最高1080p @ 60fps

支持上/下输入图片缩放器

影像输出

RGB LCD输出接口高达1920 x 1080 @ 60fps

双链路LVDS接口高达1920 x 1080 @ 60fps

4通道MIPI DSI接口,最高1920 x 1080 @ 60fps

HDMI V1.4输出接口高达4K @ 30fps

CVBS OUT接口,支持NTSC和PAL格式

视频输入

8位并行CSI接口

CVBS IN接口,支持NTSC和PAL格式

声音的

vwin 音频接口– MICIN1P / N,MICIN2P / N,MICIN3P / N,FMINL / R,LINEINL / R,LINEOUTLP / N,LINEOUTRP / N,HPOUTL / R

数字音频接口– I2S / PCM,DMIC,OWA IN / OUT

网络–带RMII和RGMII接口的10/100 / 1000M EMAC

USB – USB2.0 OTG,USB2.0主机

其他外设

SDIO 3.0,SPI x 2,UART x 6,TWI x 4

PWM(8通道),GPADC(2通道),LRADC(1通道),TPADC(4通道),IR TX&RX

封装-LFBGA BGA13 * 13 / 0.35 / 0.65mm,337 PINS

制造工艺– 22nm

责任编辑:pj

-

处理器

+关注

关注

68文章

19259浏览量

229645 -

芯片

+关注

关注

455文章

50714浏览量

423113 -

连接器

+关注

关注

98文章

14476浏览量

136424 -

计算机

+关注

关注

19文章

7488浏览量

87847

发布评论请先 登录

相关推荐

晶心科技推出突破性的RISC-V 27系列处理器及向量扩展指令处理器

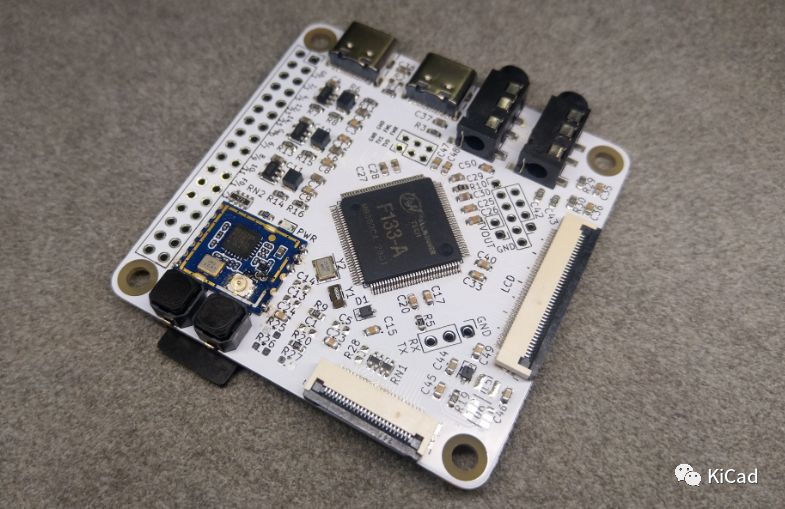

Made with KiCad(十六):全志RISC-V 64 SoC F133/D1s开发板

全志科技:多个型号的处理器芯片采用RISC-V内核

学习RISC-V入门 基于RISC-V架构的开源处理器及SoC研究

RISC-V开源处理器核介绍

阿里平头哥宣布开源玄铁RISC-V系列处理器

香山处理器 RISC-V的典范

读《玄铁RISC-V处理器入门与实战》

RISC-V是通用RISC处理器还是可定制的处理器?

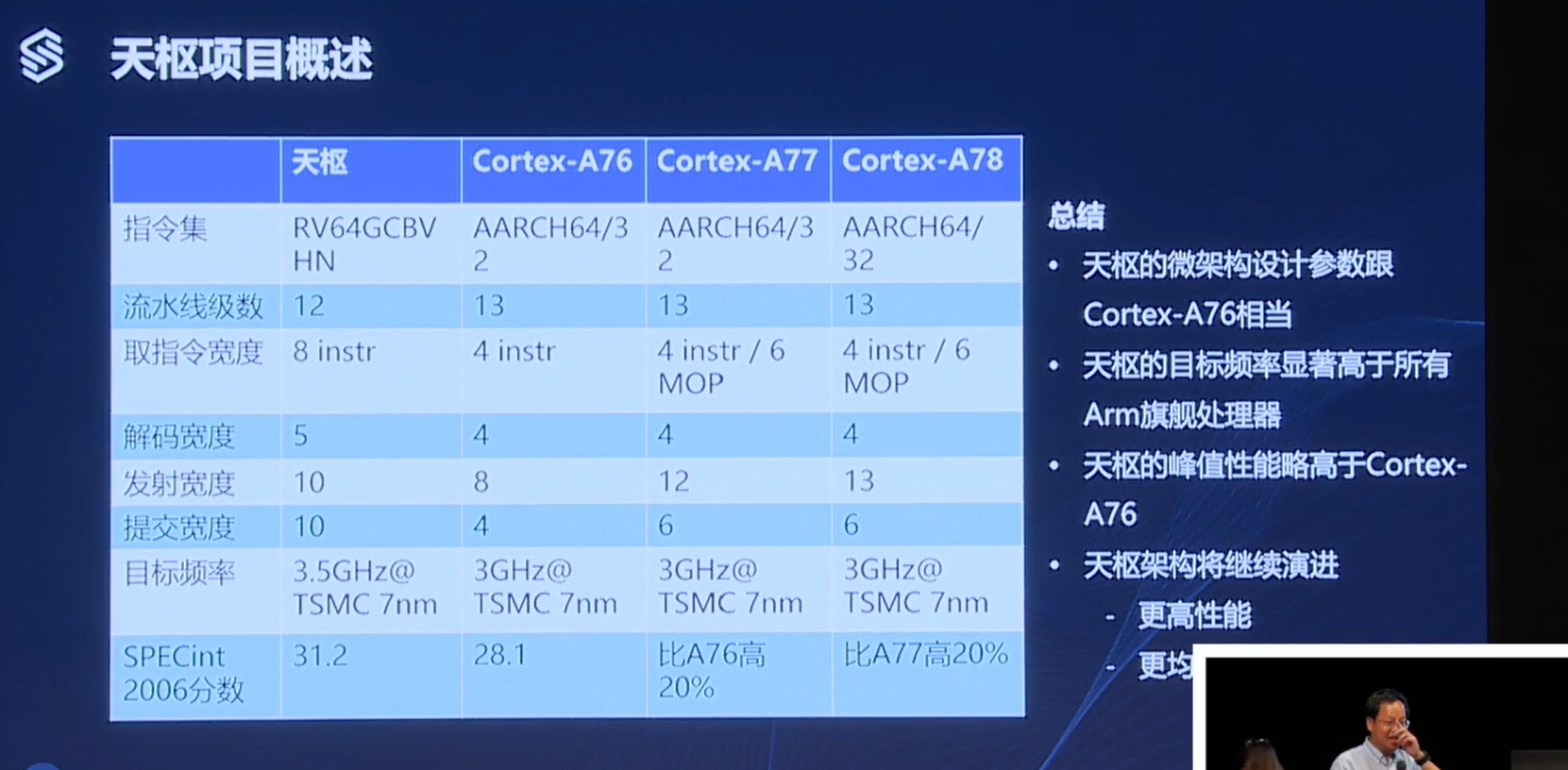

首届risc-v峰会的最新消息:天枢的高性能RISC-V处理器架构详解

商业级RISC-V 64位高性能处理器开源了?!

从零开始写RISC-V处理器

基于形式的高效 RISC-V 处理器验证方法

Out项目之增强RISC-V处理器性能的自定义硬件模块

Allwinner D1 RISC-V处理器性能如何?

Allwinner D1 RISC-V处理器性能如何?

评论