作者:马翔;冯正和;陈雅琴

随着通信技术的快速发展,各种新业务的层出不穷,无线通信以其方便、灵活、易于组网等特点获得了广泛的应用。其中特别是扩频通信技术由于其抗干扰、抗多径的突出优点,获得了各方的青睐,无线扩频产品的开发研制已成为国内外通信界的一个热点。同时扩频通信技术也已经超出了无线通信的领域,在一些“有线 ”的领域内得到了充分应用,如电力线通信系统等。

HARRIS公司的HSP3824直接序列扩频基带处理器是其24GHz天线芯片组的一部分,它包含了全双工或半双工收发机的所有功能。该芯片的最突出特点是灵活,其数据率、扩频比、调制方式以及PN码等都可以根据需要而动态调整,也可以通过设置HSP3824内部寄存器来实现大量的应用,为设计提供了较大的灵活性。实践证明该芯片可靠易用,是开发扩频通信产品的良好选择。

1 HSP3824主要功能和特点

HSP3824是HARRIS(Intersil)公司开发的用于直接序列扩频通信的基带处理器。其基本功能是将接收到的基带数据扰码、调制、直接序列扩频输出至中频调制。或反之,将中频解调后的信号经A/D变换、解扩、解调、解扰后得到基带数据并输出。

它的主要特点如下[1]:

完全的直接序列扩频基带处理器(DSSS基带处理器);

处理增益最高12dB;

可编程PN码11、13、15、16位可选;

可编程数据率,最高达4Mbps;

适合于PCMCIA板应用的TQFP封装;

调制方式DBPSK、DQPSK可选;

支持半双工、全双工操作;

内置A/D转换器;

低功耗,某些模块在不工作时可置为SLEEP状态。

HSP3824内置57个寄存器,这些寄存器的值决定了它的工作状态,外部控制器可对这些寄存器进行读写。通过正确配置寄存器,可实现HSP3824的各种功能,且可以动态调整。

除了基本的发送、接受模块之外,HSP3824还包括8位的测试总线,用于测试芯片的内部信号,实时反映芯片的工作情况;输入信号强度检测和信道空检测(CCA)可避免数据阻塞,优化网络传输;还可以由外部控制端口设置为各种功耗模式。

2 HSP3824内部结构及使用要点

2.1 内部结构及外部接口

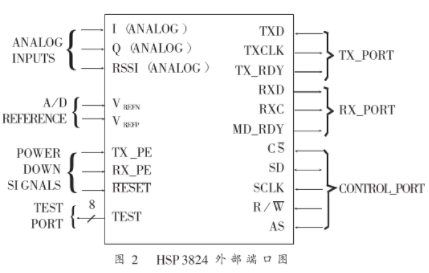

HSP3824可大体上分为三部分:控制、发送及接收。相应地对外分别提供三个数字端口与控制器相连,即控制端口 (CONTROL_PORT)、发送端口(TX_PORT)及接收端口(RX_PORT),且这三个端口可分别独立工作或同时工作。此外,还具有一个测试端口(TEST_PORT),供外部控制器监控HSP3824的工作状态。

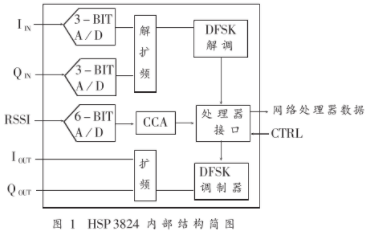

HSP3824的内部结构简图如图1所示。

IIN:接收到的I路vwin 信号;

QIN:接收到的Q路模拟信号;

RSSI:接收信号强度检测(模拟信号);

IOUT:I路输出扩频基带数字信号;

QOUT:路输出扩频基带数字信号;

HSP3824外部端口如图2所示。除四个数字端口外,还有模拟输入(ANALOGINPUTS)、A/D参考电压(A/D REFERENCE)及省电模式控制信号(POWER DOWN SIGNALS)等接口。需要强调的是每个数字端口都有其严格的时序关系,只有在满足时序的条件下HSP3824才能正常工作。其中尤其是控制端口,是设置并保证HSP3824良好工作状态的关键。

2.2 控制端口时序图

为确保HSP3824按照设计者的要求正确工作,关键的一点是实现HSP3824内部控制寄存器的正确读写。这些内部寄存器包括发送/接收PN 码长度寄存器,发送/接收PN码字寄存器,调制/解调方式寄存器等57个,存储了HSP3824正常工作所需的全部参数及一些内部状态。因此在每次重新上电时,都必须首先由外部控制器通过HSP3824的控制端口实现这些寄存器的正确配置,之后才能正常工作。在正常工作时,也可通过该控制端口读出内部寄存器的值,供控制器分析、监控系统运行状态,还可以在需要时通过改变寄存器的配置来调整HSP3824的工作方式。

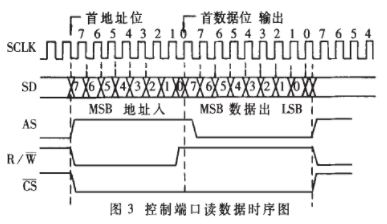

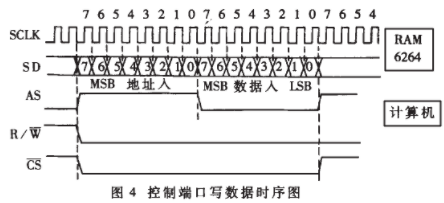

要实现内部寄存器的正确读写,必须满足HSP3824控制端口要求的时序关系。其时序分为读写两种,分别如图3及图4所示。

其中,各数据线的含义及作用如下:

SCLK:数据时钟,HSP3824在它的上升沿采样或送出数据,由它决定了读写操作的速度。需要引起注意的是SCLK应提前SD几个周期就准备好,且SCLK的速度不能大于1/2倍的系统主时钟MCLK。

SD:串行输入/输出的数据,包括寄存器的地址和值。在每次读/写一个寄存器时,SD的前8位都应该是地址,后8位为数据,且均是低位在前。

AS:区分数据线SD上送的信号是寄存器的地址还是数值,AS=1表示SD为地址,AS=0表示SD为数值。

R/:表示对于HSP3824而言,控制端口进行的是读还是写操作,RS=0为写操作,RS=1为读操作。

为使能信号,只有在=0时控制端口才能进行读写。

2.3 应注意的关键问题及其解决

HSP3824内部寄存器的读写除要求满足以上条件外,还必须满足如图5所示的HSP3824主时钟MCLK和数据时钟SCLK之间的时序关系[2]。

从图中可以看出此条件要求很高,特别是因为SCLK是由外部控制器给出,而MCLK是由一个晶振送给HSP3824的工作时钟,两者之间没有任何逻辑上的关系。因此必须采取一些额外的措施来解决此问题。

在硬件上,可增加如图6所示的电路。其中DCLK由外部控制器提供,由晶振提供。利用的反相信号CLK的上升沿(即MCLK的下降沿)触发DCLK,输出SCLK。同时CLK再经过一级反相器,得到MCLK。图中的D触发器和反相器都需要选择快速的74F系列。这样得到的MCLK和SCLK才能满足图5所示的条件。同时,可以在软件上采取些措施,如每写一个寄存器之后马上读该寄存器,并与预期值比较,若不符则重新写入,否则继续下一个寄存器的读写。通过以上两方面的措施,可确保寄存器的正确配置。

HSP3824的工作速度由MCLK决定,这个工作速度可以很高(高达44MHz)。因此,在确定的工作速度下,必须要求MCLK无抖动,特别是无毛刺,否则HSP3824会产生误动,致使工作状态不正常。可通过在MCLK送入HSP3824之前串接一个小电阻,对地并接一个小电容来防止毛刺的干扰。

3 利用HSP3824实现扩频通信的应用举例

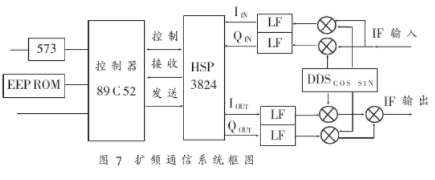

在HARRIS公司研制的24GHz天线芯片组中包括与HSP3824配套使用的中频调制解调器、频率综合器、上下变频器及双工器等芯片。但其价格昂贵,不适用于现有的工程项目。故笔者仅利用了HSP3824芯片,自行设计了其它相关电路,实现扩频通信模块。其中利用单片机89C52作为控制器,控制整个系统工作状态及实现基带数据处理;利用EPROM及D/A变换器构成直接数字频率综合器(DDS),实现中频调制解调;其它外围电路包括地址锁存器、静态RAM、EEPROM及其它辅助电路。系统框图如图7所示。

在图7中,计算机完成两个功能。其一是模拟以后实际工程中的数据采集单元或控制中心,利用它的RS232接口与89C52通信[3],提供或接受数据;另一个功能就是用作将来在现场调整一些参数的设置,包括扩频码长度的选择、对应的扩频码、数据率、功率等。其中对扩频码及其长度,通信的数据率这几个参数的调整,实际上是改变HSP3824内部寄存器的设置。其工作流程主要是工作人员通过计算机的人机界面设定满足实际条件的参数,利用计算机的串行通信口遵循RS232C协议,将命令传达至89C52。单片机利用这些收到的参数去修改HSP3824内部对应的寄存器,同时将这些参数存储在 EEPROM中。之后系统将一直维持这些选定的参数设置,直至下一次被修改。

以直接序列扩频通信基带处理器HSP3824为核心设计了扩频通信模块,并使之工作在较低频率及数据率上,实践证明其外围电路简单,性能可靠。同时也说明HSP3824具有广泛的应用领域,其处理的数据率可以从低至几千,到高达几十兆;并且对它的控制简单、灵活,可动态调整若干参数,实现最有效的应用;若结合其测试功能及输入信号强度检测和信道空检测功能,可以设计出功能更强大、更灵活、可靠的产品。但它也有其固有的缺点,主要是扩频码长较短,不能获得较高的扩频增益,限制了系统的抗噪声及抗多径效应的能力。以上优缺点需要设计人员综合考虑,以充分发挥其功能,设计出最佳的产品。

责任编辑:gt

- 处理器

+关注

关注

68文章

18815浏览量

226462 - 封装

+关注

关注

124文章

7542浏览量

141977 - 无线通信

+关注

关注

57文章

4386浏览量

143033

发布评论请先登录

相关推荐

扩频通信理论基础+主要介绍bpsk的调制

扩频通信技术 -电子书(共六章)

扩频通信技术教程

扩频通信系统简介

扩频通信技术及应用

什么是扩频通信,扩频通信的定义

小波在扩频通信中的应用

m序列、Gold序列和正交Gold序列的扩频通信系统仿真研究

DDS芯片AD9854及其在扩频通信中的应用_胡淑均

扩频通信的基本原理(SystemView仿真)

HSP3824直接序列扩频基带处理器的功能特点及在扩频通信中应用

HSP3824直接序列扩频基带处理器的功能特点及在扩频通信中应用

评论