来源:现代电子技术 作者:张剑峰 钱晶晶 谈慧宇 高进涛

引 言

随着个人计算机的蓬勃发展、因特网的演进与电子商务的冲击,市场对安全与个人隐私保护有了强烈的需求。智能卡拥有轻便与安全的特性,在网络上的安全付款、网络连接的安全控管与电子签章等应用领域扮演重要角色。我国已有不少信息安全应用系统借助智能卡来记忆系统运作所需的秘密信息,并利用智能卡具有的计算能力提升系统安全,智能卡正逐步取代磁卡而广泛应用于金融及其他相关产业。

随着对智能卡的攻击方法的不断发展,特别是随着近年来许多新型的攻击智能卡技术被公开发表,智能卡的安全面临巨大挑战。这些攻击技术能容易地以低价设备取得的信息,如电力消耗、执行时间、故障时的输出与输入行为、辐射、电力尖峰情形等信息攻击智能卡。其中,差分功耗分析(Differential Power Analysis,DPA)就是一种很有效的能量攻击方法,其主要是借助统计方法来提取与密钥有关的信息,实现过程比较复杂,但对攻击者的智能卡专业技术水平的要求并不是很高,DPA对智能卡中相关的内嵌加密算法的成功攻击已经被广泛报道。

智能卡是一种在发卡后可下载应用程序的公开平台架构,所以为了防止伪卡与保护持卡人,智能卡必须具有高安全性和高可靠性。VISA国际组织规定智能卡必须符合最高的安全技术层次要求,不但其内嵌储存体和总线上传递的数据都要求加密,而且智能卡至少要提供一个以上的对策防止简单功耗分析(Simple Power Analysis,SPA)与DPA攻击。

1 智能卡芯片架构

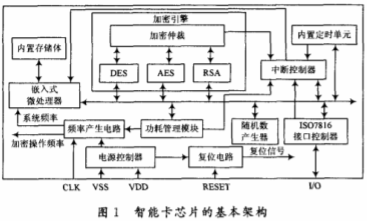

智能卡芯片架构如图1所示,主要由如下模块构成:

IDTH: 544px; HEIGHT: 363px“ height=”629“ alt=”“ src=”http://www.eefocus.com/data/09-06/49963_1246065139/1246065172.jpg“ width=”1034“》

(1)嵌入式微处理器:可控制硬件执行相关的指令完成加解密操作。其一般内置有存储器加解密单元,可通过其存取存储体数据;并通过硬件防火墙管制应用程序存储体。

(2)内置存储体:智能卡的存储体分为SRAM,E2PROM与ROM三块区域,其中ROM存放智能卡操作系统、执行环境等程序及数据;E2PROM存放用户定制代码,给不同的用户、不同的应用提供灵活的选择;SRAM为执行系统操作提供临时空间。

(3)复位电路:用于产生系统复位信号,其输入来自RESET引脚输入的外部复位信号。

(4)随机数产生器:随机数在智能卡的安全性上扮演着重要角色,密钥生成、数字签名、认证和鉴别及各种安全通信协议都离不开高质量的随机数。该模块主要产生无法预测的高质量加密用数据。

(5)ISO7816接口控制器:为智能卡与读卡器数据交换的重要接口,主要是硬件支持由ISO7816制定的T=0及T=1两种协议,T=0负责传送字符(Charac-ter);T=1则负责传送区块(Block)。

(6)中断控制器:用来接收定时单元、加密引擎、接口控制器的中断要求,并传送“中断”信号给微处理器,通知微处理器外围模块已完成指定工作或有事情发生。

(7)内置定时单元:主要当作看门狗定时器用,用以监督系统的运作,监控内部应用程序是否正确执行。若发现程序运行错误,就会给中断控制器一个中断信号,使智能卡进入暂停状态,一直要等到重置信号出现才恢复正常运行。

(8)电源控制器:内置的电压传感器和控制电路为其他模块提供稳定、安全的电源供应。

(9)功耗管理模块:智能卡对功耗的要求很高,该模块是为达到节省电源的目的设计的省电装置,其带有停止和省电两种工作模式。其中,停电模式支持ISO7816-3的频率停止模式,以降低整个系统的电源消耗;省电模式则根据系统不同模块工作特点规划了各模块的工作顺序及状态,使工作时间互斥的模块中的一部分工作时,另一部分工作在睡眠状态,从而达到降低系统整体功耗的目的。

(10)频率产生电路:智能卡作为一个复杂的SoC芯片,其系统工作频率和加密操作频率是不同的,为此一般的智能卡内部都有PLL频率产生电路。其频率来自CLK脚输入的外部频率,产生供微处理器与加密引擎中各种加密协处理器使用要求的频率。

(11)加密引擎:智能卡的加密引擎中嵌入了能实现多种加密算法的协处理器核,使其可以支持一般的加密算法包括:RSA,DES,AES。该模块主要包括:

加密仲裁 根据系统不同用途下的不同加密操作要求,通过相关的控制指令管理不同的协处理器工作。DES协处理器 支持数据加密标准(Data E-ncryption Standard,

DES)。以56 b密钥为基础的密码块加密技术,DES使用56 b密钥对64 b的数据块进行加密,并对64 b的数据块进行16轮编码,结果为64 b的密文。

AES协处理器 支持高级数据加密标准(Ad-Vanced Encryption Standard,AES)。使用的是一个迭代型分组密码,对加密来说,输入是一个明文分组和一个密钥,输出是一个密文分组;分组长度和密码长度都可变,可以独立指定为128 b,192 b或256 b。

RSA协处理器 支持公开金钥加解密系统。RSA主要是指数的运算,是基于大质数的因数分解的公匙体系,简单来讲就是两个很大的质数,一个作为公钥,另一个作为私钥,如用其中一个加密,则用另一个解密。密钥长度从40~2048 b可变,密钥越长,加密效果越好,但加密、解密的开销也就越大。

智能卡的ASIC设计,主要模块如加密引擎中所涉及的加解密协处理器、嵌入式微处理器等在市场上都由相关的IP核提供,这些IP的设计都采用了相关算法实现了抗DPA攻击,具有很好的安全性。但是将上述IP整合及其他模块的设计上必须注意采取抗DPA攻击措施,才能保证智能卡的高安全性。

2 DPA攻击原理

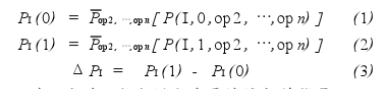

在一个没有任何抗DPA攻击的加密芯片上指令的执行顺序和相关数据处理操作会影响功率消耗,尽管这种影响会被噪声消耗,但是靠统计的方式还是可以看出端倪。DPA攻击技术以功率消耗图为基础,再以统计方式推演主密钥的攻击技术,其原理是智能卡在执行加密过程中会消耗能量,产生电磁辐射,通过使用特殊的电子测量仪和数学统计技术,就可以检测和分析这些变化,从而得到芯片中的特定关键信息。智能卡执行一条指令消耗的能量与指令的操作数相关,某一指令I的执行所消耗的平均功耗P如下式所示:

式中:PI表示指令I执行过程中平均消耗的能量;op1,op2,…,opn表示I的操作数;PI(0)和PI(1)分别表示op1取0和1时执行指令I消耗的平均功耗。可见,PI与op1相关(△PI≠0)。

另外,考虑到智能卡采用的是CMOS工艺,其功耗主要是动态功耗Pd,而Pd大小如下面公式所示:

式中:f是工作频率;CL是输出节点的集总负载电容;VDD是电源电压;α是电路开关活动因子(电路翻转率)。可见CMOS逻辑门功耗大小与α密切相关,所以,电路中的数据的0与1状态与电路的功率信号必然具有一定的相关性。

综上所述,加密用密钥与电路功耗存在相关性,DPA攻击就是从这种相关性人手,最终实现对密钥的破解。下面以AES算法为例,介绍DPA攻击的过程:

(1)随机生成大量明文;

(2)加密这些明文,并记录下加密操作时的能耗曲线,求得这些曲线的平均;

(3)关注第一轮S2盒的输出,设输出的第一比特为b,对第一轮子密钥的第一个字节进行猜测,并用其与相应的明文计算出S2盒的输出;

(4)根据b的值,将能耗曲线按照b=0和b=1分为两类;

(5)计算出这两类的平均能耗曲线,并将二者相减,求得差分能耗曲线;

(6)观察步骤(2)和(5)生成的能量曲线。若密钥猜测正确,那么步骤(4)的分组就是正确的,步骤(5)生成的差分能耗曲线将和步骤(2)生成的平均能耗曲线呈现较大的差别,差分能耗曲线中将出现峰值。因此,攻击者通过观察峰值来判断密钥的猜测是否正确;

(7)重复步骤(3)~(6),得到其他轮的子密钥。DPA攻击易于实现,一个完全不懂得智能卡技术的编程人员完全可以利用专用程序对没有DPA防范的智能卡实现攻击。高安全性的智能卡必须采取相应的防范措施以实现抗DPA攻击。

3 抗DPA攻击的设计

目前各种密码系统的算术逻辑运算单元的VLSI设计已得到较为广泛的研究,如何在其他方面实现抗DPA攻击是值得进一步深入研究的问题。下面从随机数产生器、组合和时序逻辑防DPA设计介绍智能卡抗DPA攻击的电路实现。

3.1 随机数产生器设计

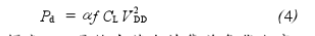

对于智能卡的DPA攻击,主要是利用在卡上嵌入式微处理器运作时,某个特定指令的执行或数据存取所消耗功率,在供应电压源上所表现特定的电流频谱提供的有用信息。故可以通过外加额外的电路造成额外的电流消耗,从而改变电流频谱以达到抗DPA攻击。同时额外的电流消耗电路必须通过采用随机数随机的方式,产生随机数消耗电流,以达到芯片消耗电力无法预测性,使其不能被分析与统计。

为此,可以在随机数产生电路中设计如图2所示的随机数消耗电路,电路由比较器、移位寄存器、译码器组成;当电阻噪声产生的噪声电压经过放大器、比较器后,产生“1”或“0”数字信号,存入移位寄存器,这样寄存器内的值已经类似混沌式RNG所产生的随机数,此随机数经译码器编码后,控制三态充放电缓冲器的充放电个数,最终达到以随机数控制电流消耗的目的。

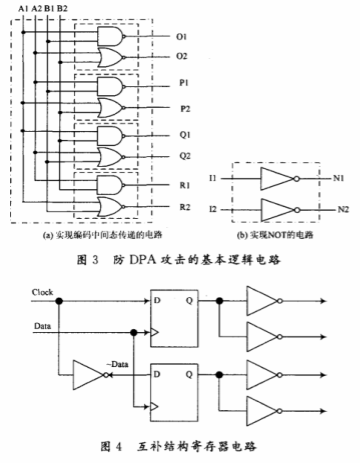

3.2 组合逻辑防DPA攻击设计

防DPA攻击的主要目的是使电路特性在运算时保持相同,而保持电特性相同很重要的一点是使翻转的晶体管数量在任何运算步骤中都是一个常数。为实现这个目的可在电路运算步骤之间增加一个中间步骤,这样能防止有用信息从功耗分析中泄漏出去。最简单的中间步骤设置是在输入参数和电路运算完成之后设置系统中间值。

为此,参考异步逻辑电路的双轨编码方式中对信息的每一位用两根信号线进行编码的方式。采用两位信号线的组合值“01”和“10”来表示数字逻辑的“真”和“假”,而组合值“00”和“01”则为中间值。这样的编码方式下,设计的基本逻辑单元电路如图3所示。

如图3(a)电路对于输入A(A1A2)和B(B1B2),输出只有O1O2和R1R2有效,当输入A1A2B1B2为0000或1111时,输出O1O2和R1R2的值是11或00,这样实现了编码中间态的传递。而当输入A1A2B1B2为有效数据0101,0110,1001和1010时,输出O1O2和R1的值就得到相关的NAND,AND,NOR和OR四个逻辑功能;其中,输出O1O2→NAND,O2O1→AND,R1R2→NoR,R2R1→OR。至于NOT的实现如图3(b)的电路所示。所以,上述基本的逻辑电路足以实现复杂的数字组合逻辑运算功能。

3.3 时序逻辑防DPA攻击设计

针对差分功耗分析,除了利用增加电路噪声以降低差分功耗分析的信噪比的防御方案外。通过减小差分功率信号的值,同样可以降低差分功耗分析的信噪比;若电路不同状态下的功率差异趋于零,则差分功耗分析将失效。于是基于上述思路,在时序逻辑电路设计上可采用如图4所示的互补结构寄存器电路。

设寄存器初始状态相同,输出负载相同,时钟沿赋值,如图4不论输入为O或1,两个互补寄存器必是一个翻转,另一个不翻转,因此总的功耗在两种情况下没有差别。

另外,对于采用前面所述的双线信号编码方式,在时序逻辑电路的设计上,可采用在输入任何有效的数据01和10之前,都先把寄存器设置为00或11中间态的协议。这样,无论进行何种操作,则时序逻辑中相关的寄存器都只有一个寄存器翻转,有效地防止了寄存器在数据传输过程中的信息泄漏。

4 结 语

智能卡是一种高安全性、高可靠性和复杂的片上系统,具有抗功率分析攻击、时间分析攻击和故障分析攻击的能力,但在一些新型的智能卡攻击技术下其安全受到巨大的挑战,例如DPA攻击。本文针对DPA攻击智能卡的特点,在智能卡的硬件电路上进行了抗DPA攻击的设计,采用此设计,再结合一些软件上的抗DPA攻击措施,就能构成一个完善的智能卡安全体系结构,能十分有效地保证智能卡免受DPA攻击。

责任编辑:gt

-

嵌入式

+关注

关注

5082文章

19104浏览量

304777 -

计算机

+关注

关注

19文章

7488浏览量

87847 -

微处理器

+关注

关注

11文章

2258浏览量

82400

发布评论请先 登录

相关推荐

采用智能卡平台的LKT系列加密IC介绍

基于FPGA的身份认证智能卡设计

基于能量攻击的FPGA克隆技术研究

SCDN的抗CC攻击和抗DDoS攻击防护是什么?

RFID射频功能的手机智能卡怎么实现?

基于ECC的远程用户智能卡认证方案

基于可信计算的Java智能卡的设计与实现

智能卡操作系统研究和实例分析

智能卡技术_王爱英

在FPGA平台上实现对DPA攻击的电路级防护技术

智能卡抗DPA攻击电路的三种实现方案研究与比较

智能卡抗DPA攻击电路的三种实现方案研究与比较

评论