行为语句描述电路的外在行为,外文文献关于行为描述的定义是:

1.仅仅描述“What do”,而不描述(或几乎不描述)“How to do”,的HDL代码,为行为描述

2.不仅描述“What do”,部分描述(少量描述)“How to do”,的HDL代码,为数据流描述

3.不仅描述“What do”,还有全部充分的描述“How to do”,的HDL代码,为结构化描述

注意英文“What do”对应中文的“做什么”;“How to do”对应中文的“如何去做”

在HDL语言系统中,行为语句(例如if,case)必须放置在特定的容器中,EDA才加以识别,用于综合。这种特定的容器称为行为体(Behaviour Body)。Verilog中常用的循环行为体为always语句块。

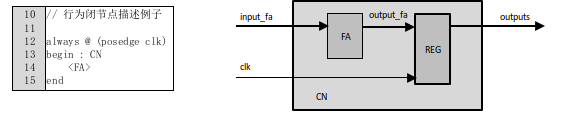

闭节点描述

根据Verilog编译器的定义:循环行为体中,信号敏感表在某些情况下,与综合有关(按照EDA的经典理论,循环行为体的信号敏感表与综合无关)。若描述闭节点(沿敏感),其定义为:信号敏感表中,有且有一个未被引用的沿敏感信号,则该循环体的FA输出端,将得到生成寄存器:

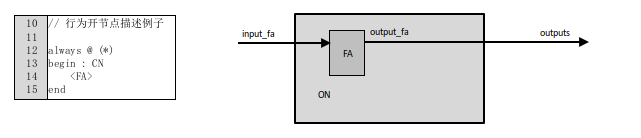

开节点描述

根据定义,若循环行为体的信号敏感表中没有沿敏感信号,或者虽然有,但全部被引用,得到开节点ON描述:

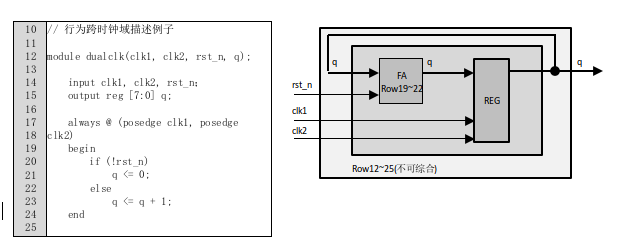

跨时钟域描述

若循环行为体的信号敏感表中有多于一个未被引用的沿敏感信号,则构成跨时钟域描述,此时,EDA通常会直接报错(需要设计者自己解决跨时钟域问题)

编辑:jq

- eda

+关注

关注

71文章

2632浏览量

171888 - 编译器

+关注

关注

1文章

1594浏览量

48865 - HDL代码

+关注

关注

0文章

5浏览量

2062

原文标题:FPGA学习:行为语句的可综合性

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先登录

相关推荐

一次性使用无菌脑积水分流器综合性测试仪

焊锡膏的综合性能该如何进行评估?

assign语句和always语句的用法

多协议网关BE115是一款多协议转多上行协议的综合性转换网关

深入探讨嵌入式C编程的goto语句

单片机if是什么语句

select语句的基本语法

什么样的高压电机软启动柜才能算得上综合性价比高

简述行为语句的可综合性

简述行为语句的可综合性

评论