作者:徐孟祥,杨飞,张尔扬

引言

低压差分信号传输LVDS(Low Voltage Differential Signaling)是高速、低电压、低功率、低噪声通用I/O接口标准。这种信号传输使用非常小的信号幅度(典型值为350mV),通过一对平行的PCB走线或平衡电缆传输数据。这对平行差分信号线的电流及电压振幅相反,噪声同时耦合到2条信号线上。由于采用差分输入方式,输入信号只与2个信号的差值有关,因而可将共模干扰抑制掉。另外,由于2条差分信号线距离很近,电流传输方向相反,其磁场相互抵消,电场相互耦合,因而与单线传输相比,电磁辐射小得多。

LVDS已广泛应用于接口器件和现场可编程门阵列(FPGA)、专用集成电路(ASIC)中,采用LVDS的系统成功实现了高速互连。然后,并非所有的LVDS I/O接口都有良好的性能。例如,一些ASIC或FPGA的LVDS I/O可能不象标准器件中的LVDS I/O那样适合在PCB板上驱动差分迹线(trace)。由于PCB板布局存在的问题,甚至导致设计良好的标准器件的信号传输质量变差。当用ASIC或FPGA等作为系统核心件时,有时不可能使器件尽可能靠近连接器放置,这样会造成迹线变线、反射增大、损耗增加。为了消除互连中存在的问题,国家半导体公司推出一系列体积小巧的缓冲器。文中将对其LVDS超高速交叉点开关SCAN90CP02的功能及应用进行介绍。

1 SCAN90CP02简介

SCAN90CP02型电路是美国国家半导体公司推出的1.5Gb/s的2x2低压差分信号传输vwin 交叉点开关(crosspoint switch)。其高速数据通路和直通(flow-through)引脚可使电路内部的抖动达到最小。当信号在有损的背板和电缆上传输时,其可配置的预增强功能(0/25/50/100%可选)能克服外部ISI(Inter Symbol Interference,符号间干扰)抖动的影响。其差分输入可连接到LVDS和Bus LVDS信号上,也可与共模逻辑(CML)和低电压正射极耦合逻辑(LVPCL)等信号电平相连。SCAN90CP02要用非块式交叉点结构,可配置为1:2时钟或数据分配器、2:1冗余复用器、交叉功能及用于信号增强和短线隐藏的双缓冲器。图1是SCAN90CP02的内部方框图。

SCAN90CP02集成的IEEE 1149.1(JTAG)和1149.6测试输入电路TAP(Test Access Port)支持单端LVTTL/CMOS和差分LVDS PCB互连的可测试性。这些功能有助于缩短测试时间,降低测试与开发方面的成本。电路采用3.3V电源、CMOS工艺和LVDS I/O,确保其在整个工业级温度范围(-40℃到+85℃)内实现高性能和低功耗。

SCAN90CP02可以真正地消除抖动,从而提高系统的可靠性,使用户能用成本较低的线路实现互连。由于SCAN90CP02设有预增强功能,因此不但可以执行正常的开关功能,而且可作为缓冲器使用,以便将现有的FPGA、ASIC及串行/解串器(SerDes)等的LVDS信号放大。另外,该电路的LVDS输出不支持多站式(multidrop)BLVDS环境。

SCAN90CP02的特点如下:

●每通道的传输速率达1.5Gb/s。

●低功耗,在双中继器模式下,最高速率时的电流仅为70mA。

●低输出抖动。

●可配置的预增强功能(0/25/50/100%)可驱动有损耗的背板和电缆。

●具有直通(Flow-through)引脚引出线。

●LVDS/BLVDS/CML/LVPECL输入,LVDS输出。

●适用IEEE 1149.1和1149.6标准。

●单电源3.3V供电。

●可对输入和输出进行单独控制以降低功耗。

●工业级温度范围(-40℃至±85℃)。

SCAN90CP02采用28引脚LLP封装或32引脚LQFP封装。

电路的预增强功能用于补偿远距离传输或者有损耗的传输媒质。为使功耗最小,电路为每个输出提供了独立的引脚。而且预增功能是可编程设备的。

2 SCAN90CP02的应用

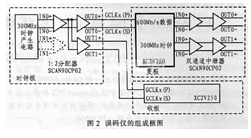

在笔者的设计项目中,需要用高达600Mb/s的速率来传送数据,由发射机和接收机完成数据收发、调制及信道匹配等任务。为检验整个通信系统数据传输质量的好坏,笔者另外设计了一台高速误码率测试仪。该测试仪由3块电路板组成,分别是时钟产生板、发板和收板。在时钟产生板和发板上各用了一块SCAN90CP02,一是可使电路板上的输出信号尽可能靠近连接器,减轻板上核心电路的布线压力,使其位置放置更加自由;二是完成电平转换任务,将LVPECL电平转换成LVDS电平;三是补偿走线的损耗,保证信号有较好的传输质量。该误码仪的框图如图2所示,图中重点突出了SCAN90CP02的连接方式。以下详细介绍该测试仪中的各种电路板。

(1)钟板。时钟板的SCAN90CP02配置成1:2分配器方式,EN0、EN1、SEL0和SEL1都置为低电平。时钟板产生的300MHz时钟信号为LVPECL电平,经SCAN90CP02转换成2路LVDS电平,分别送往误码仪的发板和收板。

(2)发板。发板以Xilinx公司的VirtexII系列XC2V250型电路为核心,由一些外围电路和控制电路组成,完成伪码产生、数据成帧、并串变换等功能。输出的600Mb/s数据和300MHz时钟经SCAN90CP02中断通过连接器送到发射机。SCAN90CP02配置成双通道中断器方式,SEL1置高电平,其他控制端置电平。

(3)收板。收板以Xilinx公司的VirtexII系列XC2V250型电路为核心,由一些外围电路和控制电路组成。实现帧同步、数据恢复、串并变换、比较计数和误码统计显示等功能。

SCAN90CP02的预增强控制端采用拨码开关来选择高、低电平,以增加设计的灵活性。

3 结束语

在许多应用中特别是用高损耗的背板及电缆连接时,一些电路(如ASIC和FPGA等)的驱动能力往往不足,这就需要使用带有预增强功能的电路(如SCAN90CP02)预先将信号放大,这样不但可以保证接收器获得足够的输入信号电压,而且还可增大传输距离,改善信号质量。特别是采用LVDS传输方式时,其抗干扰能力大大增强,同时也降低了电磁辐射。

责任编辑:gt

-

FPGA

+关注

关注

1629文章

21729浏览量

602958 -

集成电路

+关注

关注

5387文章

11530浏览量

361612 -

开关

+关注

关注

19文章

3136浏览量

93598

发布评论请先 登录

相关推荐

美国国家半导体两款低功率LVDS 2x2交叉点开关电路

SCAN90CP02,pdf datasheet (1.5

MAX4989 USB 2.0高速4选2交叉点开关

SCAN90CP02型LVDS交叉点开关的功能及应用

SCAN90CP02 具有预强制和 IEEE 1149.6 功能的 1.5 Gbps 2x2 LVDS 交叉点交换器

LVDS 4x4交叉点开关SN65LVDS250数据表

DS25CP152 3.125Gbps LVDS 2x2交叉点开关数据表

DS25CP152Q汽车应用3.125 Gbps LVDS 2x2交叉点开关数据表

DS25CP102Q汽车应用3.125 Gbps 2X2 LVDS交叉点开关数据表

DS25CP104A/CP114 3.125 Gbps 4x4 LVDS交叉点开关数据表

DS10CP154A 1.5Gbps 4x4 LVDS交叉点开关数据表

DS90CP22 800 Mbps 2x2 LVDS交叉点开关数据表

DS90CP02 1.5 Gbps 2x2 LVDS交叉点开关数据表

DS10CP152 1.5Gbps 2X2 LVDS交叉点开关数据表

DS10CP152Q汽车1.5 Gbps 2X2 LVDS交叉点开关数据表

LVDS超高速交叉点开关SCAN90CP02的性能特点及应用分析

LVDS超高速交叉点开关SCAN90CP02的性能特点及应用分析

评论