在本篇博文中,我们将探讨如何在 Vitis 中调试 Zynq UltraScale 器件启动镜像。这些启动镜像包括 ARM 可信固件 (ATF) 和 U-boot。

本篇博文乃是系列博文中的一篇,此系列博文旨在探讨如何在 Petalinux 镜像中调试各种组件。

启动镜像调试是任何定制板启动过程中不可或缺的一环,希望本篇博文能够帮助用户完整完成定制板启动镜像的调试工作。即使您使用的是开发板,本篇博文也将能够提供有关启动镜像在 Zynq UltraScale 器件上的工作方式方面的诸多实用见解。

启动镜像的生成途径多种多样。用户可以使用 PetaLinux/Yocto,或者也可以从 GiT 源代码手动构建镜像。本文将演示如何使用 PetaLinux 2020.1 来为 Zynq UltraScale 器件创建启用调试功能的启动镜像。

PetaLinux 流程:

在此次演示中使用的是 ZCU104 板,但其中步骤应适用于所有 Zynq UltraScale 器件。

在 images/Linux 文件夹中提供的 u-boot.elf 不具有在 Vitis 中进行调试所需的符号信息。因此,我们将使用 PetaLinux 内的工作目录下的 u-boot 二进制文件。

并且 PetaLinux 移除了其中间文件以节省磁盘空间,因此我们需要在 PetaLinux 工程中禁用此功能。

下列步骤演示了用户如何获取启用调试功能的 ATF 和 U-boot:

petalinux-create -t project --template zynqMP -n linux_image

cd linux_image

注: 很遗憾,在 PetaLinux 存在 1 个已知问题,即无法将 debug=1 传递到此处的 makefile。用户可以使用此处所述的变通方法来手动添加该值。

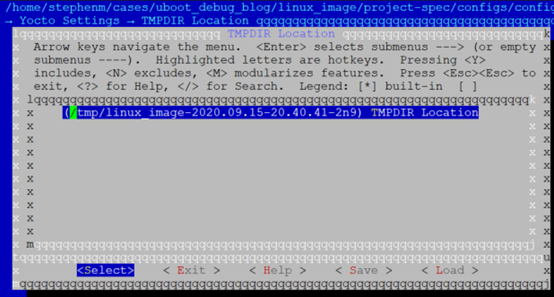

用户还应注意 TMP 目录:

退出“配置 (Config)”屏幕并单击“Save”以保存。

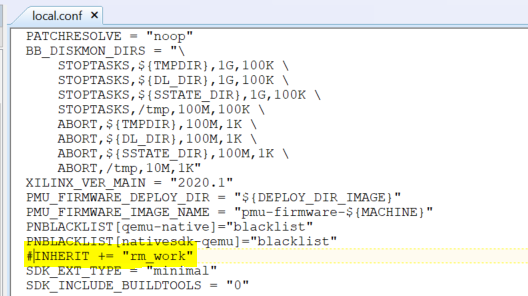

如上所述,PetaLinux 提供的 u-boot 可执行文件不具有调试所需的符号信息。用户可以通过修改 build/conf 文件夹下的 local.conf 文件来阻止 PetaLinux 移除中间构建文件。

创建任何构建时都会创建 build 文件夹,因此我们可以执行 petalinux-build,随后使用 Ctrl + c 在创建此文件时停止操作。打开 local.conf 文件并注释掉以下行:

现在,只需构建启动镜像并使用 PetaLinux 创建可启动镜像 (BOOT.BIN) 即可

petalinux-build -c bootloader

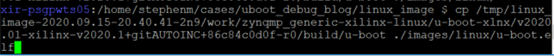

完成构建后,将 u-boot 重命名为 u-boot.elf 并从 tmp 文件夹复制到 images/linux 文件夹中:

下一步,使用 PetaLinux 创建可启动镜像 (BOOT.BIN)

cd images/linux

petalinux-package --boot --u-boot

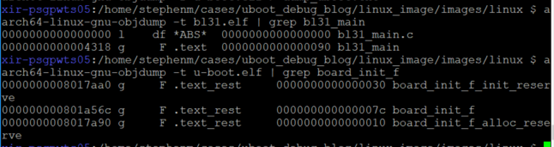

作为完整性检查,我们还可测试可执行文件以确认其中包含符号信息:

在 Vitis 中执行调试:

我发现调试启动镜像最简单的方法是将启动镜像加载到 SD/QSPI 上,并在运行目标上执行调试。

启动 Vitis 并关闭欢迎屏幕。

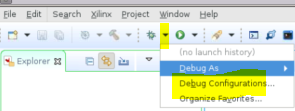

创建新的“调试配置 (Debug Configuration)”:

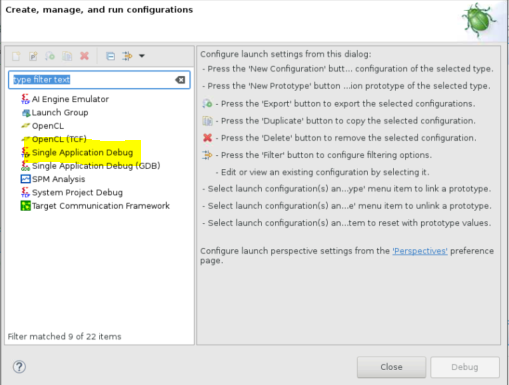

双击“单应用调试 (Single Application Debug)”:

将“调试类型 (Debug Type)”设置为“连接到运行目标 (Attach to Running Target)”:

注: 由于我当前使用远程连接,因此还需一并设置远程连接。

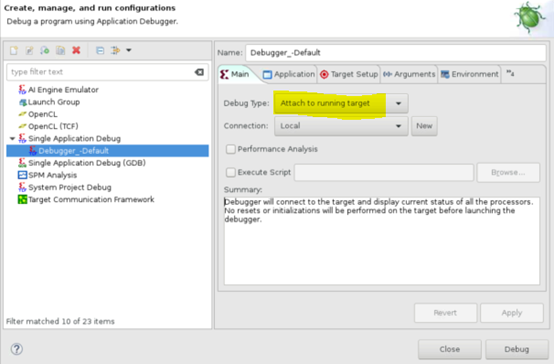

选择“应用并调试 (Apply and Debug)”。这样即可打开调试透视图。

您可以看到其中 Cortex A53 正在运行(我们的启动镜像)。

重定位前的调试:

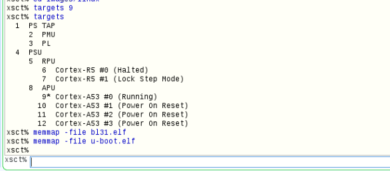

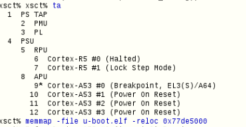

展开赛灵思软件命令行工具 (XSCT) 窗口。

我们要在其中将符号文件传递给 Cortex A53 #0 以供 ATF 和 U-Boot 使用。

在 XSCT 中使用 memmap 命令设置符号文件:

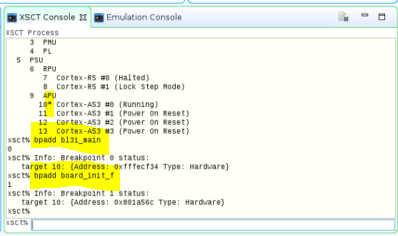

然后即可在 ATF 和 U-Boot 中添加中断点。

我将 ATF 中的中断点设置在 bl31_main,将 U-boot 中的中断点设置在 board_init_f:

如果将板掉电并重新上电,则会在 ATF 中看到中断点被命中。

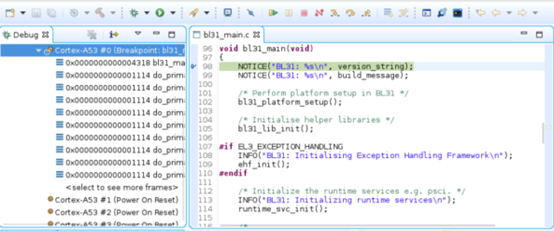

随后,用户可以执行恢复 (resume)、单步进入 (step into)、单步跳过 (step over) 等:

用户可以单步执行此处代码。例如,用户可以使用其中的 setup_reloc 功能来查找 uboot 重定位地址(或者使用 bdinfo)。

重定位地址因用户而异,我这里的重定位地址为 0x77DE5000。

重定位后的调试:

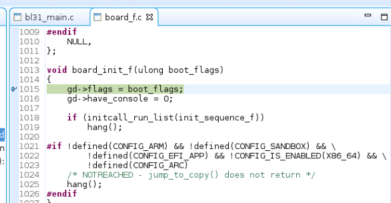

uboot 代码将对自身进行重定位,由于我们已映射符号文件存储器,因此,该重定位地址是错误的。

由此导致我们需要传递重定位地址以便调试器能够对此进行补偿:

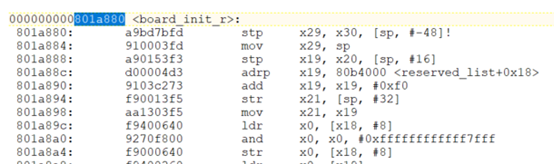

让我们使用 board_init_r 功能。

这是重定位后处理功能:

重定位后,board_init_r 地址将变为 0x77DE5000 + 0x801A880 = 0x7FDFF880。

如果我在 board_init_r 处添加中断点,即可看到实际地址符合预期:

如果此时掉电并重新上电,则将命中 ATF 中的中断点,并且此时还会命中重定位后的 U-boot。

编辑:jq

-

Linux

+关注

关注

87文章

11292浏览量

209317 -

u-boot

+关注

关注

0文章

121浏览量

38220 -

Vitis

+关注

关注

0文章

146浏览量

7421

原文标题:PetaLinux 镜像调试系列-在 Vitis 中调试 ARM 可信固件和 U-boot

文章出处:【微信号:FPGA-EETrend,微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

针对ZYNQ+ULTRASCALE的FPGA供电的一些疑问求解答

AMD/Xilinx Zynq® UltraScale+ ™ MPSoC ZCU102 评估套件

为Xilinx® Zynq®UltraScale™系列多处理器中的VCCINT_VCU轨供电

使用TPS65086x PMIC为Xilinx Zynq UltraScale MPSoC供电

正点原子ZYNQ7015开发板!ZYNQ 7000系列、双核ARM、PCIe2.0、SFPX2,性能强悍,资料丰富!

如何在 TIDK 器件和客户产品 HS 器件中完成安全流程

[XILINX] 正点原子ZYNQ7035/7045/7100开发板发布、ZYNQ 7000系列、双核ARM、PCIe2.0、SFPX2!

一个更适合工程师和研究僧的FPGA提升课程

Vitis2023.2使用之—— updata to Vitis Unified IDE

Vitis2023.2使用之—— classic Vitis IDE

AMD推出全新Spartan UltraScale+ FPGA系列

通过JTAG启动Linux的方法和脚本

如何在 Vitis 中调试 Zynq UltraScale 器件启动镜像

如何在 Vitis 中调试 Zynq UltraScale 器件启动镜像

评论