航天工程领域中,星地通讯等远距离遥测遥控是嵌入式卫星数管计算机重要功能之一,利用三线制同步串行遥测遥控通道对指令和数据进行收发操作是通信链路的重要环节。

目前许多处理器芯片都已集成了同步串行接口,但基于三线制同步串行接口的处理器并不多。利用传统设计方法所实现的三线制同步通信硬件电路接口虽然能满足一般工程设计要求,但在“低成本、小体积、低功耗和灵活性”设计理念的推动下,传统设计显然弊大于利。采用可编程逻辑器件CPLD/FPGA技术,对三线制同步串行通信接口电路进行结构设计与实现,可以大幅度减小系统体积,降低功耗,提高设计的灵活度。同时,还可以在其中增加其他逻辑功能模块,并能很方便地应用到相关的嵌入式系统中。

1 三线制同步串行通信机理

三线制同步串行通信时,发送端和接收端必须使用共同的时钟源才能保持它们之间的准确同步。为达到准确同步的目的,其中一个方法就是采用编码和解码的原理,即在发送端利用编码器把要发送的数据和发送时钟组合在一起,通过传输线发送到接收端,在接收端再用解码器从数据流中分离出接收时钟。常用的编码解码器有曼彻斯特编码解码及NRZ-L码。本文中收发信号采用的码型是NRZ-L码。

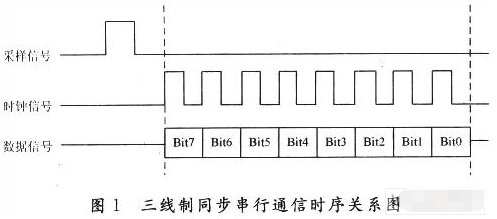

三线制同步串行通信主要包括三个信号:采样信号(也叫帧同步信号)、时钟信号和串行数据信号,其时序逻辑关系如图1所示。

从图1可看出,数据接收或发送时,首先帧同步信号先触发一个瞬时启动脉冲,之后保持低电平有效,时钟信号紧随其后,数据在时钟信号的上升沿保持稳定,并开始采样和传输,每个时钟周期收发一位字符数据,串行数据成批连续发送和接收。

2 三线制同步串行通信控制器接口结构设计

2.1 基于传统设计的硬件电路接口实现

在三线制同步串行通信控制器接口的传统硬件电路设计中,需使用多片元器件来实现其功能,包括:异步四位计数器、移位寄存器、8位D触发器、与门、与非门和反相器等主要功能器件,接口电路原理图在ProteI 99 SE中实现。

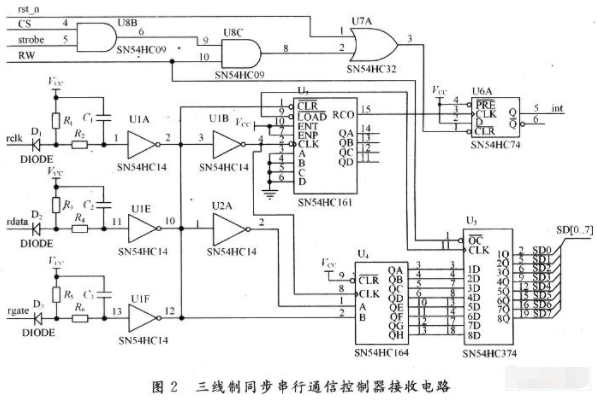

三线制同步串行通信控制器接收接口硬件电路如图2所示。

![]()

从图2中可看到,通过复位信号rst n、片选信号CS、门控信号strobe和读写信号RW等的不同组合,实现逻辑控制功能。通过异步四位计数器SN54HC161的计数功能,使得移位寄存器SN54HC164顺利进行数据的串/并转换,将8位并行数据通过8位D触发器SN54HC374锁存在内部总线上等待系统接收。在输出端,通过双D触发器SN54HC74产生中断信号int,通知系统内的微处理器进行数据接收操作。

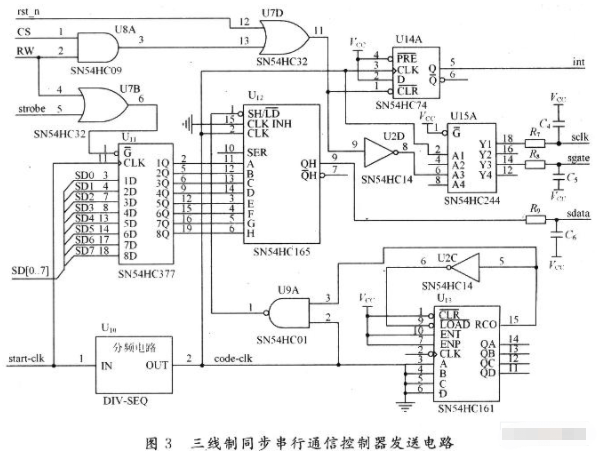

三线制同步串行通信控制器发送接口硬件电路如图3所示。

![]()

从图3可知,系统时钟start-clk通过分频电路模块产生发送时钟原始信号code-clk,用于电路的时钟状态控制。系统内的微处理器将要发送的8位并行数据通过8位D触发器SN54HC377,将数据锁存在其Q端口等待发送,然后在异步四位计数器SN54HC161的计数功能控制下,移位寄存器SN54HC165进行数据的并/串转换操作。在输出端,通过双D触发器SN54HC74产生中断信号,然后开始通过单向总线驱动器SN54HC244进行帧同步信号、时钟信号及数据的发送操作。

2.2 基于CPLD/FPGA的接口结构设计

为解决传统硬件电路元器件多,功耗大,体积大等缺点,利用CPLD/FPGA技术,同时结合VHDL硬件描述语言设计三线制同步串行通信控制器接口已成为一种必然,结合三线制同步串行通信机理,设计出了基于CPLD/FPGA的三线制同步串行通信控制器接口内部结构,其功能结构如图4所示。

整个三线制同步串行通信控制器接口的内部结构主要由时钟分频模块、系统接口控制逻辑、数据接收模块、数据发送模块等四大模块构成。

时钟分频模块主要用于数据收/发模块产生同步时钟信号。系统接口控制逻辑主要用于各种逻辑功能信号的控制,同时还可以接收_中断仲裁逻辑模块产生的中断信号,控制数据的接收或者发送操作。数据接收模块是三线制同步串行通信控制器接口进行数据接收的核心部分,其模块结构如图5所示。

数据接收流程:在帧同步脉冲信号触发下,串行数据在时钟信号rclk上升沿到来时保持稳定,并通过rdata信号线进入数据接收模块。在该模块内部,串行数据经过串/并变换,接收FIFO作为数据缓冲器,将接收到的数据锁存在VHDL程序指定的两个地址寄存器中,一个地址单元存储数据的高八位,另外一个地址单元存储数据的低八位,当数据存满这两个地址单元后,接口向系统发出一个“接收缓存满”的接收中断标志int,系统微处理器响应后,数据被全部取出,并行数据被送往系统的数据总线上,重复进行相同操作,直至连续接收完所有数据,数据接收过程结束。

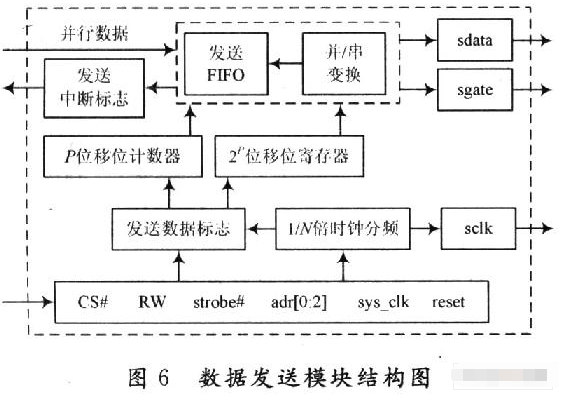

数据发送模块也是三线制同步串行通信接口进行数据发送的核心部分,其模块结构如图6所示。

数据发送流程:在sgate帧同步脉冲信号触发下,系统数据总线上的并行数据在时钟信号sclk上升沿到来时保持稳定,并通过数据发送模块开始数据发送。在模块内部,首先发送FIFO数据缓冲器,当并行数据存满该缓存单元后,数据发送模块向系统发出一个“发送缓存满”的发送中断标志int,系统微处理器响应后,并行数据从发送FIFO内读出,经过并/串变换成串行数据,最高位MSB最前,最低位LSB最后,并被送往发送数据信号线Sdata上,发送至外围设备接口,重复进行相同操作,直至发送完毕所有数据,数据发送过程结束。

3 结 语

本文在介绍了三线制同步串行通信机制基础上,首先对三线制同步串行通信接口进行了硬件电路设计,然后针对传统电路设计方式的不足,构建了基于CPLD/FPGA的三线制同步串行通信控制器接口结构,详述了各个功能模块及其工作原理,设计合理,并且满足了实际应用要求。目前,此接口结构模块已作为FPGA设计中的关键子模块被成功应用于某航天项目及其配套的硬件测试平台中。

责任编辑:gt

-

FPGA

+关注

关注

1629文章

21729浏览量

602958 -

cpld

+关注

关注

32文章

1248浏览量

169331 -

嵌入式

+关注

关注

5082文章

19104浏览量

304771

发布评论请先 登录

相关推荐

Xilinx可编程逻辑器件的高级应用与设计技巧绝版教程

可编程逻辑器件

PLD可编程逻辑器件

可编程逻辑器件基础及应用实验指导书

什么是PLD(可编程逻辑器件)

采用可编程逻辑器件实现三线制同步串行通信的应用设计

采用可编程逻辑器件实现三线制同步串行通信的应用设计

评论