时钟设计方案在复杂的FPGA设计中,设计时钟方案是一项具有挑战性的任务。设计者需要很好地掌握目标器件所能提供的时钟资源及它们的限制,需要了解不同设计技术之间的权衡,并且需要很好地掌握一系列设计实践知识。

不正确的设计或次优的时钟方案可能会导致在最好情况下较差的设计性能,或者在最坏情况下的随机和难以查找的错误。FPGA时钟资源指目标FPGA中大量与时钟有关的不同资源,如时钟类型(局部的和全局的)、频率限制和不同时钟管理器的抖动特性,以及能用于单个时钟域的时钟最大数量。本文介绍了时钟设计方案中的每个部分,并推荐了一些设计方法。

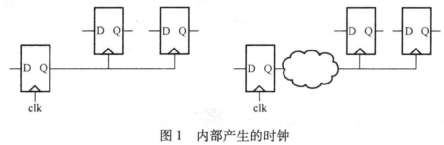

内部产生的时钟是组合逻辑或寄存器的输出,如图1所示。

组合逻辑产生的时钟可能有毛刺,会被错误地当成有效时钟边沿,在设计中会导致功能错误。因此,不要使用组合逻辑的输出作为时钟。内部产生的时钟使用通用布线资源。因此,与专用时钟布线相比延迟较长。其后果是时钟偏移增加,满足时序的过程更加困难。如果大量的逻辑使用了该内部时钟,这个问题尤为突出。公众号:OpenFPGA作为一般规则,尽量避免使用内部产生的时钟,尽可能使用专用时钟资源。

除了一些特殊电路[如双倍数据速率(DDR)的数据捕获]之外,寄存数据通常总是使用时钟的上升沿或下降沿。使用两个边沿带来的问题是由于时钟占空比可能并不总是50%,这会对电路的正常工作产生影响。

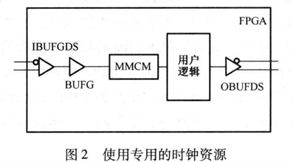

建议在频率高的情况下使用差分时钟。通常认为频率高于100MHz以上属于高频。差分时钟相比单端时钟的主要优势是共模噪声抑制,因此抗噪声性能更好。具有PECL、LVPECL和LVDS信号电平的差分时钟是高速逻辑下时钟的首选。Xilinx FPGA提供了一些用于差分时钟的专用原语:IBUFDS、IBUFGDS、IBUFGDS_DIFF、OBUFDS、0BUFTDS等(见图2)。

时钟门控是设计中通过使用控制信号,禁止或允许时钟输入到寄存器和其他同步元件上的一种方法。它能有效降低功耗,因此被广泛应用于ASIC设计中。然而,在FPGA设计中应尽量避免使用门控时钟。

不建议将时钟信号作为通用逻辑的控制、复位或数据输入。下面是这类电路的例子。

module clock_schemes(input clk1,clk2,clk3,clk4,clk5,input data_in,output reg data_out1,data_out2,data_out3,data_out4,data_out5,data_out6);wire data_from_clock, reset_from_clock, control_from_clock;/ / 时钟被用做数据输入assign data_from_clock = clk1;always @(posedge clkl) data out1 《= ~data out1;

always @(posedge clk2) data out2 《= ~data out2 & data_from_clock;

/ / 时钟被用做复位输入assign reset_from_clock = clk3;always @(posedge clk3) data out3 《= ~data out2;always @(posedge clk4, posedge reset_from_clock) if (reset_from_clock) data_out4 《= 0; else data out4 《= data in;/ / 时钟被用做控制assign control_from_clock = clk5;always @(posedge clk5) data out5 《= ~data out5;always @(*) data_out6 = control_from_clock ? data_in : data_out6;endmodule // clock schemes

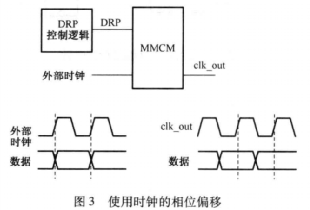

许多与FPGA接口的外设都使用与数据一样的源同步时钟。如果接口在高速下工作,可能需要对时钟边沿进行校准,以便在数据窗口的中间捕获数据。为实现动态校准Xilinx MMCM原语提供了动态重新配置端口DRP),允许时钟的可编程相位偏移。图3说明了来自MMCM的时钟被移位后,使时钟的上升沿在窗口的中间位置采样数据。

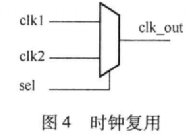

当同一个逻辑有来自不同时钟源的时钟时,需要在设计中对这些时钟源进行时钟复用(见图4)。一个例子是使用2.5MHz、25MHz或125MHz时钟的以太网MAC,选取哪种时钟取决于10Mbps、100Mbps或1Gbps的协商速度(negotiated speed)。另一个例子是电源内置自测(BIST)电路,在正常工作期间,使用了来自同一个时钟源的不同时钟信号。公众号:OpenFPGA

建议使用专用的时钟资源实现时钟复用,确保输人和输出时钟使用专用时钟线,而不是通用逻辑。参与复用的时钟频率可能彼此并不相关。使用组合逻辑实现的多路复用器在切换时会在时钟线上产生毛刺,从而危害整个系统。这些毛刺会被一些寄存器当成有效时钟边沿,而被另一些寄存器忽略。

Xilinx提供了能在两个全局时钟源之间进行复用的BUFGMUX原语。它还确保了当输人时钟切换后不会产生毛刺。时钟复用需要对复用器中所有从输入到输出的时钟路径进行细致的时序约束

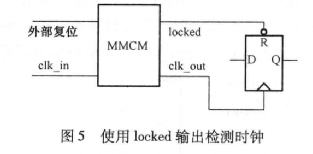

检测时钟缺失 (absence)的一种方法,是使用其他更高速的时钟对其进行过采样,缺点是时钟可能没有可用的高速时钟。还有一种方法是使用 Xilinx MMCM 原语的 locked 输出,如图 5 所示。

编辑:jq

-

FPGA

+关注

关注

1629文章

21729浏览量

602960 -

寄存器

+关注

关注

31文章

5336浏览量

120224 -

数据

+关注

关注

8文章

7002浏览量

88937 -

Xilinx

+关注

关注

71文章

2167浏览量

121290

原文标题:FPGA时钟设计方案

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

2024年ICPC与华为挑战赛冠军杯圆满落幕

边缘计算的技术挑战与解决方案

【智能生活新宠】:WTR096芯片语音时钟方案,录音播放+时钟提醒+计时时钟功能一体,一键掌控您的日常节奏

康谋分享 | 在基于场景的AD/ADAS验证过程中,识别挑战性场景!

FPGA设计面临的挑战和解决方案

使用STM8L做内部RTC做时钟,时钟计时计到了超过24时怎么解决?

EPSON 的 RX8010SJ 为安防产品提供高可靠性低功耗的实时时钟模块解决方案

单片机开发好学吗?学习中有哪些乐趣与挑战?

硬件工程师在可靠性设计中所面临的挑战及解决之道

时钟同步系统在网络通信中的重要性及优势

剖析具有挑战性的设计时钟方案

剖析具有挑战性的设计时钟方案

评论