1. 块语句有两种,一种是 begin-end 语句, 通常用来标志()执行的语句;一种是 fork-join 语句,通常用来标志()执行的语句。

答案:顺序,并行

解析:

(1)begin_end顺序块,用于将多条语句组成顺序块,语句按顺序一条一条执行(除了带有内嵌延迟控制的非阻塞赋值语句),每条语句的延迟时间是相对于由上一条语句的仿真时间而言;

(2)fork-join并行块,块内语句同时执行。

2. 块语句,下面这段语句中,第 40 时刻上,A、B 的值各是多少?

reg A;reg B;initial begin fork begin A = 1; #20 A = 0; #30 A = 1; #50 A = 0; end begin B = 1; #20 B = 0; #30 B = 1; #50 B = 0; end joinend

答案:A = 0,B = 0

解析:

块语句有两种,begin...end 和 fork...join,其中 fork...join 是并行块,begin...end 是顺序执行块,可以相互嵌套。

上面,两个 begin...end 之间是并行的,而各自 begin...end 内部是顺序执行,A 和 B 的赋值逻辑是一样的,所以要么都是 1,要么都是 0。

按照顺序执行,A 前 20 个时间单位是 1,然后持续 30 个时间单位的 0,所以 40 时刻是 0,同理 B 也是 0。

原文标题:Verilog 的块语句 fork...join 和 begin...end

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

Verilog

+关注

关注

28文章

1351浏览量

110074 -

语句表

+关注

关注

0文章

8浏览量

7210

原文标题:Verilog 的块语句 fork...join 和 begin...end

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

solidworks正版软件:永久版权和订阅许可 两种购买方式解析和选择

晶闸管的阻断状态有两种是什么

充电桩为什么有直流与交流两种接口?

verilog调用模块端口对应方式

verilog中repeat必须用begin和end吗

assign语句和always语句的用法

verilog中initial和always的区别

verilog中for循环是串行执行还是并行执行

verilog同步和异步的区别 verilog阻塞赋值和非阻塞赋值的区别

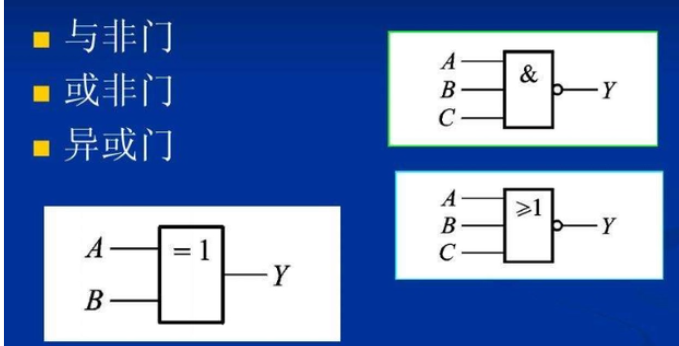

异或门两种常见的实现方式

Verilog的两种块语句解析

Verilog的两种块语句解析

评论