前言

随着5G、AI、航天等领域迅猛发展,高速信号处理需求日益突出,硬件加速势在必行。异构多核架构近年来得到业界广泛重视,一方面,CPU/GPU算力受限,无法应对高速海量数据实时计算;另一方面,以ASIC、FPGA为代表的硬件加速器具有并行计算优势,可实现高吞吐率、低时延处理,但操控灵活性尚有不足。因此,基于CPU/GPU+ASIC/FPGA的异构计算平台顺势推出,既能保证操控灵活性,又能保证高速低时延处理,可应对5G、AI、数据中心、航天等领域重大需求。

FPGA作为高度集成可编程芯片,在工业、通信、航天等行业得到广泛应用,FPGA工程师将致力于实现功能需求定制开发FPGA。如何进行FPGA开发,需要掌握哪些技术,是每一个FPGA工程师面临的首要问题。本系列文章基于高亚军老师的视频教程,结合Xilinx公司的Vivado集成开发环境,为大家讲解如何利用Vivado进行FPGA开发。

Xilinx FPGA/ Vivado开发教程

01

第一讲

Vivado设计流程及使用模式

注意,高老师在B站的视频教程给出了demo工程演示,本文就不做演示部分的内容说明,自己动手新建一个工程,进行实践。

在第一讲中,我们将了解Xilinx的ISE和Vivado设计套件的不同点,以及如何使用Vivado进行FPGA开发。

Vivado是ISE的升级版,可应用于7系列FPGA、ZYNQ、SOC等开发,功能更强大。

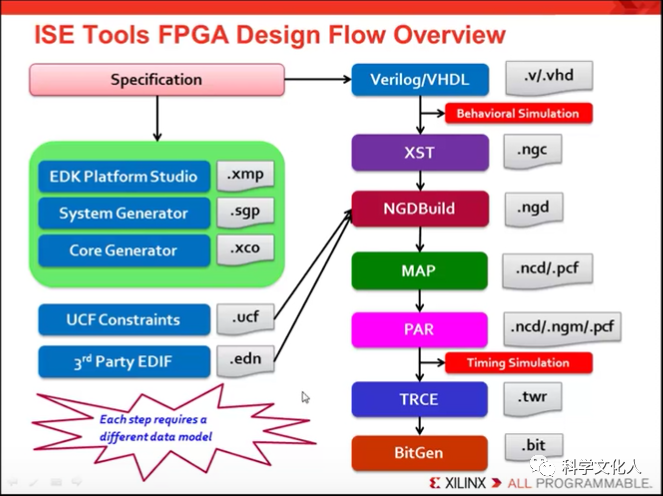

ISE工具FPGA设计流程:

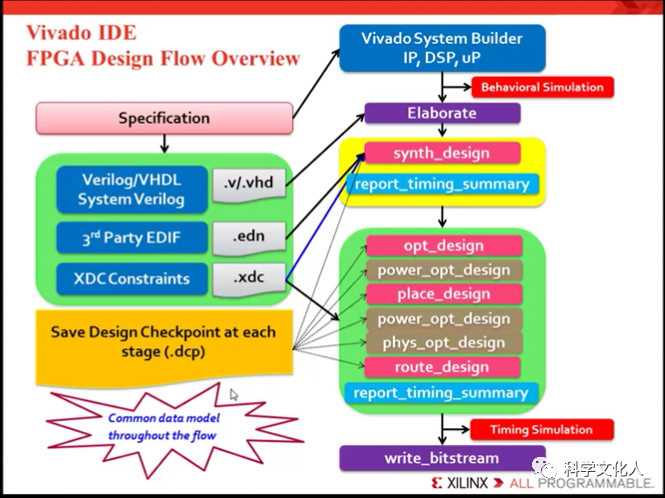

Vivado集成发开环境FPGA设计流程:

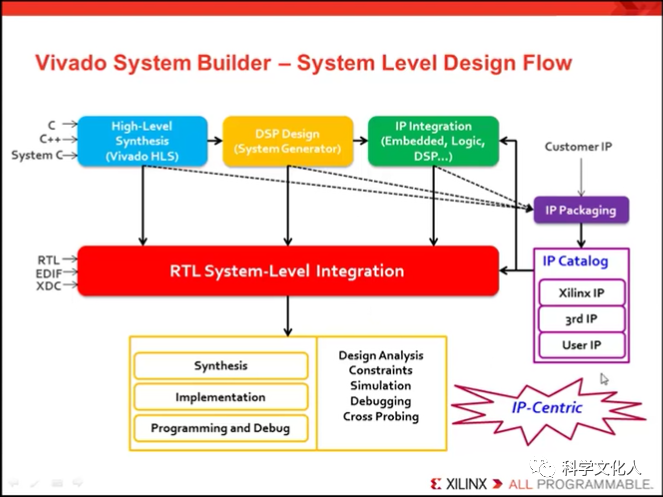

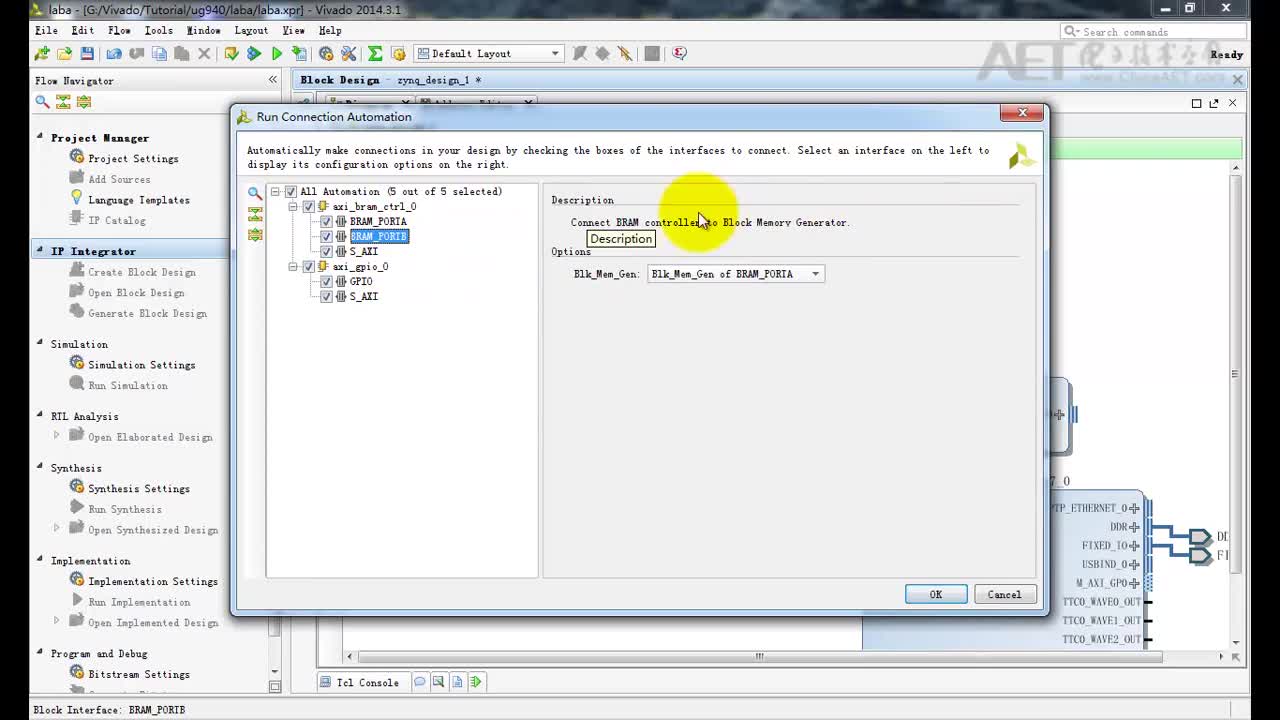

采用Vivado进行系统级设计时,IP模块是一个重要组成部分,不论是软核、硬核还是固核,或者自己用RTL逻辑开发的IP模块,在Vivado中可快速集成。

在开发过程中,设计分析(如时序、逻辑),约束文件(如I/O、时钟),仿真验证,综合与实现,在线debug(VIO、ILA)调试,更高一级技术要求,如方案与架构设计、资源与性能评估、系统算法,都需要工程师们掌握。

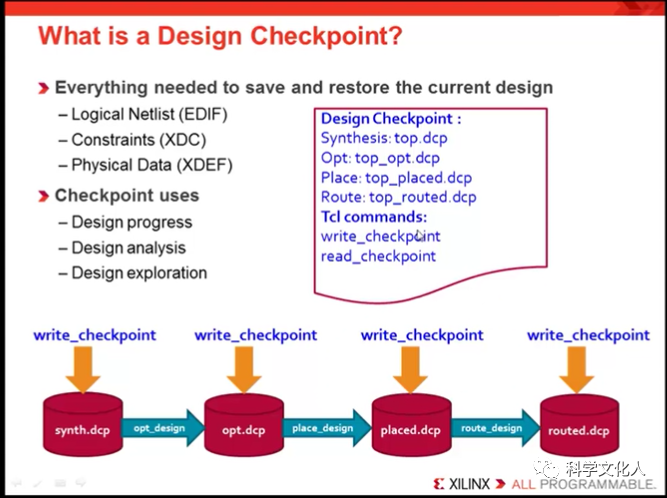

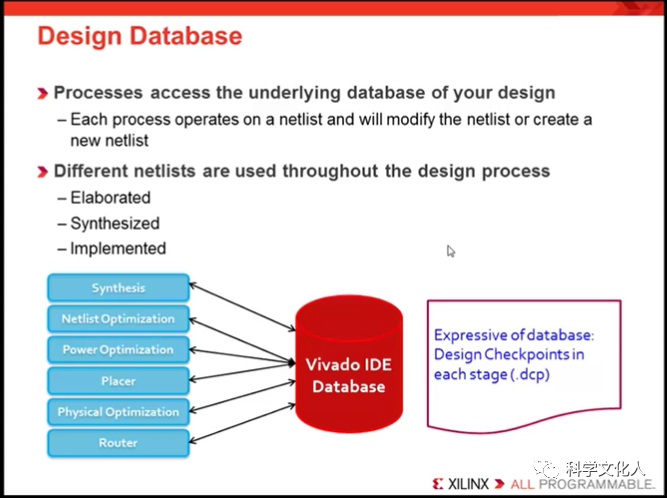

Vivado工具在设计的每个阶段,会生成对应的文件和网表,并进行相应的检查。

当新建一个工程后,工程文件夹包含整个工程的数据库,并进行设计更新。

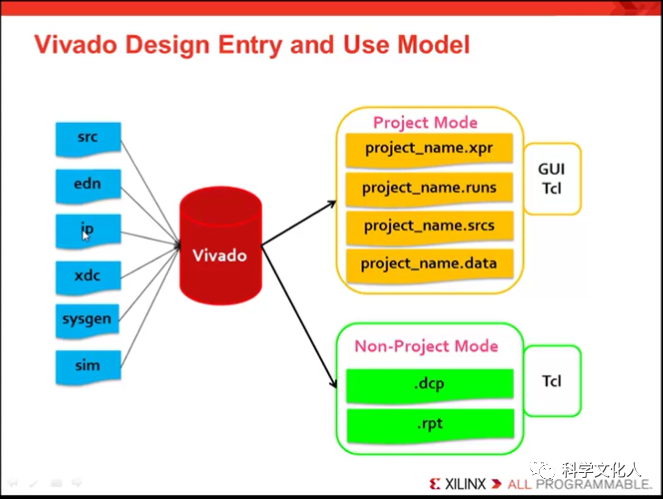

在利用Vivado进行设计时,使用模式有Project Mode和Non-Project Mode之分,我们常用的是Project Mode。

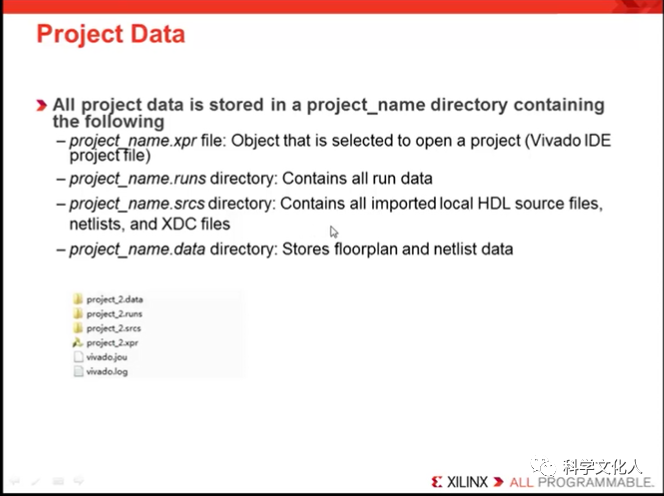

建立一个工程后,会将工程数据保存在工程文件夹下。

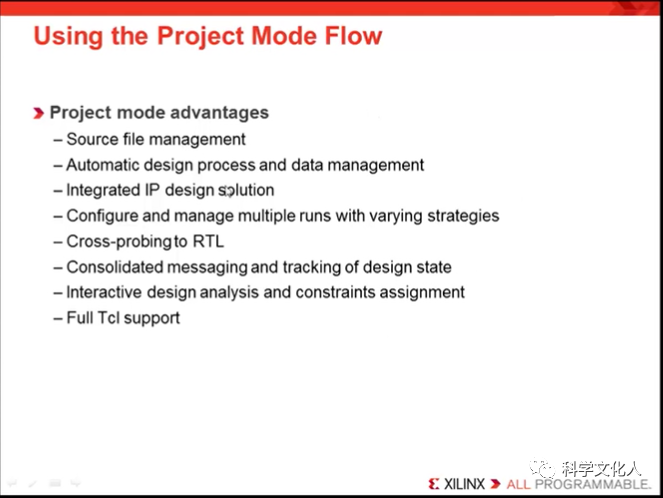

对于Project Mode,其特点为:

源文件管理、设计过程和数据管理、集成IP设计方案、配置和管理策略、RTL模块移植、设计分析和约束管理、支持TCL命令操作等等,一应俱全。

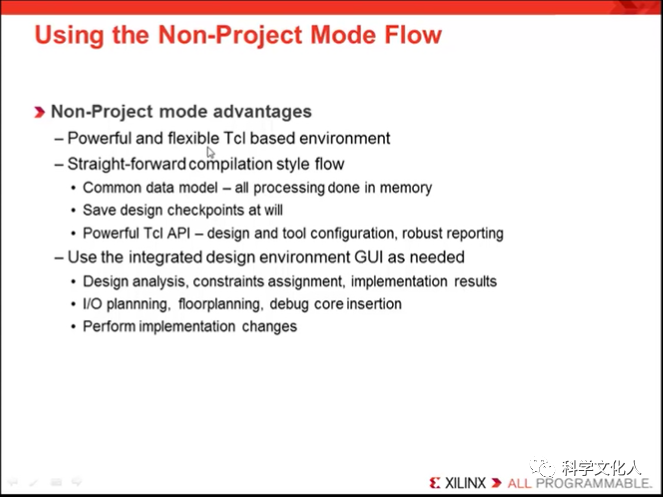

对于Non-Project Mode,其特点为:

该模式下,TCL用得多,感觉不是很适合做工程开发。

文章出处:【微信公众号:FPGA之家】

-

FPGA

+关注

关注

1629文章

21729浏览量

602960 -

芯片

+关注

关注

455文章

50714浏览量

423113 -

cpu

+关注

关注

68文章

10854浏览量

211567

原文标题:Xilinx FPGA/Vivado开发教程

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPGA开发Vivado的仿真设计案例分析

FPGA开发如何降低成本,比如利用免费的IP内核

#硬声创作季 #FPGA Xilinx开发-34 利用Vivado IP Integrator进行设计开发-1

#硬声创作季 #FPGA Xilinx开发-34 利用Vivado IP Integrator进行设计开发-2

Xilinx FPGA Vivado开发流程介绍

利用FPGA开发板进行ASIC原型开发的技巧

如何读懂FPGA开发过程中的Vivado时序报告?

如何利用Vivado集成开发环境进行FPGA的应用开发

如何利用Vivado集成开发环境进行FPGA的应用开发

评论