一、IC 定义

IC就是半导体元件产品的统称,IC按功能可分为:数字IC、vwin IC、微波IC及其他IC。数字IC就是传递、加工、处理数字信号的IC,是近年来应用最广、发展最快的IC品种,可分为通用数字IC和专用数字IC。

通用IC:是指那些用户多、使用领域广泛、标准型的电路,如存储器(DRAM)、微处理器(MPU)及微控制器(MCU)等,反映了数字IC的现状和水平。

专用IC(ASIC):是指为特定的用户、某种专门或特别的用途而设计的电路。

集成电路产品有以下几种设计、生产、销售模式。

1.IC制造商(IDM)自行设计,由自己的生产线加工、封装,测试后的成品芯片自行销售。

2.IC设计公司(Fabless)与标准工艺加工线(Foundry)相结合的方式。设计公司将所设计芯片最终的物理版图交给Foundry加工制造,同样,封装测试也委托专业厂家完成,最后的成品芯片作为IC设计公司的产品而自行销售。

二、芯片各个节点分工

全球晶圆片厂排名前五依次是 台积电(TSMC)、格罗方德、联电、三星、中芯国际(SMI).

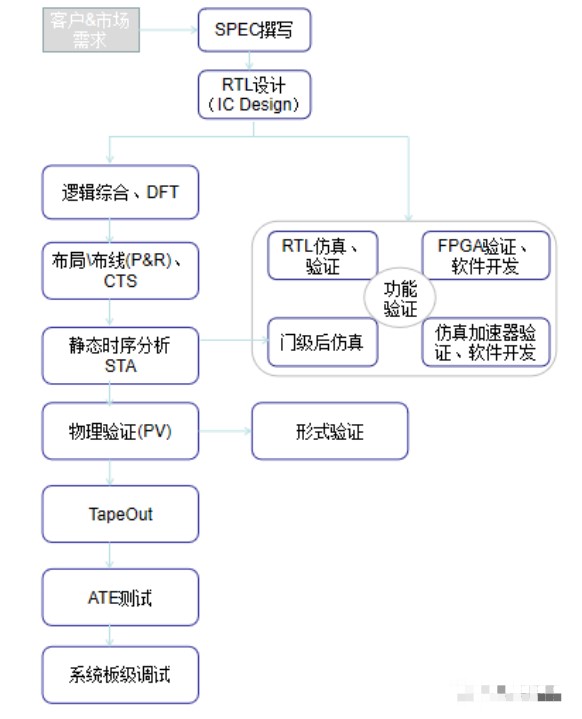

三、数字IC设计全流程

四、IC Design

前端设计 :

4.1 SPEC拟写

(1)工艺的选定 ;(2)详细feature描述 (3)模块划分、IP选型;

(4)架构规划 ;(5)时钟域、时钟结构规划;(6)电源域、低功耗规划

(7)地址空间分配;(7)IO选定与分配;

4.2 RTL 逻辑设计

使用硬件描述语言(VHDL,Verilog HDL,业界公司一般都是使用后者)将模块功能以代码来描述实现,也就是将实际的硬件电路功能通过HDL语言描述出来,形成RTL(寄存器传输级)代码。

前端逻辑设计时也需要注意PPA(Performance、Power、Area)性能、功耗、面积平衡。需要特别关注面积和速度互换原则(串并转换和并串转换、乒乓操作、流水线设计)和低功耗设计方法(门控时钟clock_gatinng、资源共享、采用独热码多路器)等等,做到这些才能算是比较好的设计。

涉及到代码检查,使用工具vcs/verdi 把一般的错误和警告消除掉,还有一些隐藏比较深的错误和警告就要使用spyglass 进行lint/cdc检查。

物理实现 :

4.3 逻辑综合、DFT

综合:仿真验证通过后,进行逻辑综合,一般由后端工程师完成,但是时序的迭代需要与前端工程师配合。需要的文件:RTL代码+约束文件+库文件(.db);使用的工具是Design Compiler。逻辑综合的结果就是把设计实现的HDL代码翻译成门级网表netlist。

DFT:Design For Test 可测试性设计,一般由前端工程师集成DFT逻辑。DFT通过插入 DFT 逻辑,比如Scan Chain(寄存器)、MBist(片上存储器)、Boundary Scan(IO)等,然后利用 ATPG、MBist、Boundary Scan 工具产生测试向量,仿真验证测试向量。目的为了检测到芯片量产过程中出现的带有各种制造缺陷的片子,从而为顾客提供性能更稳定的产品,降低DPPM(每百万芯片缺陷数量),从而为公司产品保证良好的口碑。

4.4 布局&布线、CTS

布局规划(Floorplan)直接影响芯片的面积,布线需要考虑拥塞情况,而且由于线延时的存在,在PR时一般时序比单纯逻辑综合要差一些。

CTS :clock tree synthesis 时钟树综合,目的是要时钟到各个寄存器单元延时差异最小。

4.5 静态时序分析(STA)

主要是通过检查建立时间和保持时间是否满足要求,其目的是通过遍历所有的传输路径,寻找所有的组合逻辑电路的最坏延迟情况(以及毛刺、时钟偏差等等),也被称为关键路径。涉及到的时序分析路径有:寄存器到寄存器:Reg2Reg;寄存器到输出引脚:Reg2Pin;

输入引脚到寄存器:Pin2Reg;输入引脚到输出引脚:Pin2Pin. 此外,在芯片设计中我们还会经常见到reg2mem和mem2reg 时序违例报告。

时序分析只能验证同步时序电路的时序特性,不能自动识别设计中的特殊路径,如多周期路径(Multi-Cycle Path)、非正常路径(False Path)、多时钟分配(Multiple Path)。如果设计中含有较多的异步电路,我们一般把异步路径设置为max_delay进行约束。

4.6 形式验证

它是从功能上(STA是时序上)对综合后的网表进行验证。常用的就是等价性检查方法,以功能验证后的HDL设计为参考,对比综合后的网表功能,他们是否在功能上存在等价性。这样做是为了保证在逻辑综合过程中没有改变原先HDL描述的电路功能。形式验证工具有Synopsys的Formality。

4.7 TapeOut

在流片之前,为提高良率和解决物理规则违规还要做些DRC/LVS的工作;芯片设计阶段完成之后,把输出的物理版图GDS文件->芯片代工厂->晶体硅->做出实际电路->封装和测试->芯片。

功能验证:

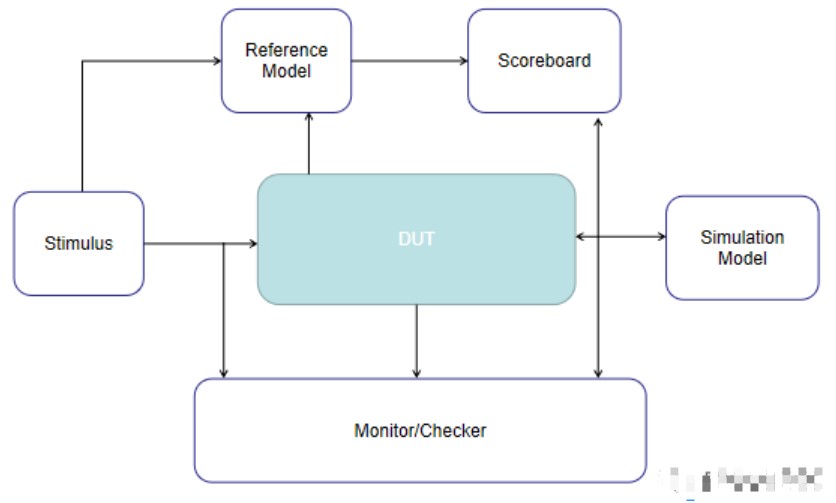

4.8 验证环境

如下图所示,其中,Scoreboard主要用于比较reference model与DUT输出是否一致,并给出比较结果Reference model和DUT是对SPEC的两个独立的实现。当ref model和DUT行为不一致时,或者dut错,或者ref model错,或者两者都错,debug就好。Stimulus激励,需覆盖DUT不同的工作场景以及可能出现的异常情况。Monitor 做一些中间状态监控或者计数。

4.9 验证方式

验证方式包含两种:白盒验证和黑盒验证

白盒指的是验证对象(DUT)的内部结构是完全可见的,我们可以清楚的看到设计的详细内容,白盒验证的好处是我们可以了解设计者的意图,并且验证可以达到设计上的每一点,但这需要花费更长的时间。

灰盒指的是验证对象(DUT)的内部结构,只有一部分是可见的,黑盒验证则DUT内部完全不可见,我们只能看到设计的输入接口和输出接口,对黑盒验证,我们只能通过了解其设计文档来了解它的功能。

4.10 验证语言和验证方法学

验证语言:Verilog 、SystemVerilog、Assertion、SystemC、Perl、Makefile

验证方法学 :UVM 、OVM、VMM

4.11 验证覆盖率

代码覆盖率(Code Coverage):Line coverage /Condition coverage 、

Branch coverage /Toggle coverage /FSM coverage

功能覆盖率(Function Coverage):uassertion

4.12 后仿真

• 门级延迟

– Sdf延迟文件加载

– 与RTL不一致

• X 态传播

– 异步时序电路产生X态

– 增加debug难度

– 控制X态传播

• PG网表门级仿真

– 低功耗仿真

4.13 FPGA验证

ASIC 代码移植

– PLL/IO/MEM/STDCELL替换

– 时钟产生逻辑去除

– 时钟频率、时钟关系调整

– 设计裁剪partition

• 代码FPGA实现

– 时序约束

– 时序检查

• FPGA调试、验证

4.14 仿真加速器验证

Cadence – Palladium

– CPU based

• Synopsys – ZeBu

– FPGA based

• Mentor – Veloce

– FPGA based

4.15 验证方式比较

一般在代码开发过程中,以下验证方式一般是逐级递进的,后期同时进行回归验证,由于FPGA验证和仿真加速器都是降频模式下验证下,一些时序问题也是验证不出来的。但是两者好处在于仿真速度快,容易验出一些在长时间运行累积的错误,因此,一般需要长时间拷机测试。

责任编辑:lq6

-

集成电路

+关注

关注

5387文章

11530浏览量

361607 -

IC

+关注

关注

36文章

5944浏览量

175468 -

数字IC

+关注

关注

1文章

38浏览量

12545

原文标题:数字IC设计知识结构

文章出处:【微信号:FPGA_Study,微信公众号:FPGA自习室】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

瑞萨电子面向不断增长的 IO-link 市场推出四通道主控 IC 和传感器信号调节器

【「数字IC设计入门」阅读体验】+ 数字IC设计流程

【「数字IC设计入门」阅读体验】+ 概观

JK触发器是一种什么稳态电路

数字滤波器的实现方法

S1D15K01是一种混合LCD驱动器IC

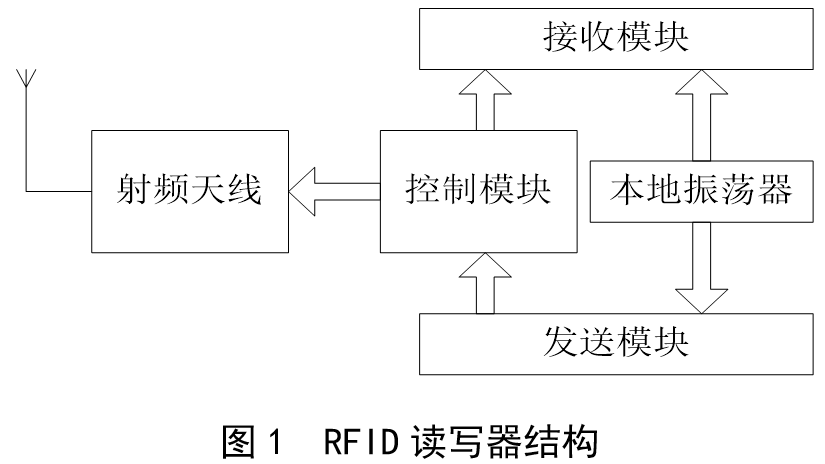

一种用于RFID读写器的数字鉴相器设计

一种供电总线技术POWERBUS二总线

rup是一种什么模型

plc是一种什么的电子装置

fpga和数字ic区别 fpga和plc区别

一种数字delayline的设计方案

如何去实现一种数字IC的设计?

如何去实现一种数字IC的设计?

评论